半导体的黄金时代全面开启,摩尔定律成为行业领先技术的衡量指标

半导体集成电路是现代信息产业的基石。1947年12月,美国贝尔实验室的肖克利、巴丁和布拉顿组成的研究小组,研制出世界上第一只锗晶体管,结束了笨重的电子管时代。60年代以后,硅晶体管开始全面取代锗晶体管,从此半导体的黄金时代全面开启。

1965年,英特尔的创始人之一戈登·摩尔发布了集成电路行业最知名的定律:“每隔18个月,同样面积内晶体管数量翻倍,但是价格不变。”这就是后来被称为“集成电路的指数级增长”的摩尔定律。60多年来,晶体管数量的增长得益于制程工艺的创新,与摩尔定律一直保持着“默契”。芯片沿着摩尔定律不断微缩,0.5 u、0.35 u、0.25 u、0.18 u、0.13 u、90 nm、65 nm、45 nm、28 nm、14 nm,直到现在的7 nm、5 nm,甚至到主流制程工艺接近2 nm、1 nm,芯片的尺寸越来越小,性能应用越来越先进。例如,在摩尔定律的指导下,英特尔1971年对外公布了世界第一个微处理器4004,宣告了“一个集成电子新纪元已经来临”。1974年,又推出了微处理器8080。“8080”被当时业内人士称赞为有史以来最成功的微处理器之一,也正是从8080开始,个人电脑开始在全世界范围内流行起来……。俨然,摩尔定律已成为半导体企业保持技术领先的衡量指标:保持摩尔定律企业就能生存,不能保持摩尔定律企业就会在竞争中被淘汰。

摩尔定律正遭遇技术与成本两大发展瓶颈

随着人工智能、物联网、超级计算等时代的到来,对半导体材料与器件提出了更高的性能要求,半导体产业即将步入亟需转变突破发展的关键点。单纯依靠缩小尺寸的做法正走向穷途末路。当前,硅晶体管随着技术节点的迭代缩减,特别是尺寸突破到10 nm以下时,晶体管性能会变得很不稳定。不过,摩尔定律总能抓住一些“救命稻草”。在90 nm时代,应变硅技术问世。在45纳米时代,一种能提高晶体管电容的新材料推出。在22 nm时代,三栅极晶体管使芯片性能变得更强大。

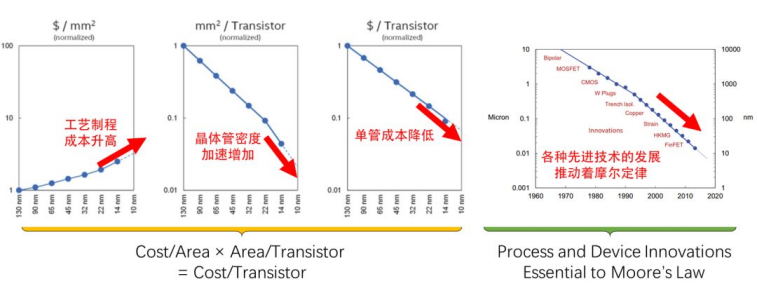

但随着特征尺寸越来越接近宏观物理和量子物理的边界,现在高级工艺制程的研发越来越困难,研发成本也越来越高,尤其是摩尔定律发展到特征尺寸5纳米节点以下,继续简单粗暴地缩小特征尺寸会变得很困难,并且芯片的成本指数增加。据IBS统计,28 nm芯片的设计成本在4000万美元,16 nm芯片设计成本约1亿美元,而5 nm芯片的设计成本更高达5.4亿美元。再继续发展下去,先进工艺的投入产出比已难以具备商业合理性,同时受制于光刻尺寸及晶圆厂良率,单芯片的面积也很难继续延伸,未来芯片设计的成本将直接“劝退”中小厂商,甚至大厂也需要摸一下自己的口袋。这也部分地打破了摩尔定律“投资发展制程——芯片生产成本降低——用部分利润继续投资发展制程”的逻辑。也就是说,传统的硅基电子技术临近生命周期极限,摩尔定律正遭遇技术与成本两大发展瓶颈。

如何延续摩尔定律?

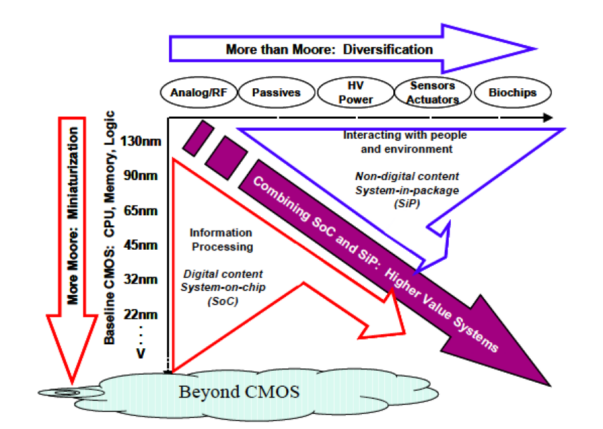

如何延续摩尔定律,实际上不仅是技术问题也是经济问题。鉴于应用的多元化与复杂程度的提高,微电子技术演进不再仅限于半导体CMOS工艺本身,半导体产业生态系统也在持续扩大。后摩尔时代电子技术的核心需求主要分成三个方向:即more Moore、morethan Moore和beyond Moore或beyond CMOS。这也是后摩尔时代全球半导体技术发展的三个主流路线。目前行业给出几种可能的方案:包括大热门的chiplet/3D封装,新兴器件技术(自旋器件/量子)和新兴架构(量子计算/神经形态计算)等。

后摩尔时代三大技术路线

实际上,早在2005年,ITRS委员会首次明确指出:在2020年前后,硅基CMOS技术将达到其性能极限。以2020年作为时间节点,来自工业界和学术界的研究人员都在积极寻找硅的替代技术。然而,当时可供选择的名单并不多。

2007年,ITRS委员会认识到发展新型纳米器件的紧迫性。为了制定更详尽的半导体技术路线图,要求新兴研究材料工作组(ERM)和新兴研究器件工作组(ERD)推荐一两种最有前景的新兴材料和器件技术。在对所有的硅基CMOS替代技术——包括纳电子机械开关,集体自旋器件,自旋矩转移器件,原子开关,单电子晶体管,碳基纳电子学等进行考察、评估之后,工作组明确推荐碳基纳电子学(包括碳纳米管和石墨烯)作为可能在未来5~10年显现商业价值的下一代电子技术。

2009年,路线图委员会(IRC)支持ERD/ERM工作小组选择碳基纳米电子学作为需要重点关注和投资的技术,用以加速半导体电子产业的发展。

ITRS在2014年正式宣布迈入2.0版,除了将系统整合、异质整合概念纳入,也将2005年首度提出的“More Moore”(即持续以工艺微缩延续摩尔定律生命)、”Moore than Moore”(CMOS工艺之外其他多样化组件如传感器、微机电系统、光电组件以及生物芯片的技术发展)列为讨论重点,还有对”Beyond CMOS”,也就是并非以MOS晶体管为基础的新组件技术探索,像是自旋电子与磁性组件。

在2016年,”国际组件暨系统技术蓝图”(International Roadmap for Devices and Systems,IRDS)在IEEE的赞助下启动,并于2017年推出首版IRDS白皮书。

做为ITRS的后继,IRDS同样以15年为一个时间跨度,定义通用组件与系统的需求、挑战、潜在解决方案以及创新机会,原则上是每两年更新一版(或依据实际情况也可能每年更新)。如同IEEE在IRDS官网所明示,技术蓝图从ITRS到IRDS的转变与演进,代表将技术发展焦点更集中于系统,并且关注跳脱传统组件、电路、逻辑闸、功能区块与系统典范的架构与应用。目前IRDS已经更新至2020年版,共有13个IFT,分别为:(1)应用基准(Application Benchmarking,AB);(2)系统与架构(Systems and Architectures,SA);(3)系统外部链接(Outside Systems Connectivity,OSC);(4)后摩尔定律技术(More Moore,MM);(5)超越摩尔定律(More than Moore,MtM);(6)微影技术(Lithography,L);(7)封装整合(Packaging Integration,PI);(8)良率提升(Yield Enhancement,YE);(9)度量(Metrology,M);(10)工厂整合(Factory Integration,FI);(11)超越CMOS(Beyond CMOS,BC);(12)低温电子与量子信息处理(Cryogenic Electronics and Quantum Information Processing,CEQIP);(13)环境、安全、健康与永续性(Environment, Safety, Health, and Sustainability,ESH/S)。

从IRDS可以看出,半导体技术的发展脉络与未来方向不仅会受到IoT、AI、5G等等新兴应用的系统架构影响,摩尔定律的延续不再只靠CMOS工艺微缩挑大梁,先进封装技术为芯片整合带来了全新的视野;而业界已经开始着眼于CMOS之外的技术发展方向,我们可以期待在将来出现打破现有规则与组件结构的颠覆性成果。

我国同样也在着重布局。2021年5月14日,国家科技体制改革和创新体系建设领导小组第十八次会议在北京召开。此次会议专题讨论了面向后摩尔时代的集成电路潜在颠覆性技术。

1、“More Moore”延续摩尔定律:以晶体管结构变革为特点

所谓“More Moore”,这是一个延续CMOS的整体思路方法。简单来说,“More Moore”,即“延续摩尔”,是指延续摩尔定律的发展思路,缩小集成电路特征尺寸,同时兼顾性能及功耗。具体而言就是在器件结构、沟道材料、连接导线、高介质金属栅、架构系统、制造工艺等等方面进行创新研发,沿着摩尔定律一路微缩。在130 nm节点出现之前,晶体管遵循着Dennard scaling,其中等效氧化物厚度(EOT)、晶体管栅极长度(Lg)和晶体管宽度(W)均采用常数因子进行微缩,以便在恒定功率密度下提供延迟改善。英特尔的William M. Holt在2016年的国际固态电路年度会议ISSCC上谈到(William M. Holt, ISSCC,Moore’s Law: A Path Going Forward, 2016),在延续摩尔这一条道路上,对晶体管的优化的重头在于减小漏电,降低功耗。对功耗降低的需求驱动着工艺制程的不断演进。

目前,为了维持低电压下的定标,近年来的定标主要集中在提高性能的其他解决方案上,如在沟道中引入应变、应力助推器、high-κ金属栅、降低接触电阻和改善静电。所有这些都是为了补偿栅极驱动损耗的同时,还满足高性能移动应用所需要的低电源电压。

逻辑技术(Logic technologies)、基本规则缩放(Ground rule scaling)、性能助推器(Performance boosters)、性能-功率-尺寸(PPA)缩放(Performance-power-area (PPA) scaling)、3D集成(3D integration)、内存技术(Memory technologies)、DRAM技术(DRAM technologies)、Flash技术(Flash technologies)、新兴的非易失性内存(NVM)技术(Emerging non-volatile-memory (NVM) technologies)等技术的突破也是驱动其发展的重要因素。

其实,大部分的半导体器件都是数字逻辑,就需要去支持两种器件类型的技术平台:(1)高性能逻辑;(2)低功耗/高密度逻辑。该技术平台的关键考虑因素是速度、功耗、密度和成本。More Moore路线图为MOSFET的持续扩展提供了一个参考,以保持以更低的功耗和成本改进设备性能的历史趋势。

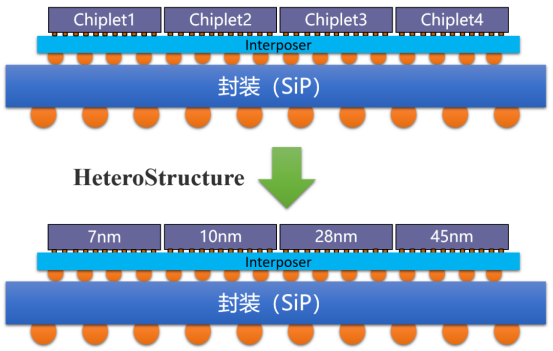

2、“More than Moore”超越摩尔定律:以先进封装技术变革为特点

所谓的More than Moore,即“扩展摩尔”,是指依靠电路设计以及系统算法优化,同时通过先进封装技术实现异质集成(heterogeneous integration),以此提升集成电路性能。也就是说,以系统应用的概念为出发点,不执着在晶体管的制程点缩小的摩尔定律,而更应该将各种技术进行异质整合,以先进封装技术变革为特点。先进封装技术能进一步提高芯片的集成度并且降低芯片制造的成本,同时暂不涉及到去突破量子隧穿效应等物理极限问题,已经成为超越摩尔定律的关键赛道。

不同于“More Moore”不断对晶体管的优化,More than Moore是应用需求驱动的,侧重于实现多样化的功能。摩尔定律在数字世界统治的同时只是在整个版图里占据一部分位置,在其余的部分里,并不是单纯的把晶体管当开关来实现0和1。相对于数字世界,真实的物理世界(模拟领域)发展并没有受到很好的关注。许多模拟应用领域,例如射频器件(RF devices)、电源管理子系统、无源器件、生物芯片、传感器、微机电系统MEMS等等,在现今的半导体产品里扮演同样重要的角色。将上述现成的技术元素集成进基于CMOS的芯片中去,形成一个异构的系统,可以让系统价值倍增,让成本进一步优化,性能进一步提高。这种将现有模拟技术元素集成进CMOS芯片,形成一种异构芯片,从而扩展CMOS芯片功能范围的发展就是More than Moore。

目前,先进封装应用不断扩大,预计在2026年将占到整个封装市场的规模的50%以上。先进封装技术与传统封装技术通常以是否焊线来区分:传统的封装技术通常指先将晶圆切割成单个芯片,再进行封装的工艺形式,其包括双排直立式封装DIP与球格阵列封装BGA,需要焊接线路;先进封装则包括倒装(FlipChip)、凸块(Bumping)、晶圆级封装(Wafer-level-package)、2.5D封装(interposer,RDL等)、3D封装(TSV)等封装技术,其技术并不需要用到线路焊接的方式。

就连大火的Chiplet实现的前提也是先进封装。Chiplet也称芯粒,简单来说Chiplet模式是在摩尔定律趋缓下的半导体工艺发展方向之一,是对原本复杂的SoC芯片的解构,将满足不同功能芯片裸片通过Die-to-Die内部互连技术与底层基础芯片封装组合的拼搭,在某种意义上也是不同IP的拼搭,像拼接乐高积木一样,用封装技术整合在一起,最后集成为一个系统级芯片,借此可以实现对先进制程迭代的弯道超车,在提升性能的同时实现低成本和高良率。实际上,Chiplet的出现则是给了整个行业一个新的思路,Chiplet技术可以将大型7 nm设计的成本降低25%,5 nm及以下的制程节省的成本更多,基于Chiplet架构的芯片设计理念也逐步成为后摩尔时代提升芯片性能及算力的共识。

目前,AMD、台积电、英特尔、英伟达等芯片巨头近年来纷纷布局Chiplet,AMD最新几代产品都极大受益于“SiP+Chiplet”的异构系统集成模式,近日苹果最新发布的M1Ultra芯片也通过定制的UltraFusion封装架构实现了超强的性能和功能水平,包括2.5TB/s的处理器间带宽。据Omdia报告,预计到2024年,Chiplet市场规模将达58亿美元,2035年则超过570亿美元,将迎来快速增长。

然而,Chiplet对先进封装提出更高要求。在芯片小型化的设计过程中,需要添加更多I/O来与其他芯片接口,裸片尺寸有必要保持较大且留有空白空间,导致部分芯片无法拆分,芯片尺寸小型化的上限被pad(晶片的管脚)限制,并且单个晶片上的布线密度和信号传输质量远高于Chiplet之间,要实现Chiplet的信号传输,就要求发展出高密度、大带宽布线的“先进封装技术”。

3、“Beyond CMOS”超越摩尔:以半导体材料变革为特点

前面说到的延续摩尔和超越摩尔都是基于Si MOSFET的发展方向。延续摩尔继续缩小尺寸,但重心转向功耗优化。超越摩尔则把重心放在电路设计、先进封装和算法优化层面。相对于上述两个方向,第三个IRDS提出的方向就是Beyond CMOS。

因为,无论是透过”由上而下”或”由下而上”的创新延续CMOS工艺的微缩,此类技术仍然会达到再难以打破的物理屏障,特别是到了1纳米以下节点,打破现有组件架构、工艺与材料”典范”(paradigm)势在必行。此外随着全新运算典范,以及大数据分析、IoT、AI、自驾车、超大规模运算等等应用,带来对电子组件的更高性能与效率需求。这就需要跳脱CMOS工艺另辟蹊径。

“Beyond CMOS”,即“超越摩尔”,是指使用CMOS以外的新器件提升集成电路性能,这涉及半导体新材料的采用。按照这个演进路线,后摩尔时代的产业发展将同时拥抱“新制程”、“新架构”与“新材料”,以实现产业的继续迭代升级。

IRDS针对”超越CMOS”路线列出了五个关注项目:(1)新兴内存组件(emerging memory devices);(2)新兴逻辑与替代性信息处理组件(emerging logic and alternative information processing devices);(3)新兴组件-架构互动(emerging device-architecture interaction);(4)支持后摩尔定律应用的超越CMOS组件(beyond-CMOS devices for More-than-Moore applications);(5)新兴材料整合(emerging materials integration)。这些项目包含了具备长期潜力与一定技术成熟度的新兴组件与运算架构,并为它们定义出进一步被产业采用所需克服的科学与技术挑战(可接受的风险)。其中有一部分可通过异质整合拓展现有CMOS平台功能性的新技术,另一部分则是新信息处理典范,例如模拟运算、量子运算、随机运算等等激发的全新组件技术。

其中,新兴内存、自旋电子、磁性电子,以及可替代硅的新材料(如碳纳米管、纳米线、纳米薄片、2D材料、超导体……大多数都是仍在初期阶段的前瞻性研究,却有可能成为未来主宰电子系统的技术。这也是延续自ITRS 2.0的BC小组所关注的是非CMOS组件技术的发展的主流路线。

尽管众多这类”超越CMOS”的研发,从走出实验室到产业化还有很长的一段距离需要努力,但目前已经有了些突破。

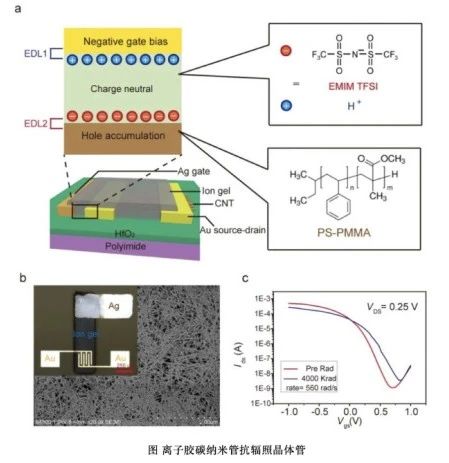

例如,在众多新型半导体材料中,碳纳米管(Carbon-Nanotube,碳管或CNT)由于其独特的准一维结构和优异的电学性质而受到了人们的高度重视。在碳基芯片的研发中,这场科技追逐战主要在两个世界顶级名校之间展开——北京大学(联合中科院)和麻省理工学院。在《自然》、《科学》杂志上出现的多篇碳晶体管的论文也多由这二者发布。2017年,北京大学在5nm栅极碳纳米管CMOS器件的工作就证明了碳纳米管在达到理论极限时可以克服短沟道效应,这就使其不必使用如硅技术那样发展更复杂的三维晶体管技术,例如FinFET,来降低短沟道效应。另外,碳纳米管技术本身是一个低温技术,可以制备三维的芯片。2020年,该团队登上全球顶级学术期刊《自然·电子学》,研发出一种可“抗辐射”的碳纳米管晶体管和集成电路、可用于航天航空、核工业等有较强辐照的特殊应用场景。此项研究成果意味着我国碳基半导体研究成功突破抗辐照这一世界性难题,为研制抗辐照的碳基芯片打下了坚实基础。彭练矛院士也表示,与国外硅基芯片相比,中国在处理大规模数据时所采用的国产碳基芯片速度快,功耗低,至少可节省三成。

另外,北京大学、北京石墨烯研究院的刘忠范与孙靖宇教授在对非金属基石墨烯晶圆CVD制备的研究上,发明了一种基于传热和气体流动性质原理的石墨烯晶圆批量化制备方法,每一批次可以生产出30片4英寸的石墨烯晶圆。中科院上海微系统所实现国产8英寸石墨烯晶圆小批量生产……目前,国内石墨烯晶圆生产技术无论在石墨烯单晶晶圆的尺寸和质量上,均处于国际领先水平。可见,中国在碳基芯片研发中已具有优势。

另外,二维材料同样引起业界关注。传统的硅基半导体和二维半导体之间的最大区别在于它们的几何形状。二维半导体要薄得多,只有几个原子层厚。这在许多方面都是有利的,因为使半导体更小的推动力不断增强。将二维材料集成到传统的半导体制造工艺中可能是芯片行业历史上更激进的变化之一。虽然在半导体制造中引入任何新材料都会带来痛苦和痛苦,但过渡金属二硫化物 (TMD:transition metal dichalcogenides)支持各种新的器件概念,包括BEOL晶体管和单晶体管逻辑栅极。新的背栅(back-gate)和分栅(split-gate)晶体管已经显示出二维设计的前景。

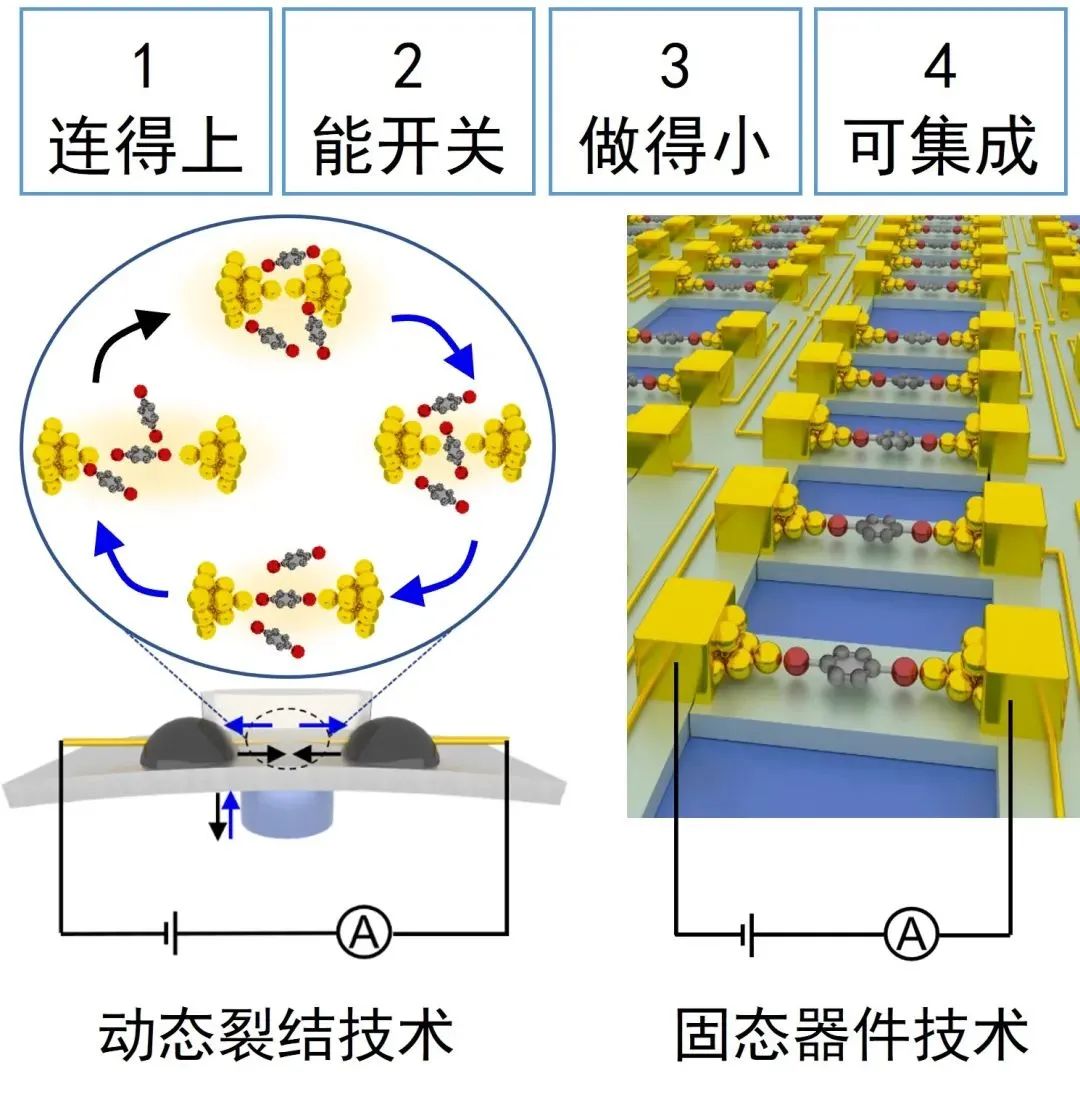

例如,厦门大学洪文晶教授课题组发展了基于π-π相互作用的原子级精度全碳电子器件构筑策略,为制造超分子电子器件,推动电子器件小型化,及在分子水平理解分子间电子输运过程提供了一种新的研究途径。

新竹阳明交通大学电子物理系教授张文豪以及台积电(TSMC)研发人员,在2020年曾共同发表在单原子厚度二维材料(2D material)的研发成果,实现以大面积晶圆尺寸生长单晶氮化硼(h-BN)的技术,会是未来CMOS工艺走向终结之后,搭配石墨烯、二硫化钼(MoS2)等硅替代材料作为绝缘层的理想选择。

中国台湾大学化学系教授陈俊显与台东大学应用科学系教授陈以文,发表了在单分子电子学(Single-molecule Electronics)领域的最新研发成果,提出采用双金属电极(bimetallic electrodes)的架构,相较于采用单一金属元素的电极,电极表面与分子之间的能阶匹配效果提升了30%~80%;这为未来实现单分子电子组件的理想迈进了一步。

……

目前,针对CMOS工艺的微缩技术的创新和延续,业界做了大量努力,但业界期望最大的还是材料的突破,就像当年的硅材料横空出世改变世界一样。这恰恰也是我国的机遇。相比“新制程”、“新架构”而言,中国在半导体新材料领域追赶主流、保持齐头并进,存在更大可能性。后摩尔时代,碳基半导体、二维半导体、第三、四代半导体或将成为我国重塑全球集成电路产业格局的关键机会点。产学合作的研发成果,或许会成为加速让这些新兴技术迈入商业化阶段的关键。不同代际的半导体材料,也将实现了技术与应用互补。半导体技术的世代交替已经隐隐在望,那么谁将会主宰后摩尔时代的技术走向呢?我们将拭目以待!

3022

3022

-1-%E5%89%AF%E6%9C%AC.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[下载]LAT1482 STM32G0单线串口通信帧错误问题解析

[下载]LAT1482 STM32G0单线串口通信帧错误问题解析