几十年来,英特尔等集成电路(IC)供应商都会设计一种将所有功能集成在同一片芯上的芯片,然而,随着行业看到摩尔定律的放缓(芯片密度不再每两年翻一番),扩展单片IC变得越来越困难和昂贵。这促使IC供应商转向了“先进半导体封装”。因此,先进封装已被誉为下一代IC的关键基础。

目前,应用先进封装的领域不胜枚举,人工智能(AI)、高性能计算、数据中心、自动驾驶汽车、5G都有它身影。而一些以技术见长的头部玩家更是对先进封装情有独钟,纷纷下场一显身手。

什么是先进半导体封装?

半导体封装已经存在了几十年,第一批量产产品出现在20世纪70年代初。说实话,尽管封装形式多种多样,但万变不离其宗,都是为了保护其中的芯。

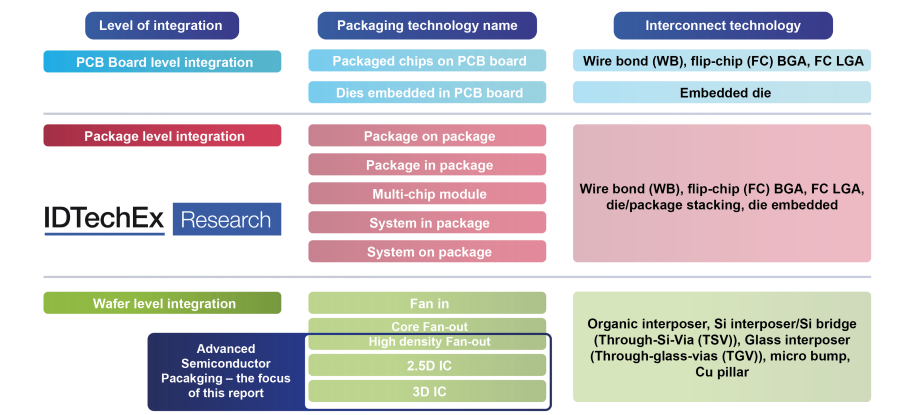

半导体封装技术——集成、封装与互连

一般来说,封装是制造半导体器件的最后两个步骤——封测——之一,然后还要对器件进行测试。先进封装的出现使这两个步骤出现了分离,笔者认为,封装变得更加独立了,功能上已突破了原来的保护作用。

以IC封装过程为例,首先要将IC裸片封装在具有电触点的支撑壳中。通过这种方式,用外壳保护IC裸片免受物理损伤和腐蚀的影响,同时将IC与PCB板上的其他器件连接在一起。

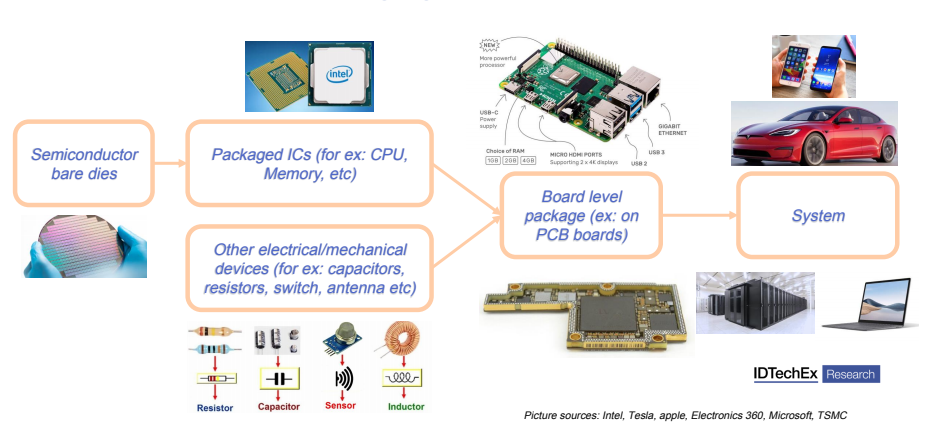

通用电子封装有四个流程:一是半导体裸片;二是封装IC(例如:CPU、内存等),以及其他电气/机械装置(例如:电容器、电阻器、开关、天线等);三是板级封装(例如:在PCB板上);四是最终的系统。

通用电子封装

如前所述,由于摩尔定律的放缓和单片IC制造成本的显著增加,IC供应商需要新的方法来设计能够实现高性能并同时保持成本效益的处理器。一种被称为“小芯片(chiplet)”的新设计登上了舞台,并日渐成为未来的关键趋势。

小芯片的背后

人们发明小芯片的想法是想将单片IC“拆分”为多个功能块,将功能块重组为单独的小芯片,然后在封装级别“重新组装”这些小芯片。理想情况下,基于小芯片设计的处理器应该具有与单片IC相同或更高的性能,但总的生产成本更低。

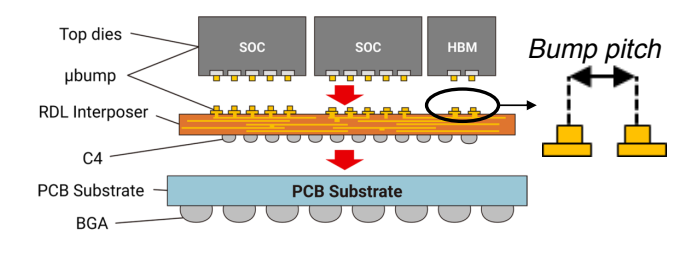

而封装方法,特别是用于连接多个小芯片的封装方法将会影响整个系统的性能,因此在小芯片设计中发挥着至关重要的作用。这些封装技术包括2.5D IC、3D IC和高密度扇出晶圆级封装等,都被归类为“先进半导体封装”。它们可以在单个基板上的不同工艺节点处合并多个小芯片,并且具有很小的凸点尺寸,能够实现更高的互连密度和更高的集成能力。

凸点大小的意义

1965年发明了第一个半导体封装,此后封装技术不断发展。现在,封装技术多种多样,从最广泛使用的引线键合到最先进的3D IC。

哪些技术被归类为先进半导体封装呢?一种分类方法是根据凸点间距大小。较小的凸点间距尺寸意味着更多的I/O数和更高的互连密度,这是许多高计算应用所需要的特性。不同公司提供不同的封装技术,包括3D混合键合、3D微凸点、2.5D嵌入式硅桥、2.5D全硅中介层、2.5D扇出(有机中介层)、倒装芯片、扇入等,不一而足。其最小凸点间距不尽相同,通常,将先进半导体封装定义为凸点尺寸小于100µm的任何封装。

I/O随着凸点大小的减小而增加,例如:10µm凸点尺寸封装技术可以提供大约400倍于200µm凸点尺寸封装技术的I/O数。

台积电开发的CoWoS(带硅中介层的基板上晶圆芯片)

所谓异构集成

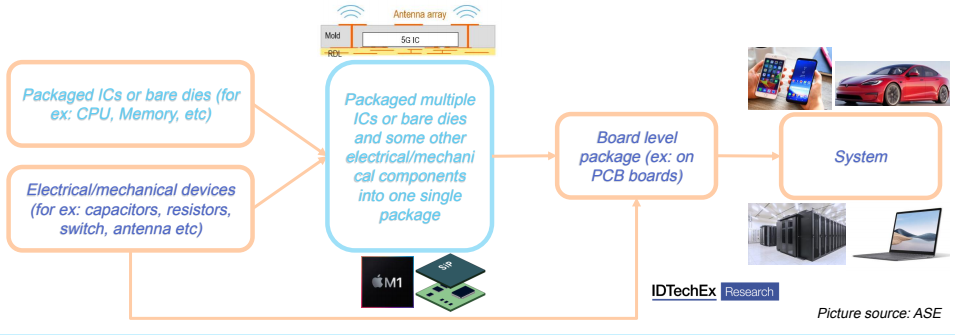

异构集成的基本概念是将多个有不同功能的组件组合在同一个封装中。在某种意义上讲,先进半导体封装就是一种“异构集成”,是指将IC到无源/有源电气/机械组件的多个器件集成到一个封装中,以此作为单个电子器件的封装技术。

如下面的流程所示,先进半导体封装是一种介于传统IC FeOL(半导体制造)和BeOL(传统封装)之间的又一种封装工艺。

先进半导体封装流程

和通用电子封装有四个流程相仿:一是封装IC或裸片(例如:CPU、内存等),电气/机械装置(例如:电容器、电阻器、开关、天线等);二是将多个IC或裸片和一些其他电气/机械组件封装到一个单独的封装中;三是板级封装(例如:在PCB板上);四是最终系统。不同之处在于将第二步的集成内容提前到了第一步。

异构集成有点像系统级封装(SiP),但它并不是将多颗裸片集成在基板上,而是将多个IP以小芯片的形式集成在基板上。其意义在于,将分开制造(不同制造工艺)的不同元件集成到更高级别的器件中,有助于增强功能并改进器件特性。

先进封装的关键市场

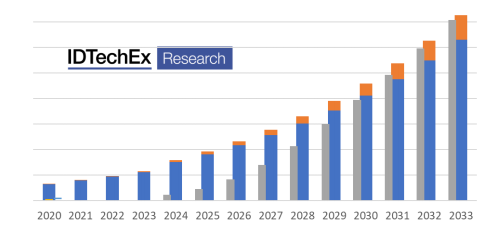

IDTechEx“2023-2033年先进半导体封装”报告指出,先进半导体封装是下一代IC的关键基础,将在四个关键市场发挥重要的作用:数据中心、5G、自动驾驶汽车和消费电子产品。采用的先进封装技术包括2.5D嵌入式硅、2.5硅内插器、2.5D(超)高密度扇出和3D管芯堆叠。

IDTechEx技术分析师Yu Han Chang博士认为,先进半导体封装为以数据为中心的未来铺平了道路。如今,数据在各个层面和几乎每个行业都呈爆炸式增长,数字世界每秒钟都会产生4000太字节的数据,预计这一数字在未来只会上升,尽管不是大幅上升。

他指出,机器学习和AI等数据丰富的应用是数据中心、5G和自动驾驶汽车等广泛应用的关键数据推动者。要运行这些应用,需要一个强大的处理器,其基础是基于硅的集成电路的技术创新。言外之意,在摩尔定律不给力的前提下,先进封装同样可以被认为是一种技术创新。

服务器加速先进封装单元出货量趋势

先进封装直击应用痛点

事实上先进封装的意义已经超出了封装本身,封装天线(AiP)就是一个典型的例子。AiP通过封装技术将天线与芯片集成在封装内,以实现系统级的无线功能,成为目前毫米波5G NR的首选封装技术基准。

封装天线技术将无源天线阵面、多种功能模块与无源天线集成在一起,满足了毫米波AiP解决方案中两个关键要求:一是IC和天线之间的互连应在所需频率范围内产生低插入损耗和可接受的回波损耗;二是尺寸应尽可能小。

三种常见天线集成方法中一些关键因素比较

未来的6G时代,片上/晶圆上天线(AoC/AoW)将进一步满足新一代系统的微型化、多功能、高性能、低功耗、低成本等多种需求。

头部玩家的先进封装之举

先进半导体封装的参与者非常多,其解决方案涵盖(超)高密度扇出(有机中介层)、3D片芯堆叠、2.5D硅中介层、2.5D嵌入式硅桥、3D堆叠存储器等几大类。

龙头代工厂及其解决方案当然还是台积电(InFO,集成扇出)、日月光(FOCoS,芯片后装的基板上扇出芯片)、三星(2.5D RDL(再分布层))、Amkor Technology(S-SWIFT,高密度扇出线),也包括中国的长电科技(XDFOI,多维扇出封装集成)。

从技术节点看,台积电和三星2020年实现了4/5纳米商用先进节点,英特尔是在2022年,更先进节点还在试验和开发中。

这两年AMD的奋起直追让处理器两大厂商之间的竞争进入了白热化阶段。据DigiTimes报道,2025年之前台积电和格芯大概率仍然是AMD的主要代工合作伙伴。不过,AMD也会将三星放入供应链。

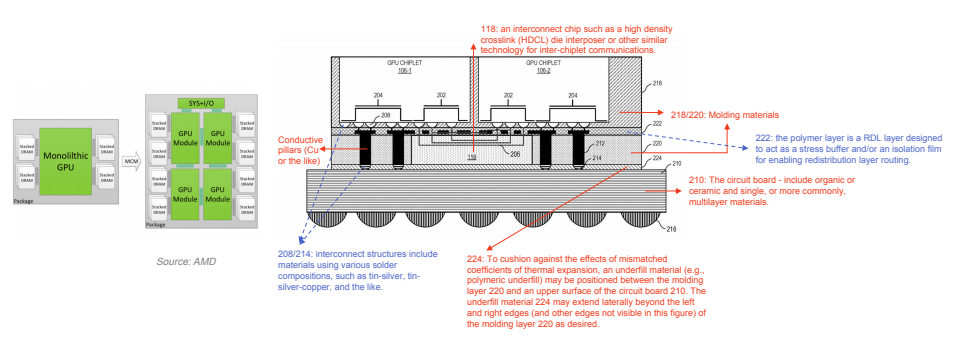

2020年底,AMD发布了GPU小芯片设计的新专利,其设计是将一个大型单片GPU拆分为几个小芯片,并使用扇出封装技术连接不同的片芯,但在基板上方添加一个小硅桥来连接两个片芯(AMD高架扇出桥2.5D)。

AMD未来显卡GPU小芯片设计

2023年初,AMD首发Navi 31 GPU,正式进入小芯片时代。历史上第一个小芯片GPU是1个GCD+6个MCD的组合体,有580亿个晶体管,采用台积电先进5纳米工艺制造。不过,其中较小的MCD小芯片尺寸仅为37平方毫米,包含内存控制器和Infinity缓存,使用6纳米工艺制造,不需要使用最新工艺。这意味着,小芯片架构的使用降低了成本,因为使用尺寸更小的芯片有助于减少一个晶圆上的缺陷芯片数量。

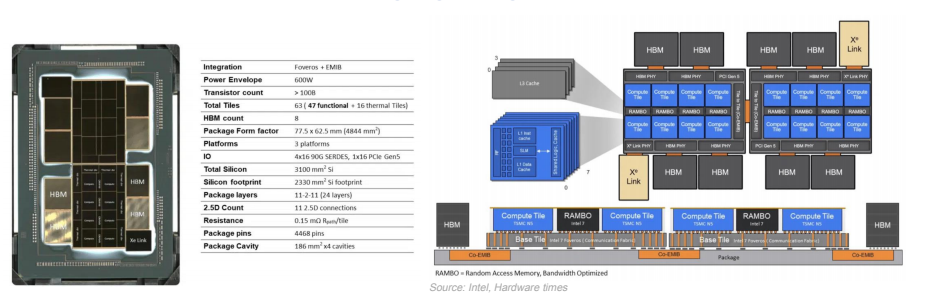

2022年8月,英特尔针对AI和HPC应用推出Ponte Vecchio封装的HPC GPU旗舰产品。Ponte Vecchio拥有超过1000亿个晶体管,将结合英特尔内部代工厂和台积电先进节点的三个不同节点。

其计算瓦片(tile)将在台积电的N5节点上制造,Xe Link瓦片将在台积电的N7(7nm)节点上制造,Foveros/Rambo Cache瓦片将在Intel 7(以前的10nm ESF)节点上制造。

Ponte Vecchio结合了英特尔的前沿封装技术,即Foveros(一种3D堆叠技术)和EMIB:两个基础瓦片(基础瓦片——HBM和计算瓦片——RAMBO)之间的连接都通过EMIB连接,而计算瓦片——基础瓦片和RAMBO与基础瓦片通过Foveros堆叠技术连接。

根据英特尔的说法,Ponte Vecchio和Sapphire Rapids HBM CPU将是阿贡国家实验室的Exascale Aurora超级计算机的两个关键组成部分。截至目前,Ponte Vecchio GPU仍处于客户送样阶段。

英特尔Ponte Vecchio封装

再来看应用端,ADAS/自动驾驶系统是当前的热点应用,面临着诸多挑战,既要求高性能、低功耗、系统占位面积小,又要求高性价比,因此需要高晶体管数量来应对日益增长的性能和高系统可用性要求,同时通过软件轻松升级车辆功能。

高晶体管数量意味着更大的IC片芯,传统的组件级零缺陷方法不再适用,需要从系统级角度来考量。制造大尺寸高端芯片也会带来工艺方面的挑战,未来可能会采用小芯片设计。

另外,CPU和其他组件的异构集成,如HBM(高带宽内存)和可靠的电力输送系统,需要与系统及组件优化相关的热管理;在处理热约束方面,还需要新型高导电TIM(热界面材料),同时也需要协同优化系统布局。

当然,新的先进互连和封装技术可能会增加成本,可能带来更高的风险。

自研的也不例外

在汽车领域,有了领头羊特斯拉,大众也决定追求自研芯片设计,首席执行官Herbert Diess曾表示,从汽车到芯片,只有一步之遥。他解释说:“随着汽车对计算的要求越来越高,软件和硬件应该来自同一个地方。”2022年7月Herbert Diess因未能达到开发预期突然离职。

不过,这也没有耽误大众的自研,2023年5月,大众汽车软件部门Cariad为加强其美国技术中心的研发能力,聘请了多位半导体专家,其中就包括来自特斯拉和苹果的顶级半导体专家。与特斯拉一样,三星似乎也是大众新的自研芯片的潜在制造供应商。此前曾有分析认为,大众可能将自主设计芯片外包给台积电代工生产。截至2021年11月,与台积电合作车用半导体的还有美国通用汽车(GM)。

2021年5月,为缓解芯片短缺问题,福特也表示将内部进行芯片设计,将与全球第四大代工企业格芯合作,与其直接签订供应协议。

在计算机领域,2022年首次推出的新款M1 Ultra芯片采用了台积电的扇出技术。据苹果公司称,M1 Ultra芯片将两个M1 Max芯片组与1140亿个晶体管、一个20核CPU和一个64核GPU结合在一起,使该芯片在消耗相同功率的同时,提供比最快的16核台式机高90%的多线程性能,并比当前市场上最快的台式机GPU性能更高,功耗却减少了200W。

苹果的M1 Ultra芯片

M1 Ultra主要为台式电脑设计,将在苹果新的Mac Studio中使用,是目前唯一一款采用新款M1 Ultra处理器的电脑,起价3999美元。

苹果公司表示,其最强大的Mac Studio定制硅利用UltraFusion芯片对芯片的连接来实现2.5TB/s带宽,其中包括两个并行工作的M1 Max SoC的通信。

苹果公司的新M1 Ultra芯片并不是在台积电的CoWoS-S(带硅中介层的基板上晶圆芯片)2.5D封装工艺上大规模生产的,而是带有本地硅互连(LSI)的集成扇出(InFO)。

通常认为,选择InFO LSI而不是CoWoS,是因为它是合并了两个小芯片的更具成本效益的替代方案。

一路向前

事实上,先进封装技术要求很高,资本投入也很高,只有大厂才能玩得起。经过长时间的研发,领先大厂均已开始提供异构集成的先进封装工艺服务,通过绑定先进工艺到先进封装的一条龙服务,为顶级客户定制最优化的产品,主要应用于汽车HPC(高性能计算)和高档智能手机的芯片制造。

随着时间的推移,由于摩尔定律发展至今已遇到瓶颈,芯片尺寸已接近物理极限,作为延续摩尔定律的一条重要途径,先进封装技术将为摩尔定律“续命”。

1976

1976

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

-1-%E5%89%AF%E6%9C%AC.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[下载]LAT1482 STM32G0单线串口通信帧错误问题解析

[下载]LAT1482 STM32G0单线串口通信帧错误问题解析