日前,在IEDM 2022(2022 IEEE国际电子器件会议)上,英特尔宣布要将封装技术密度再提升10倍,并使用厚度仅三个原子的新材料推进晶体管微缩,为在2030年打造万亿晶体管芯片铺平道路。

英特尔研究人员展示的成果有:3D封装技术的新进展,可将密度再提升10倍;超越RibbonFET,用于2D晶体管微缩的新材料,包括仅三个原子厚的超薄材料;能效和存储的新可能,以实现更高性能的计算;量子计算的新进展。

值得一提的是,今年是晶体管诞生75周年。从英特尔公布的多项研究成果来看,有助于其继续突破瓶颈,满足下一步计算需求,未来十年内继续推进摩尔定律的演进。

延续摩尔定律的前沿创新

三个关键方向

在IEDM 2022,英特尔的组件研究团队展示了在三个关键领域的创新进展,以实现摩尔定律的延续:新的3D混合键合(hybrid bonding)封装技术,可无缝集成芯粒;超薄2D材料,可在单个芯片上集成更多晶体管;能效和存储的新可能,以实现更高性能的计算。

具体而言,第一个方向是新的3D混合键合封装技术,相当于把3D封装的密度进一步提高了10倍,然后用不同的技术组合在封装层面实现,达到和用单芯片去做一个系统类似的密度,包括带宽、甚至能效方面也要达到同样级别。

第二个方向是半导体微缩。多年来,摩尔定律主要依赖于晶体管微缩,而传统的硅材料未来将会遇到瓶颈。英特尔在去年的IEDM上就公布了新的超薄二维材料方面的研究,今年更进一步深化了研究成果。

第三个关键方向是新的存储相关材料,在铁电、反铁电等存储体材料方面进行深入研究,提高它的存储容量、密度,减少体积和能效比,提高控制效率。这些都是为未来的嵌入式存储能够达到更高的功效密度,实现更高性能的计算和存储。

下一代3D封装技术可实现准单片芯片

与IEDM 2021上公布的成果相比,英特尔在IEDM 2022上展示的最新混合键合研究将功率密度和性能又提升了10倍。并且通过混合键合技术将互连间距继续微缩到3微米,英特尔实现了与单片式系统级芯片(system-on-chip)连接相似的互连密度和带宽。

何为准单片芯片(quasi-monolithic chip)?据英特尔研究院副总裁、英特尔中国研究院院长宋继强博士介绍,封装本身是封装层级的工艺,一个芯片的wafer,它的die做出来之后,用封装材料和工序把它们封在一起。这本来是两个步骤的事,因为材料、制程工艺以及工厂的洁净度要求都不一样。不过,英特尔使用多个芯片集成,做出一个大的封装级芯片,希望它能达到更高的密度。这相当于把原来封装工厂做的事情,转移到芯片工厂去做了。

这其实是通过混合键合技术、新材料和新工艺,模糊了封装和芯片制造之间的界限,一方面将3D封装互连的多个步骤由封装厂转移到芯片制造工厂中,另一方面也为顶端芯粒和底部芯粒的大小与相对位置带来最大的灵活性,解决了典型硅通孔的功率和信号完整性问题。例如通过英特尔的试验和选择,通过TDV绝缘无机填充物过孔的方式,可以不需要增加额外一个芯粒就形成过孔连接,还能在增加过孔连接线密度时提升信号完整性。

这样带来的好处是,在推进多个芯片互连的时候,可以把很多工艺流程整合在wafer fab,封装厂只需在准单片的基础上做后续封装。

超薄2D材料在单个芯片上集成更多晶体管

英特尔展示了一种全环绕栅极堆叠式纳米片结构,使用了厚度仅三个原子的2D通道材料,在室温下实现了近似理想的低漏电流双栅极结构晶体管开关。

研究人员还展示了对2D材料的电接触拓扑结构(electrical contact topologies)的首次全面分析,为打造高性能、可扩展的晶体管通道进一步铺平道路。

探索能效和存储的新可能

通过开发可垂直放置在晶体管上方的存储器,英特尔重新定义了微缩技术,从而更有效地利用芯片面积。英特尔展示了性能可媲美传统铁电沟槽电容器(ferroelectric trench capacitors)的堆叠型铁电电容器(stacked ferroelectric capacitors),可用于在逻辑芯片上构建铁电存储器(FeRAM)。

据介绍,这一业界首创的器件级模型,可定位铁电氧化器件(ferroelectric hafnia devices)的混合相位和缺陷,标志着英特尔在支持行业工具以开发新型存储器和铁电晶体管方面取得了重大进展。

英特尔正在为打造300毫米硅基氮化镓晶圆(GaN-on-silicon wafers)开辟一条可行的路径,从而离超越5G和电源能效问题的解决更进一步。这一突破实现了比行业标准高20倍的增益,并在高性能供电指标上打破了行业记录。

此外,英特尔在超高能效技术上也取得了突破,特别是在断电情况下也能保留数据的晶体管。“至此,对于三个阻碍该技术在室温下完全实现并投入使用的障碍,英特尔的研究人员已经解决其中两个”,宋继强表示。

制造用于量子计算的性能更强的量子位

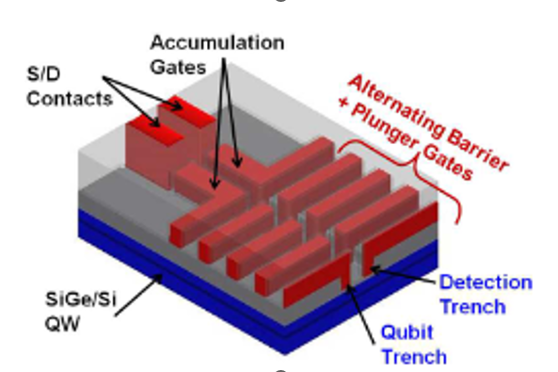

英特尔的研究人员加深了对各种界面缺陷(interface defects)的认识,这些缺陷可能会成为影响量子数据的环境干扰(environmental disturbances),从而找到了储存量子信息的更好方法。

据了解,有关量子位的制造,英特尔曾尝试了两种不同类型的量子位:一种是用固态电路模拟量子位,另一种是通过硅电子自旋的方式。考虑到自身优势,英特尔在批量化生产、制造更大规模量子位道路上,还是认为硅基量子点的方式最可行。

以下概念图简单展示了这一概念,量子阱里可以操控硅的单电子自旋方向,而电子自旋的方向就用于表征量子比特的状态。但从生产制造角度来看,不同层的表面、层与层之间都会产生缺陷,而这些缺陷会影响量子比特的稳定性,甚至会产生虚假量子比特的可能。总体而言,目前的量子比特仍然处于量级较少的状态,还属于试验型测试芯片,尚处于充分理解如何制造大批量、能够达到未来良率的量子比特的阶段。

制程是根本,封装是加分

近年来,英特尔在先进封装领域投入颇多,且先进封装技术对未来芯片显现出了较大的性能提升,其功效甚至不亚于先进制程的提升。在这样的背景下,英特尔未来是否会更注重先进封装的发展?

宋继强表示,先进制程是基础,是重中之重。如果没有好的晶体管,没有好的die,仅靠封装达不到最好的效果。先进封装技术,像准单芯片设计,现在最好的预期也就是和单芯片达到一个数量级左右的差距。间距方面,先进封装通过hybrid bonding能达到的最好间距是3微米左右;而单芯片通过先进制程实现的很多互连的线宽间距都在100纳米,如果针对高性能、高节点工艺,很可能是100纳米以下。也就是说,准单芯片和真正的单芯片之间,其实还有一到两个数量级的差距,只不过比起以前几个数量级的差距有缩小。

他强调,先进制程和先进封装一定要齐头并进地推进,因为一方面要通过更好的晶体管设计,让一个die既小又功耗低,还可以容纳更多的晶体管。另一方面,还可以把不同工艺节点上不同厂家的芯片能够封装在一起,这是进一步提高系统集成度的方法。

对英特尔来说,制程一定是根本,同时在封装方面进一步去扩展、去加分。现在英特尔提的系统级封装(systems foundry)理念,也是希望把原来做代工的经验,比如对材料、制程工艺的理解,进一步推到封装领域。因为很多最基本的对材料、对制程的要求原来都是来自于先进制程的,然后才逐步在封装领域形成需求。

“芯粒”将如何影响芯片设计乃至半导体商业模式?

宋继强表示,英特尔已经从原来的大芯片设计明确转到支持分块、分片化设计了,前两年提出的disaggregated设计理念,其实就是要把芯片分解,这和业界所提的芯粒的思路是一致的。例如,英特尔把CPU、GPU和IPU变成多个小块的die组合在一起,构成一个大的系统,Ponte Vecchio就是很典型的例子,它采用了多个不同的工艺节点、不同的架构组合在一起。未来,英特尔将会有更多芯片采用芯粒的方式做设计。

至于未来是否会有商业模式上的变化?比如IP厂商将其IP芯片化,或是传统的芯片厂商会将其关键技术进行拆解,去对外销售,从而便于其他芯片厂商各自进行芯片组合设计?

对此,宋继强表示,这个商业模式其实正在发生,英特尔所提的IDM 2.0,即系统级代工模式,其实都是在往这个方向迈进。现在一些主要IP,原来是用可综合的软IP形式,或是和某些工艺节点完全对应绑定的硬IP形式提供给SoC设计厂商。

未来,如果芯粒形成很好的互联互通的标准,在某些IP比较成熟、比较流行的情况下,且某个工艺节点做出来的某些die会被大量采用,一定会有厂商往这个方向发展。比如在可以预先锁定一些产能的情况下,先做出一些芯粒,这样的话就可以供应给其他厂商去采用,相信未来会有IP供应商向这一方向努力。

再从传统的芯片设计厂商角度来看,肯定也存在有一定通用性的模块是可以拆解出来,进行IP化的。可以通过做很多测试,进行一些定义,使它更加通用化之后形成IP。

其实,英特尔在这方面已经旗帜鲜明地进行了表态,今年在系统级代工的发布时就曾提到,x86 CPU、GPU的一些计算模块,未来可以作为一些硬IP去授权。以及英特尔现在的很多芯片设计,未来如果拆解成小的模块、变成小的die,去和一些用户产品进行集成封装的话,也是可行的。

写在最后

2030年之时,英特尔在单芯片中放入1万亿晶体管的目标能不能实现?从当前的现实来看,这意味着要从2023年到2030年,实现单芯片上的晶体管数量从1千亿颗变为1万亿颗。

无论从哪个角度衡量,这都是一个相当激进的目标,需要晶体管微缩技术、新3D封装技术等前沿组件研究的革命性突破,换言之,这是一个系统级的大工程。但这恰恰也可能是比较合适英特尔的“战术”,重新盘活英特尔全面的芯片设计、制造能力,再加上芯粒、软件等技术力量,将有助于英特尔完成面向下一个十年的“撑杆跳”。

1780

1780

下载ECAD模型

下载ECAD模型

[下载]LAT1482 STM32G0单线串口通信帧错误问题解析

[下载]LAT1482 STM32G0单线串口通信帧错误问题解析