半导体业界的年度盛事–超大型积体技术及电路国际会议(Symposium on VLSI Technology and Circuits),再度成为各大技术研究机构展示其研发成果的舞台。包含比利时微电子研究中心(imec)及中国台湾的工研院,都在这次论坛期间发表其最新的研究成果。

工研院连结产学 磁性记忆体取得重大突破

工研院在今年的VLSI论坛上,分别发表了与台积电合作的自旋轨道扭矩磁性记忆体(Spin Orbit Torque Magnetoresistive Random Access Memory, SOT-MRAM)阵列晶片,以及和阳明交通大学联合开发,工作温度横跨近400度的新兴磁性记忆体技术。

工研院电子与光电系统所所长张世杰表示,MRAM有媲美SRAM的读写速度,兼具快闪记忆体非挥发性,近年来已成为半导体先进製程、下世代记忆体与运算的新星。记忆体若在高写入速度的前提下,使用的电压电流越小,则代表效率越高,工研院携手台积电共同发表具备高写入效率与低写入电压SOT-MRAM技术,并达成0.4奈秒高速写入、7兆次读写之高耐受度,比欧洲最大的半导体研究机构imec先前创下的纪录多一百倍,还有超过10年资料储存能力等特性,未来可整合成先进製程嵌入式记忆体,在AI人工智慧、车用电子、高效能运算晶片等领域具有极佳的前景。

工研院与阳明交通大学的合作,则聚焦在自旋转移矩磁性记忆体(Spin-Transfer-Torque MRAM, STT-MRAM)的多层膜与元件改良上,可提高写入速度、缩短延迟、降低写入电流与增高使用次数等特色,且工作温度为摄氏127度到零下269度。工作温度横跨近400度的多功能磁性记忆体是首次被实验验证,未来在量子电脑、航太领域等前瞻应用与产业上,具备极大的潜力。

imec展示晶背供电整合方案

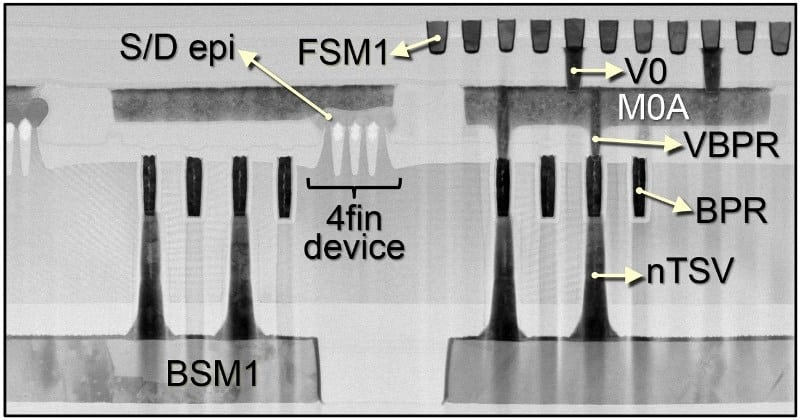

imec在今年的VLSI论坛上,则是以晶背供电技术作为发表的重点。imec首度展示基于埋入式电源轨(Buried Power Rail, BPR)技术,从晶片背面供电的逻辑IC布线方案。BPR採用奈米硅穿孔(nTSV)结构,将晶圆正面的元件连接到BPR上,取得运作所需的电力。微缩化的鳍式场效电晶体(FinFET)若透过这些BPR实现互连,性能便可不受晶背製程影响。

imec所展示的晶背供电整合布线。FinFET微缩元件透过nTSV与BPR连接至晶圆背面,与晶圆正面连接则利用BPR、通孔对电源轨(via to BPR;VBPR)以及电源超出主动区(metal over active;MOA)的结构设计

这套先进的布线方案能分离电源线与讯号线的配置,推动2nm以下逻辑晶片持续微缩,还能增强供电效能,进而提升系统性能。此外,imec也在晶圆背面导入了採用2.5D金属—绝缘体—金属(MIM)结构的电容,展现更佳的晶片效能。

把电源线跟讯号线分开,可以有效减缓后段製程布线壅塞的问题,还能带来优化供电效能的好处。imec于2019年首次提出这项技术,不同的製程方案也随之出现。例如,在2021年VLSI论坛,imec首度展示晶背导线互连的实例,将奈米硅穿孔连接到位于晶圆正面的M1金属层衬垫。在2022年,imec进一步展示了一套进阶整合方案,透过BPR将FinFET微缩元件一齐连接到晶圆正面与背面,创下全球首例。

imec的CMOS元件技术研究计画主持人Naoto Horiguchi表示,从微缩元件与提升性能的角度来看,採用晶背供电设计并导入埋入式电源轨是最有可能实现晶背供电网路的解决方案,这些电源轨在前段製程中埋入晶片,以局部布线的结构设计推动晶片微缩。

他接著说明,imec在开发测试晶片时,从晶圆正面定义埋入式电源轨的图形,随后将奈米硅穿孔连接到这些电源轨上,结果显示FinFET元件性能不受晶背製程影响,这就包含接合目标晶圆与承载晶圆、薄化晶背以及製造深度长达320nm的奈米硅穿孔。奈米硅穿孔以垂直向与埋入式电源轨紧密接合,各穿孔的间距仅200nm,不佔用标准单元尺寸,能确保元件继续微缩至2nm以下。

晶背供电设计可望从系统层面提升整体供电效能,尤其目前元件所需的功率密度持续攀升,供应电压或IR压降的问题也越来越严峻。imec的3D系统整合计画副总裁Eric Beyne指出,为了应对IR压降问题,imec在晶背製程中导入一颗2.5D柱状MIM结构的去藕电容。透过这颗2.5D电容,电容密度因此提升了4~5倍,IR压降现象与不使用电容及2D电容相比,分别改善了32.1%及23.5%。这些分析结果来自一套经过实验数据校正的IR压降模拟架构。

Beyne总结说,我们的研究成果显示晶圆背面具备高弹性的设计空间,还能诉诸全新的设计选择,解决传统2D晶片微缩的痛点。此外,我们也展示了一些3D系统级微缩技术的效能,在剥离承载晶圆时,以功能性晶圆取而代之,例如用于3D SOC逻辑元件堆叠的逻辑晶圆,而底层的晶粒可从晶背取得电源供应。

芯耀

芯耀

313

313