当业界还沉浸在3nm何时量产交付时,IMEC就公布了0.2nm路线,引发半导体行业的轩然大波。ICVIEWS邀请到千芯科技陈巍博士对IMEC到0.2nm工艺的路线图进行深入解读。超详细解析Nanosheet、Forksheet、CFET等微缩器件技术,晶体管背面供电技术和系统-工艺协同优化(存算一体的形式)技术。

——ICVIEWS 智库专家:陈巍 博士

与台积电、英特尔和AMD等公司的产品路线图相比,IMEC 的路线图可以让我们对半导体行业的技术推进有更前瞻的了解。

比利时研究机构IMEC于2022年5月17日举办了年度技术盛会“FUTURE SUMMITS 2022”,并展示了半导体器件突破微型化极限的路线。该路线让我们大致了解了到IMEC与台积电、英特尔、三星和 ASML 等行业领先巨头合作研发的情况,特别是下几代主要工艺节点和晶体管架构的推进时间表。

与台积电、英特尔和AMD等公司的产品路线图相比,IMEC 的路线图可以让我们对半导体行业的技术推进有更前瞻的了解。预计到到2036年,IMEC将实现0.2nm工艺。

下面对IMEC到0.2nm工艺的路线图进行深入解读。特别是IC进步的三大动力,包括Nanosheet、Forksheet、CFET等微缩器件技术,晶体管背面供电技术和系统-工艺协同优化(存算一体的形式)技术。

来源:IMEC

发展到0.2nm的工艺微缩路线图

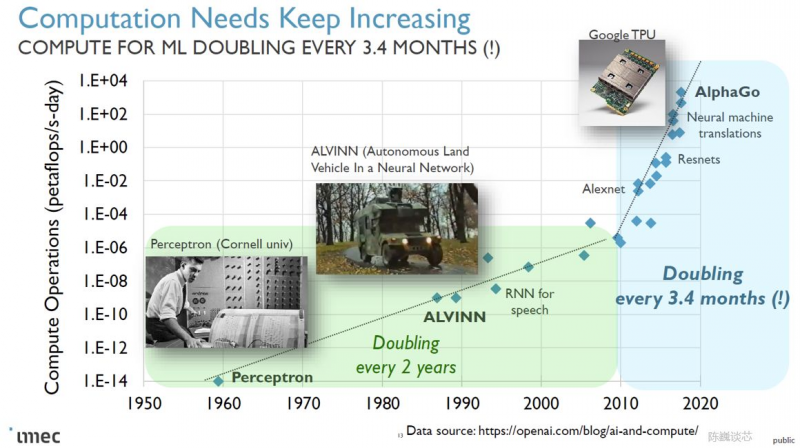

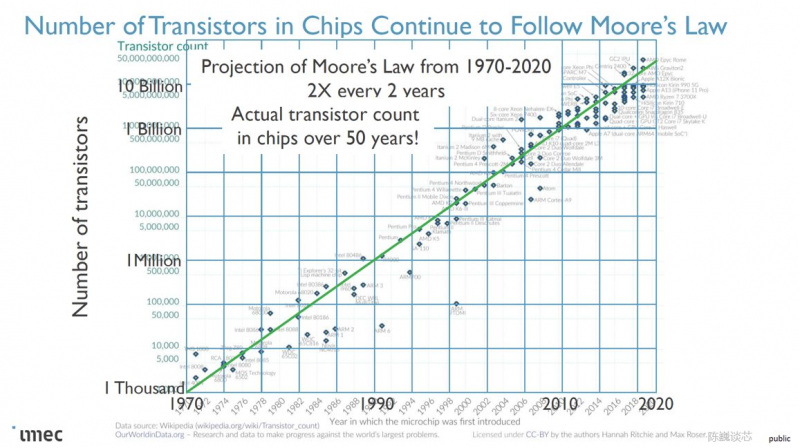

在前几年,算力需求大概每两年翻一番,基本上能对应摩尔定律对半导体产业的性能提升预测。但最近AI所需的算力大约每六个月翻一番,即使晶体管数量持续以摩尔定律的速度发展也无法跟上计算需求的步伐。IMEC认为,工艺微缩(包括更高的密度和封装技术)、新材料和设备、系统-工艺协同优化 (SCTO,以存算一体的形式) 的三管齐下的解决方案可以使行业保持更高的增速。

来源:IMEC

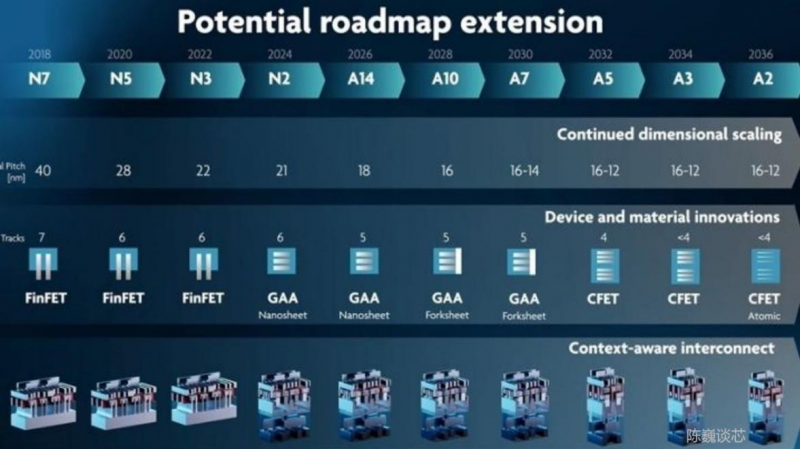

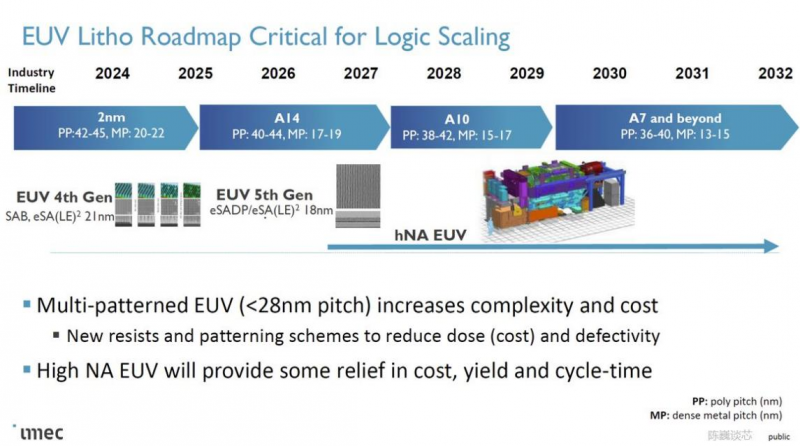

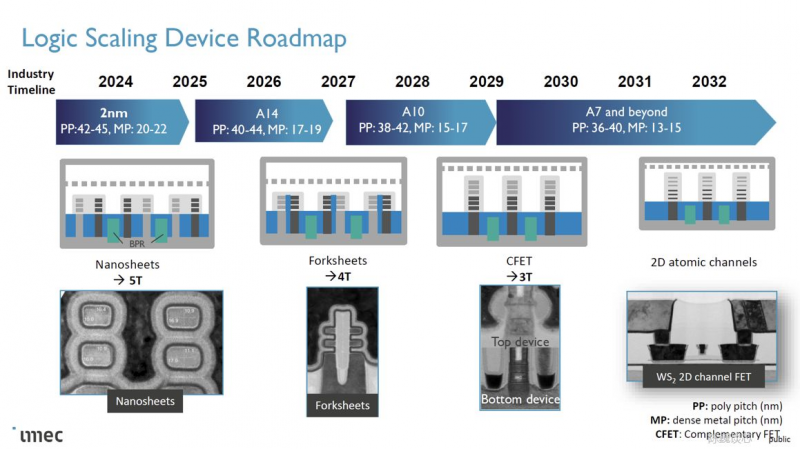

目前,世界上将量产的最先进工艺节点是3nm(N3)。在N3工艺试产后,2024年2nm工艺落地,2026年则有A14工艺落地。(A代表Ångström, 简称埃,符号Å)

来源:IMEC

IMEC预计2028年实现A10工艺,也就是1nm节点。2030年是A7工艺,其次是A5、A3、A2工艺。2036年的A2相当于0.2nm节点。这一前进步伐满足摩尔定律的要求。

当然这些进步主要是有源器件的提升。决定工艺密度的金属栅距等指标,并没有显著改善。这就意味着,即使是A7到A2,晶体管密度可能也没有明显提升。

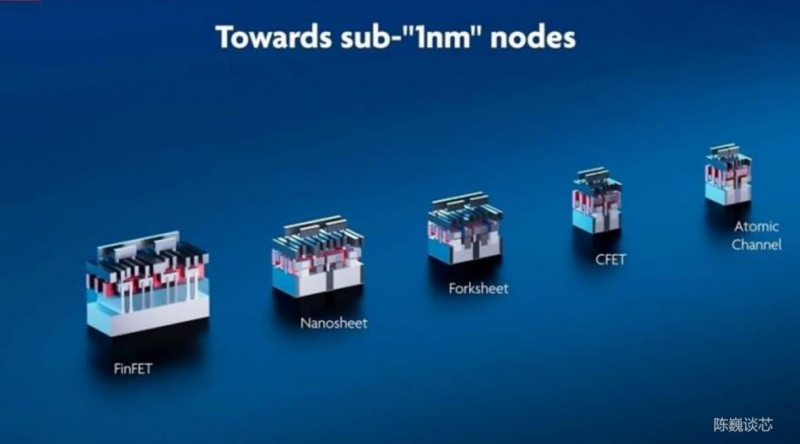

当前先进的半导体器件采用“FinFET(鳍型场效应晶体管)”结构。2nm 代开始,下一代晶体管“GAA(Gate-All-Around)”和“CFET(Complementary FET)”等将陆续被采用。

Gate All Around (GAA)/Nanosheet 晶体管将于 2024 完成,采用 2nm 节点,取代目前的FinFET技术。

来源:IMEC

IMEC预计 GAA/Nanosheet 和 Forksheet 晶体管(GAA 的更密集版本)将持续前进到 A7 节点。互补 FET (CFET) 晶体管将在 2032 年左右进一步缩小尺寸,从而实现高密度。到2032年,我们将看到具有原子通道的 CFET 版本,进一步提高性能和密度。

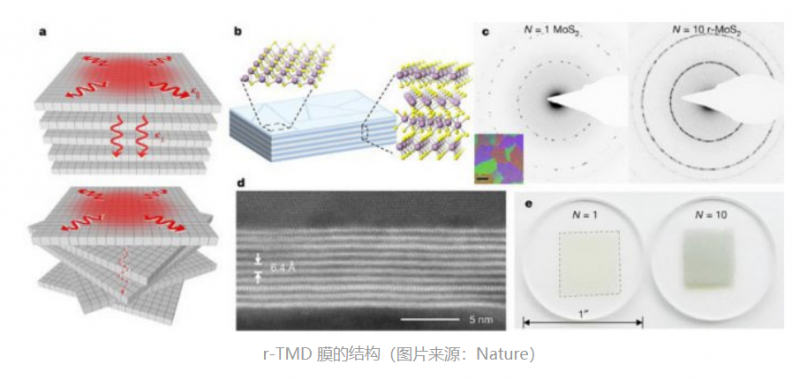

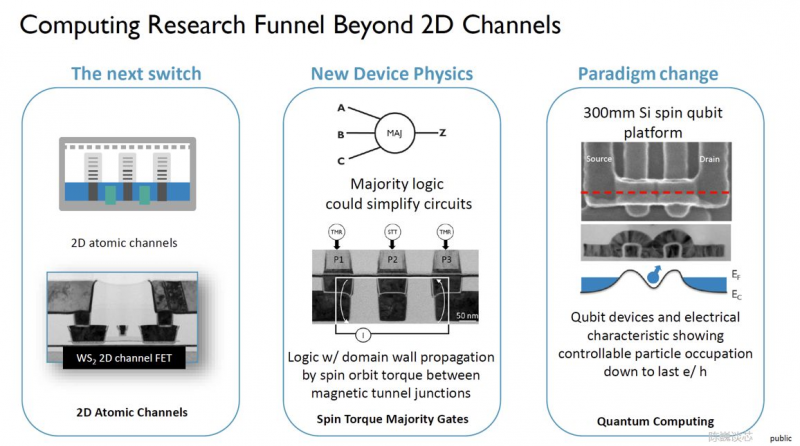

在微缩的同时,新材料也将持续被引入半导体制造。与硅基材料相比,二维半导体材料具有非常好的潜力。目前比较具有代表性的二维半导体材料是过渡金属硫化物(TMD),如二硫化钨(WuS2)、二硫化钼(MoS2)等。

Naosheets、Forksheets和CFET

在1nm及更先进工艺中,晶体管结构发生了巨大变化。台积电和三星在3nm/2nm节点放弃FinFET,转为GAA结构,A5之后则转为CFET晶体管结构。

在IMEC的晶体管路线图中,有Nanosheet、Forksheet和CFET。

形象点说,如果FinFET是三面包栅的平排沟道结构,那GAA中的Nanosheet就是四面环栅的叠在一起的的沟道结构,提升了沟道控制力和密度。而GAA中的Forksheet就是以三面包栅,中间介电墙隔离的方式减小n管-p管的间距, 进一步提升密度。CFET堆叠的最彻底,将n管和p管堆叠,密度最大。

Nanosheet(纳米片)作为一种GAAFET结构,晶体管的导电沟道完全被包围在高介电系数材料之中,因此,栅极在沟道缩短的情况下,仍能表现出很好的沟道控制能力。

多个纳米片通道垂直堆叠以增加晶体管的有效宽度,从而提供额外的驱动电流,进一步降低元件尺寸。

来源:IMEC

Forksheet由IMEC提出,最早是在2017年IEDM发表的SRAM微缩研究上出现,在2019年则作为逻辑标准单元的微缩解决方案展示出来。Forksheet缩短了n-p沟道的间隙,减小了n管和p管的互连电阻,更有效的提高了晶体管密度和整体性能(特别是直流性能)。与Nanosheet不同,Forksheet在n型与p型晶体管之间有一个介电墙,可大大缩短n型与p型晶体管的间距。

Forksheet不足在于,其栅极没有将沟道完全环绕,因此沟道控制力略有下降。

来源:IMEC

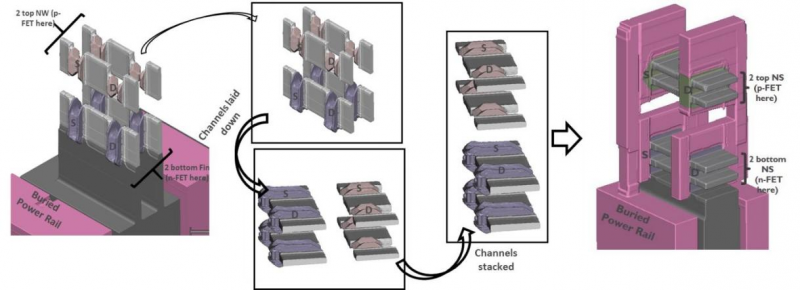

互补式场效晶体管(Complementary FET;CFET)则是改进沟道控制力的优质架构选择。

CFET 允许将 n 晶体管堆叠在 p 晶体管之上,从而以工艺复杂度为代价节省大量面积。

除了水平沟道结构的CFET,也可以采取垂直沟道结构的CFET。则此时n-p间距转成垂直方向,标准单元的高度限制被大大解除。

对CFET架构来说,需要全新的金属布线设计方式和衬底的埋入式电源轨道 (BPR))。

IMEC表示,CFET架构支持未来的逻辑元件或SRAM持续微缩,是CMOS电路的最佳器件选择。其沟道的构形可以是n型或p型的鳍片,或是n型或p型的纳米片。

来源:IMEC

来源:IMEC

晶体管背面供电

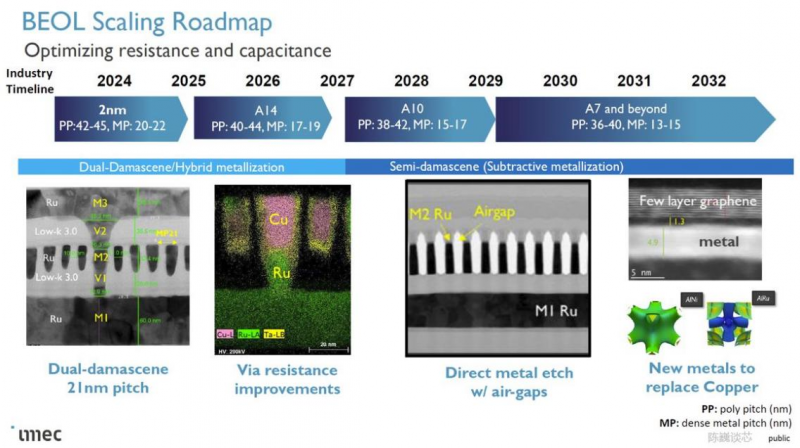

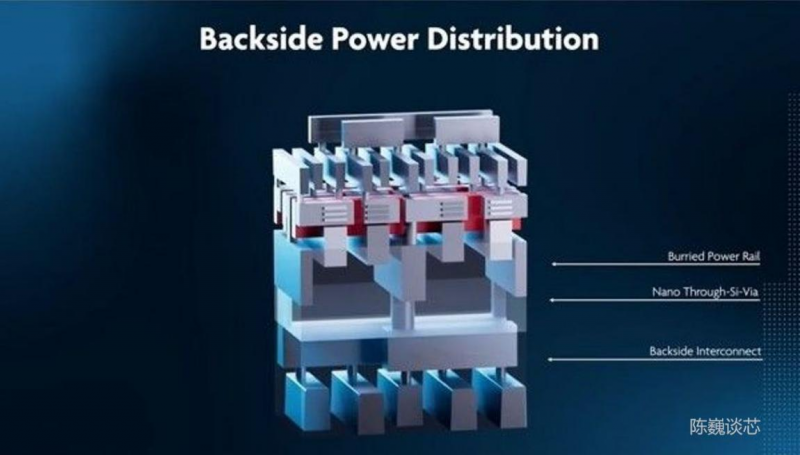

为了提高晶体管的性能,进一步改进密度,还需要增强的后道 (BEOL) 工艺,持续改进金属布线结构。BEOL 的作用在于将不同晶体管连接在一起,实现信号传送和供电,完成完整的逻辑功能。背面供电可直接提升晶体管密度和性能。

英特尔已经宣布称为 PowerVIA的背面供电技术。这种技术通过晶圆的背面将电力传输到晶体管,而信号传输依然保持在晶圆的顶面。

IMEC后道工艺路线图 来源:IMEC

晶体管层上一般有10层或更多的布线层。但随着芯片集成度的提高,连接晶体管的布线变得异常复杂。再加上串扰等问题的同时存在(不能过密),布线密度要求严重阻碍了芯片密度的提升。通过从背面供电,可以增加正面布线设计的灵活性。

打个形象的比方,传统布线方式就好比粗细线混织的毛衣,十分混乱。背面供电则像是粗线织里层,细线织外层,毛衣变厚了,同时密度提高了很多,但毛线的间距变化不大,编织的难度也降低了。

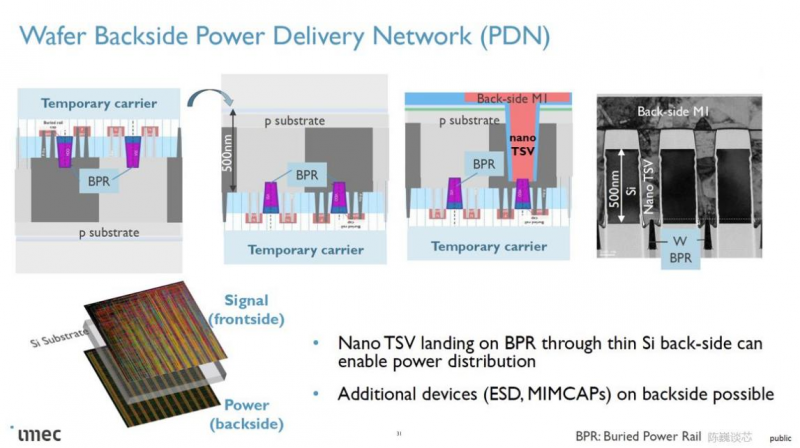

BPR的路线图的包括用于互连的直接金属蚀刻技术,以及具有气隙的自对准通孔。IMEC也在研究替代铜互连的新材料(例如石墨烯)。

晶体管背面供电实现布线层的灵活设计 来源:IMEC

分离电源电路和数据互连改善了IR-Drop,可允许更快的晶体管开关速度,且在芯片正面实现更密集的信号布局布线。同时,信号传输也因简化布线而缩短长度并降低串扰,同时减少了导通电阻和寄生电容。

来源:IMEC

IMEC通过埋入式电源轨道(Buried Power Rails,BPR)在晶体管下方建立电源连接,可构建更粗、电阻更小的电源网格,并为晶体管上方的信号互连腾出空间。

来源:IMEC

系统-工艺协同优化技术与存算一体

逻辑技术发展趋势 来源:IMEC

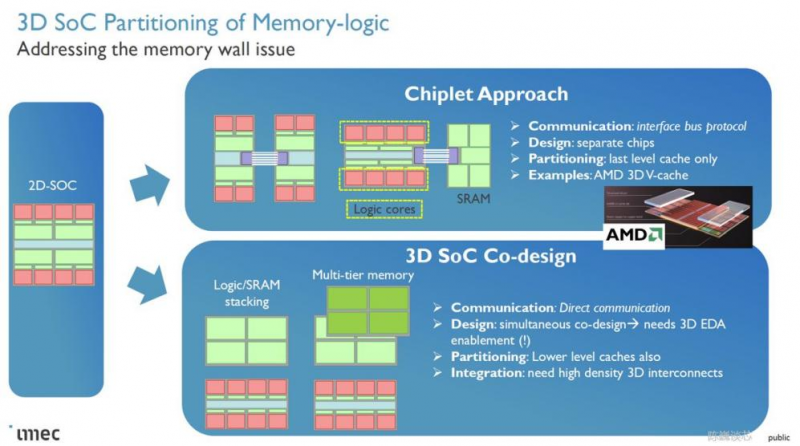

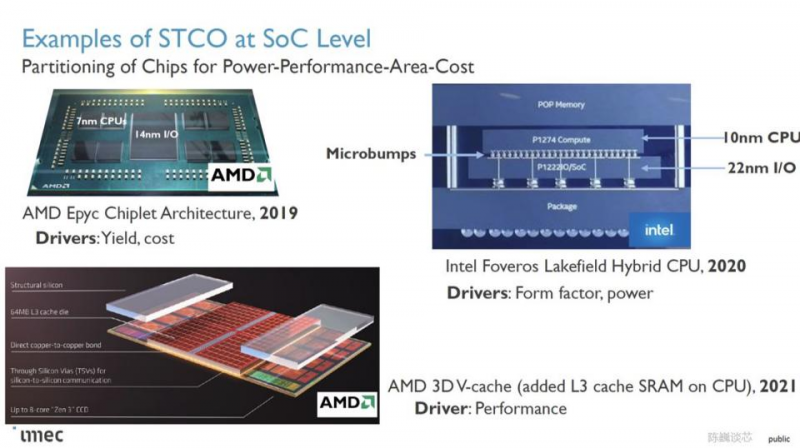

IMEC也强调了系统-工艺协同优化 (STCO) 技术的进展。例如 3D 互连和 2.5D 芯粒技术实现。特别是IMEC 正在与 Cadence 合作 3D 芯片设计的电子设计自动化 (EDA) 软件,以提升3D IC设计的效率。

我们可以看到,对IMEC的STCO,特别是3D设计而言,技术的重中之重是通过工艺进步实现存算一体架构。即基于工艺制造实现,逻辑与存储整合的近存架构,进而推动算力的进一步发展。

存算一体技术的典型受益的代表就是AMD的Zen系列CPU。

基于工艺支持的存算一体架构 来源:IMEC

系统-工艺协同优化的示例 来源:IMEC

当逻辑和存储三维结构连接时,不同单元可以缩短彼此之间的距离,有利于芯片之间的高速数据传输,并节约能耗。无论是对传统的冯诺依曼架构的处理器,还是类脑或神经芯片,都能通过存算一体的架构(这里是近存计算架构)获得巨大性能收益。

高性能半导体芯片的立体结构截面图 来源:IMEC

半导体技术未来趋势

通过IMEC在其“FUTURE SUMMITS 2022”做的技术发布,我们可以看到半导体技术的未来趋势,包括:

工艺微缩,特别是晶体管工艺器件结构向立体垂直发展,包括沟道垂直、供电分立。

新材料与设备的持续导入。

半导体进入系统-工艺协同优化时代(以存算一体/Chiplet的形式为代表)。

0.2nm路线的到来再次延续了摩尔定律的寿命,面对目前的工艺制造瓶颈半导体行业出现了很多新的研究方向。而在唱衰摩尔定律的曲调中,或许摩尔定律能继续保持其应有的势头前进。

芯耀

芯耀

1290

1290

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍