Sony半导体(Sony Semiconductor Solutions Corporation)2021年12月,于IEEE会议上宣布成功开发世界上第一款具有双层电晶体画素的堆叠式CMOS影像感测器技术。传统CMOS影像感测器的光电二极体和画素电晶体一起併排在基板上,而Sony的新技术将光电二极体和画素电晶体可以垂直堆叠于基板。与传统影像感测器相比,这种新架构大约增加了一倍饱和讯号位准(Saturation Signal Level),扩大了动态范围并降低杂讯,显著提高成像性能。

堆叠式CMOS影像感测器架构

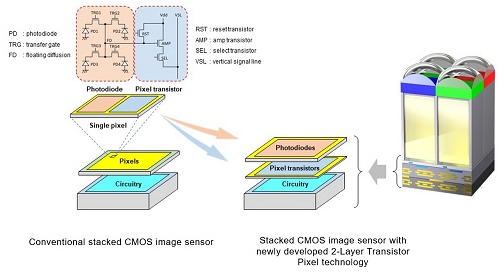

Sony新技术的画素结构将使画素能够保持或改善其现有属性,不仅是当前的,而且是更小的画素尺寸。堆叠式CMOS影像感测器採用由画素晶片组成的堆叠结构,该画素晶片由堆叠在形成讯号处理电路的逻辑晶片顶部的背照式画素组成。在画素晶片内,用于将光转换为电讯号的光电二极体和用于控制讯号的画素晶体管彼此并排位于同一层上。在外形尺寸限制内增加饱和讯号位准对于实现具有高动态范围的高解析影像非常重要。

Sony的新架构是堆叠CMOS影像感测器技术的进步。利用其专有的堆叠技术,Sony将光电二极体和画素电晶体封装在单独的基板上,一层一层堆叠。相比之下,在传统的堆叠式CMOS影像感测器中,光电二极体和画素电晶体并排放置在同一基板上。新的堆叠技术允许採用能够优化光电二极体和画素电晶体层的架构,使饱和讯号位准相对于传统影像感测器大约增加一倍,进而扩大动态范围。

双层电晶体画素堆叠式CMOS影像感测器垂直角度架构

另外,因为除了传输门(TRG)之外的画素电晶体,包括复位晶体管(RST)、选择晶体管(SEL)和放大器晶体管(AMP),占据了无光电二极体层,所以放大器晶体管的尺寸可以增加。通过增加放大器晶体管的尺寸,Sony大幅降低了夜间和其他黑暗位置图像容易产生的杂讯。

这项新技术提供的更宽的动态范围和降噪功能将防止在结合明亮和昏暗照明(例如背光设置)的设置中曝光不足和过度曝光,即使在低光照条件下也能获得高质量、低噪声的图像(例如、室内、夜间)设置。Sony将透过其双层电晶体像素技术为智慧手机照片等越来越高解析的图像做出贡献。

芯耀

芯耀

262

262