从聊天机器人程序ChatGPT,到文生视频大模型Sora,AI大模型的蓬勃发展背后,为算法模型、高质量数据、算力基础设施带来了持续的挑战。“当企业通过Scale out提升集群规模,就需要把数据中心从微观到宏观、点对点地连接起来,增强各个层面的互联性能,真正有效地应用算力资源。” 奇异摩尔创始人兼CEO田陌晨在接受电子发烧友采访时表示。

伴随着摩尔定律的放缓步伐,通过Scale up提升单处理器系统的性能和算力遭遇了“流水线过长,延迟高、布线困难”等重重困境。Scale out作为Scale up的延续,在物理层面引入了规模性互联,让“算力-互联”成为算力提升的新型抓手。研究机构IPnest预测,2025年,“片间互联技术”接口IP市占率有望超过处理器IP,成为排名第一的IP品类。那么,片内、片间、网间的互联技术未来会呈现何种特点?高性能计算体系将如何发展?就这些话题,我们采访了互联技术领域代表企业奇异摩尔CEO田陌晨先生。

片内互联:从专用到通用

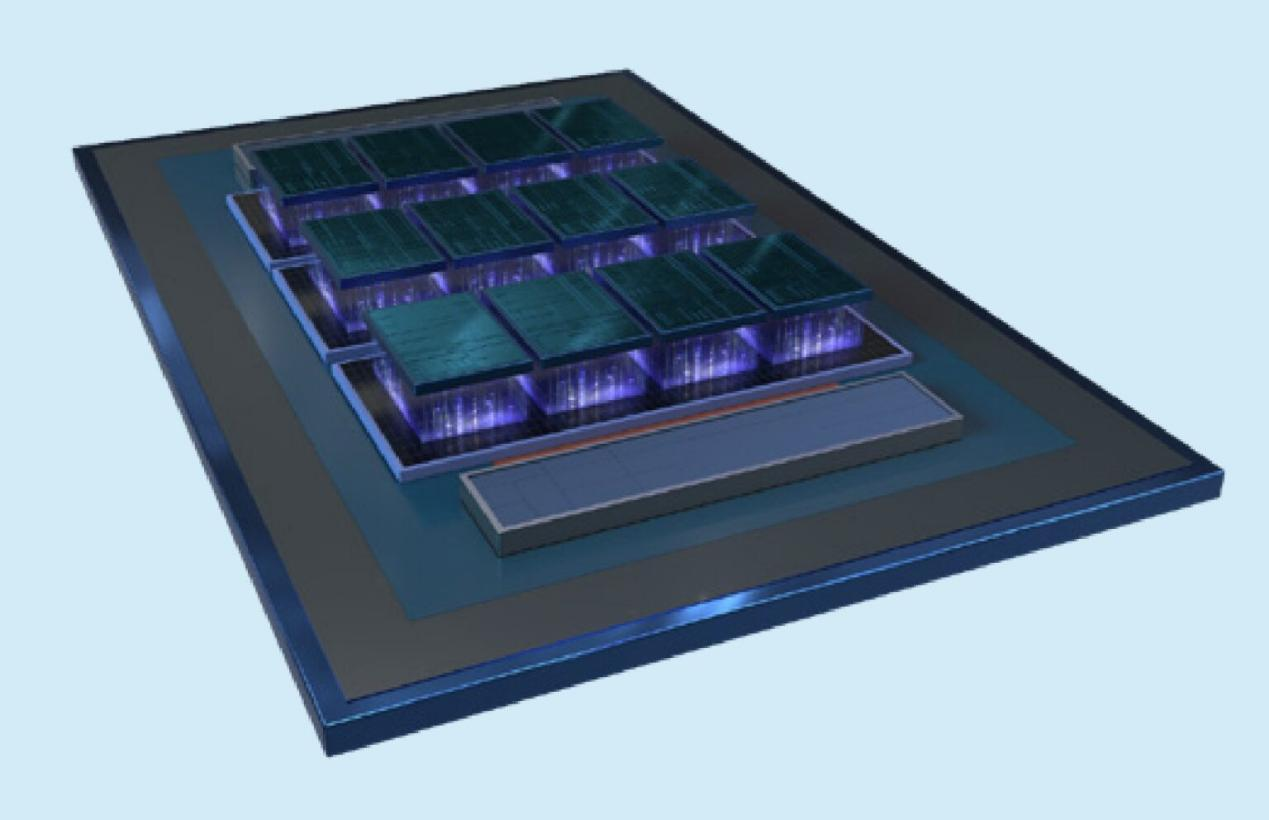

理论上,芯粒可被视作固定模块,实现不同产品、代际的复用。在智算中心集群发展中,以互联芯粒IO Die为代表的互联芯粒在提升良率、降低制造复杂度和成本等方面所显示出的优势,已成为行业发展共识。AMD的Zen系列和英特尔Clearwater Forest旗舰级数据中心处理器都是典型案例。

Intel Clearwater Forest 2

田陌晨认为,IO Die为代表的片内互联技术呈现芯粒化、3D化发展两大趋势。芯粒化是为了增进架构灵活性,降低芯片对先进工艺的依赖;3D化则是通过纵向维度进一步提升互联密度。

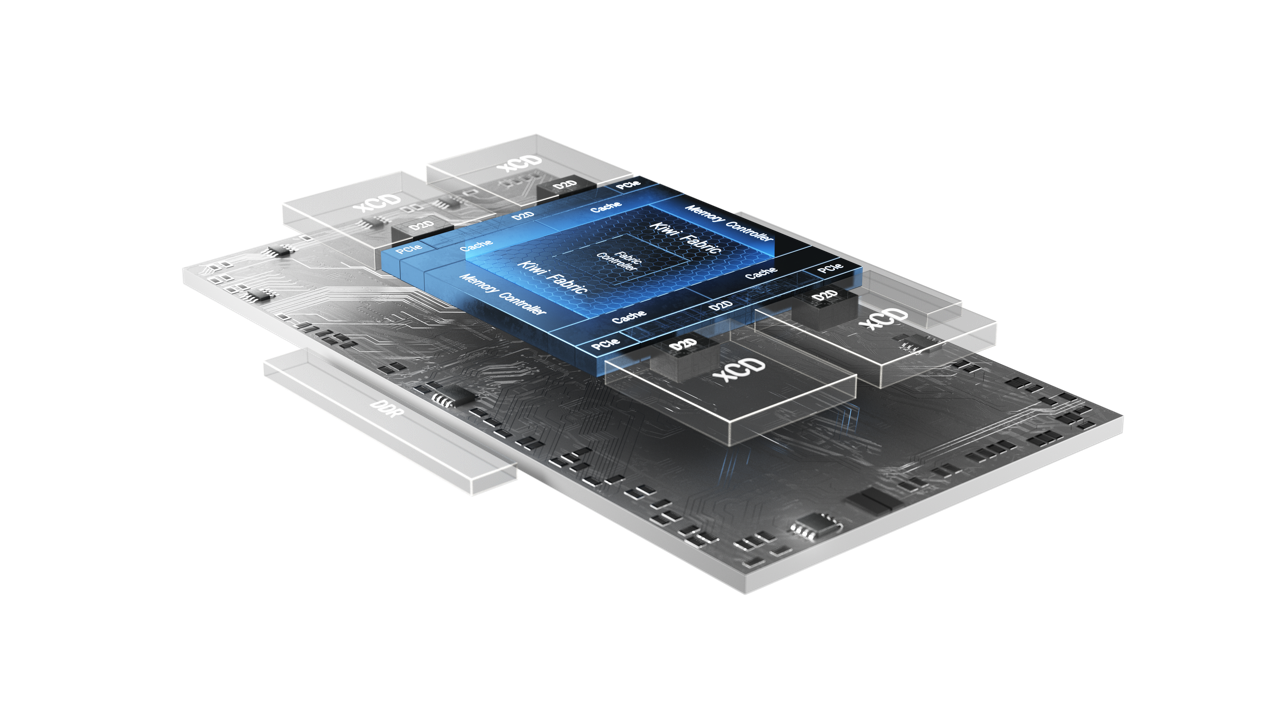

目前,市场上的IO Die主要为AMD、英特尔等大厂主导,但私有协议无法兼容不同来源的芯粒,专用IO Die的封闭生态已成为其发展掣肘。受到巨大的需求推动,通用IO芯粒开始崭露头角。以奇异摩尔旗下的通用互联芯粒 Kiwi IO Die为例,产品集成了如D2DDDRPCIeCXL等大量存储、互联接口,最高可以支持10+Chiplets,构建高达192 core CPU或1000T GPU的算力平台。

奇异摩尔通用互联芯粒 Kiwi IO Die

与其同时,受益于先进封装技术的进步,IO Die也出现了2.5D向3D的结构变化。Base Die可视为IO Die的3D形态,允许不同计算、存储芯粒的堆叠或并排放,可显著提升芯片单位面积晶体管的集成度,带来更高的带宽,更低的延迟、功耗。

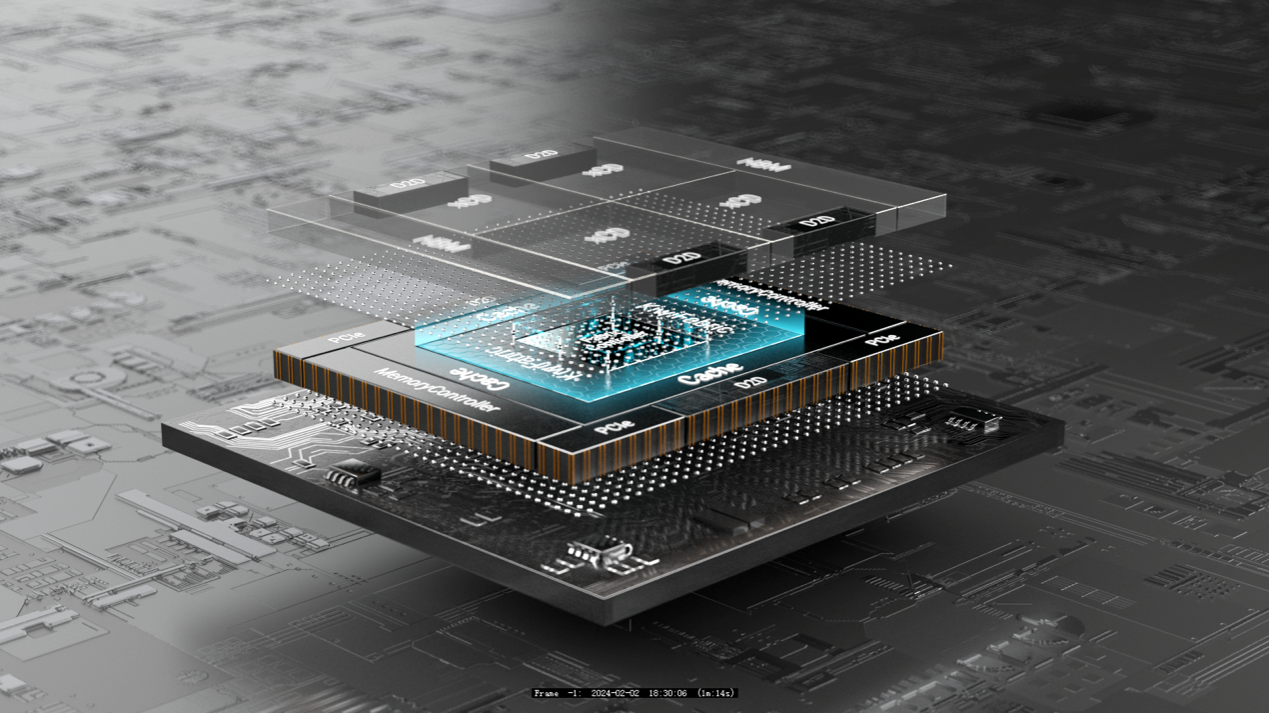

市场上Base Die的境况与IO Die类似,虽然专用产品已在市场上展现了商业化价值,但技术并未扩散,而是被少数头部企业垄断。在奇异摩尔为代表的创新企业努力下,Base Die通用市场开始起步。据田陌晨介绍,奇异摩尔旗下的通用互联底座Kiwi 3D Base Die,在3D高性能通用底座方面属全球首例,实现了通用互联芯粒在带宽、能效、搭载芯片数量等多方面的突破性进展,能够以20%的功耗实现8倍于2.5D结构的互联密度,最高可实现16颗算力芯粒堆叠。

奇异摩尔通用互联底座Kiwi 3D Base Die

IO Die和Base Die只是互联技术的两个典型的例子,说明片内互联技术如何在计算与存储之间、在庞大的智算中心和Scaling out 的浪潮中,产生对计算能力的更多助力。事实上,除了片内互联,还有许多种方法可以让更多的数据实现更高好的连接和更低的成本,比如片间互联、网间互联技术的单点到全面突破。

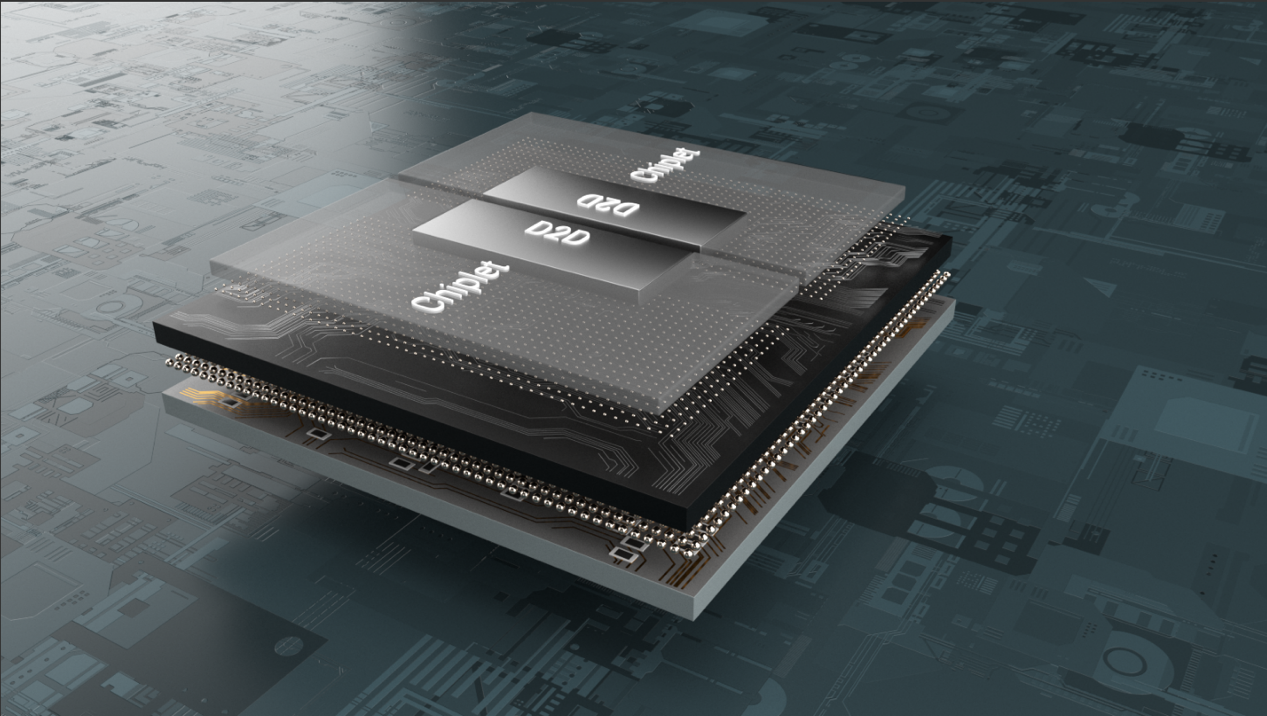

亟待加速的片间互联:D2D接口

和片内互联一样,受益于算力和突飞猛进的算力增长需求,片间互联技术亟需加速。基于Chiplet技术的Die-to-Die技术(D2D)带来了一种更高效的计算和内存的连接方式,可以看似毫不费力的将计算、存储芯粒集成在一起,在互联层面上形成一个SoC级芯片。

相比传统的计算芯片和存储芯片的互联方式,D2D提供了更高效、更低延迟的连接方式,是Chiplet实现的基础,田陌晨介绍。通过Die间通信,D2D可以实现更高的传输带宽和更高密度的集成;D2D能有效缩短数据传输的物理距离,降低延迟,提高处理速度;作为先进封装的基础,D2D可以实现计算和存储单元的无缝连接,进一步提高性能、降低功耗;基于D2D,企业可以更灵活地实现计算和存储单元的多模组配置,提高系统可扩展性、灵活性,降低系统维护成本。这些优势,使得D2D接口在高性能集群的Scaling out建设中,发挥了关键的作用。

和IO Die一样,D2D也需要通用化的大力推进。奇异摩尔基于UCIe标准,推出了全球首批支持 UCIe V1.1 的 Die2Die IP,互联速度高达32GT/s,延时低至数nS,全面支持UCIe、CXL、Streaming等主流协议,即插即用。田陌晨说,奇异摩尔所有产品都构建在国际标准协议之上,致力于使各家产品实现互联互通,构成一个开放的Chiplet系统。

奇异摩尔高速互联接口Kiwi Die2Die IP

RISC-V+Chiplet:1+1>2

如今,Chiplet之外,RISC-V架构也在大举迈进高性能计算。边缘计算市场,传统通用型MCU/MPU/CPU已经难以满足不同应用场景和性能要求,RISC-V了带来更好的PPA实现。RISC-V的本质是一个开放标准,冲击高性能运算市场是发展的必然,而二者(与Chiplet)的融合,被认为能为高性能计算市场开辟一场1+1>2的创新动力。这也是RISC-V高性能处理器的代表性企业Ventana与奇异摩尔合作的深层动因。

Ventana创始人兼CEO Balaji Baktha介绍,两家企业联手打造了一个可扩展处理器架构,可将多个Ventana Veyron V2与奇异摩尔的IO Die组成不同配置的SoC。田陌晨认为,V2与奇异摩尔IO Die的结合,是RISC-V和Chiplet在高性能计算领域融合的成功案例。

“RISC-V具备开源、开放、灵活和高度可定制特性,设计了多种用于任务加速的指令集扩展,能实现向量计算、加解密等任务加速,具有较高的计算性能,且简洁特性能降低芯片的功耗。”Balaji说,“而Chiplet是构建下一代半导体产品前进战略的重要组成部分,可以轻松构建高性能CPU。其‘可组合性’让用户以最佳比例组合计算、内存和IO,创造一个在性能、成本效益、工作负载等各方面都更为高效的系统。将RISC-V的开放式架构与 Chiplet开放式硬件设计相结合,能有效推动数据中心的工作流程效率,将单插槽性能发挥到极致。”

记者了解到,奇异摩尔和Ventana一直在努力将RISC-V和IO Die的组合推向下一代计算架构的前沿,以提高数据中心服务的效率和工作负载的效率,并共同创建了一款高性能数据中心级RISC-V处理器,其融合了RISC-V 架构和模块化的Chiplet设计的优势,每个V2单元包括32个核心,最终实现最高192个内核,这也是全球首例数据中心级的RISC-V Chiplet处理器。

回顾这次和Ventana的合作,田陌晨称,从技术互通性角度看,基于IO Die的互联,x86、ARM和RISC-V三大架构都需要采用大量存储访问和外部接口,进行大量传输、读取及调度。RISC-V和Chiplet技术融合进一步提升了计算平台的定制特性,可以避免那些对高性能运算有需求的客户被锁定在一个供应商的生态内,并助力企业应对AGI所引发的架构变革挑战,这在x86和ARM的Chiplet设计中较难实现。

当然,RISC-V和Chiplet技术融合,也伴随着如Die间通信、高性能、特定领域等多重挑战,如,为实现不同来源芯粒的通信,两家公司采取了IO Die中央设计连接CPU芯粒的方案,通过Kiwi Fabric实现了ns级的低延迟和高效的数据传输。让整个SoC在工作流的角度上,呈现独立CPU的特质。

在性能方面,为达到现有ISA(x86/ARM)设定的高性能基准,确保处理器微架构可以提供世界一流性能,双方合作的产品最高可实现192个内核。同时,通过一致性互联,让所有内核共享高性能、高速缓存和内存。

在特定领域方面,通过对计算芯粒、内存和各种加速器配比的整体规划,为各种工作负载提供灵活的硬件配置选项;在CPU中内置了端到端的RAS,确保所有总线都受到安全启动验证和级别验证等保护,同时克服侧通道攻击和其他漏洞,确保CPU芯粒和整个SoC层面的安全。

从计算加速到网络加速

从行业动态来看,高性能运算从Scale up向Scale out的转变是全方位的,在芯片设计、算力卡间、集群间无不如此。简单的说,Scale out最核心的改变就是互联。田陌晨认为,在Scale out所引发的巨量数据交互挑战背后,是加速重点从计算到网络的转变和“Bandwidth, Efficiency, Workload”互联三要素的优化需求。

在算力集群网络传输协议方面,传统协议TCP/IP存在CPU负载重、延迟高等缺点,难以满足高性能计算对网络吞吐、时延的苛刻要求。RDMA能直接通过网络接口访问内存数据,无需操作系统内核的介入,让大规模并行计算集群成为可行。计算机网络协议栈将从TCP/IP过渡到RDMA,在网络层面上,把一个集群变成一台设备。

RDMA并未规定完整的协议栈,因此包含不同的分支,如英伟达的Quantum InfiniBand是专门为RDMA设计的一种超低延迟、超高吞吐量的专用网络引擎。然而,业界需要一种更为通用化的解决方案。在性能方面可与InfiniBand匹敌的RoCE显著降低了RDMA协议通信成本,被认为能够打破英伟达在这个领域的技术垄断。

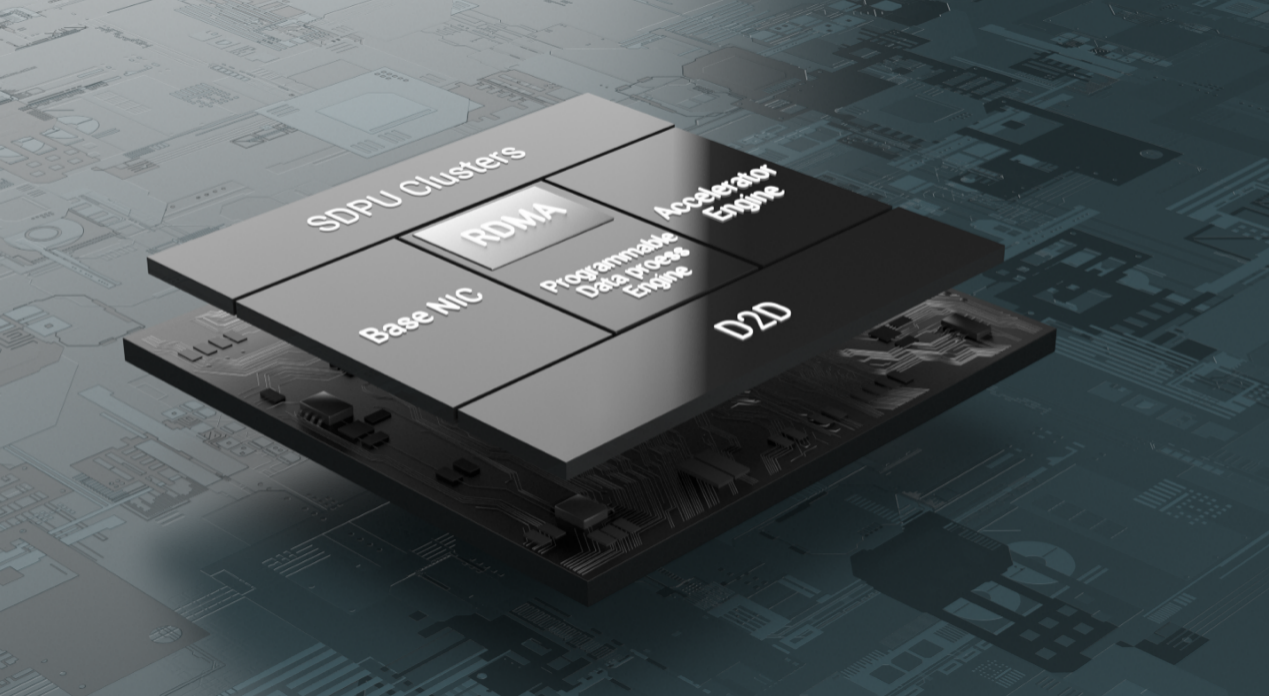

这也是奇异摩尔推出高性能网络加速芯粒Kiwi NDSA(Network Domain Specific Accelerator)系列的原因所在。据介绍,Kiwi NDSA内建RoCE V2高性能 RDMA (Remote Direct Memory Access) 和数十种卸载/加速引擎,可作为独立芯粒,实现系统不同位置的加速。Kiwi NDSA产品系列包括“NDSA-RN-F”和“NDSA-RN”。前者是全球首批200/400G的高性能FPGA RDMA网卡,将在近期面世;后者是全球首款支持800G带宽的RDMA NIC Chiplet产品,除带宽升级到800G之外,延时也降至ns级,并支持数十GB的超大规模数据包。

奇异摩尔高性能网络加速芯粒Kiwi NDSA

结语

在高性能计算体系全方位从Scale up向Scale out转变的背景下,互联技术已成为提升集群算力的新方案。以IO Die为代表的互联芯粒正在加速其通用化进程和2.5D至3D转变;片间PCIe等传统传输方式正在被低延迟、低功耗的D2D技术取代;集群互联网络则从TCP/IP转向RDMA架构,通用RDMA方案将迎来更广阔的机遇。互联技术和RISC-V架构的融合,能够助力企业更好地应对AGI所引发的架构变革挑战,帮助高性能计算领域用户实现Scale out。未来,对几乎每一家高性能计算产业链上的企业来说,互联都是一个至关重要的市场。

芯耀

芯耀

1758

1758

下载ECAD模型

下载ECAD模型