随着芯片制程不断演进,所面临的技术和成本挑战越来越大。制造过程中的材料、设备、能源等成本不断增加,而性能提升的幅度越来越小。摩尔定律被认为已逼近极限,业界开始采用异构集成、先进封装、引入新材料/新工艺等方式,来进行芯片设计制造的创新。

不过,整个行业向先进节点升级的必要性仍然存在,比如尖端的AI应用、汽车等,都需要更先进的半导体系统方案。日前,英特尔在IEDM 2023(2023 IEEE 国际电子器件会议)上展示了多项技术突破,分享了近期背面供电研发突破的扩展路径(如背面触点),并率先在同一块300毫米晶圆上,成功实现了硅晶体管与氮化镓(GaN)晶体管的大规模单片3D集成。

背面供电领域两大主要突破

根据英特尔组件研究团队的说明,背面供电和背面触点等技术有助于晶体管进一步微缩和性能提升,此外,他们还在同一晶圆上进行了不同材料晶体管的集成。随着背面供电技术的完善和新型2D通道材料的采用,英特尔致力于继续推进摩尔定律,在2030年前实现在单个封装内集成一万亿个晶体管。

首先解释一个问题:为什么要进行背面供电?在背面供电技术出现之前,计算机处理器是以层叠的方式制造的,从一层晶体管开始,然后通过添加多层金属导线进行互连。随着单位面积上的晶体管数量不断增加,这就需要更小且更多层的互连,从技术验证的角度来说,这会增加复杂性和成本。

从性能角度来看,如果没有背面供电,在每一层互连上都需要为两项功能布线,即供电和信号传输。供电需要大截面、低电阻的导线,而信号传输则需要小截面、低电容的导线,这就会导致优化上的妥协和对宝贵的互连空间的竞争,最终影响整体性能。这种情况在文献中有多种不同的描述,有时被称为互连瓶颈问题。

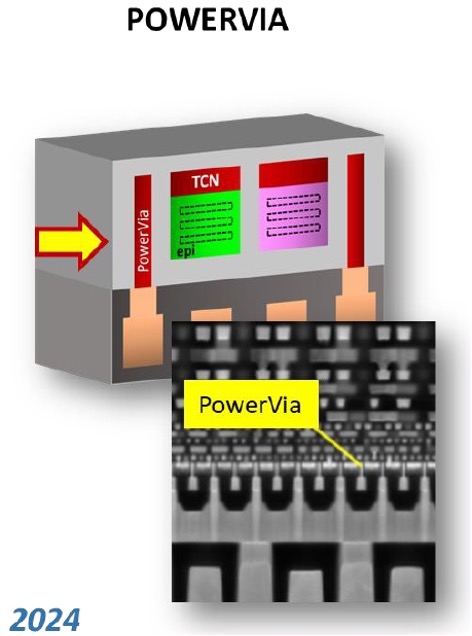

针对背面供电技术继续微缩晶体管这一方向,英特尔确定了所需的关键研发领域,当前的主要突破包括:可实现背面供电的PowerVia、背面触点等新型垂直互联技术、以及在同一块300毫米晶圆上实现了硅晶体管和氮化镓晶体管的集成。

PowerVia背面供电技术从根本上改善了这种情况,如示意图,可以看到,在晶体管两侧都实现了互连,两层互连之间通过垂直连接进行通信。在背面供电的基础上,可以将背面的互连专用于供电,将大截面、低电阻线用于背面互连线,而将正面主要用于信号传输,并对它们分别进行独立优化。

由于不再需要妥协,这将带来更多的性能提升。此外,将供电线从前面转移至背面,因此原本拥挤的前部,现在释放了更多空间。将导线分开,对降低工艺、复杂性和成本都有重要意义。

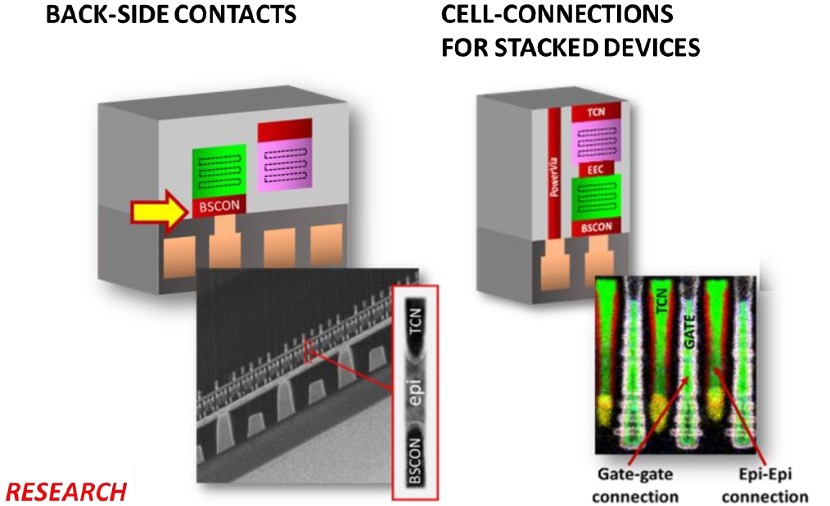

在IEDM 2023上,英特尔展示了另一种新技术,即背面触点。这一全新技术让英特尔首次拥有单一器件层,可从上面或下面,亦或在需要的时候从上下同时连接到晶体管。

它可以与 PowerVia 一起部署,也可以单独部署。从透射电子显微镜图像上可以看到,英特尔已经有能力制造出这些背面触点,并使其对称。背面触点从顶部和底部看起来非常相似,而英特尔将在 IEDM 2023上展示的电性能表现表明,这种背面触点不仅在几何形状上非常相似,而且在电性能表现上也非常相似。

背面触点有什么作用?在其帮助下,可以从背面通过大截面导线直接向晶体管供电,而不必绕路,这在供电上大大提高了性能。同时,因为没有PowerVia,单元内金属数量减少,电容及电容自旋也就随之减少,因此开关速度加快,同时功耗降低。由于不需要为PowerVia预留空间,可以将所有东西更紧密地固定在相同的区域内,这就意味着可以在单位面积内放入更多晶体管。

总之,背面触点不仅保留了背面供电技术的所有优点,还带来了更多性能或能效比方面的优势,并有助于进一步实现微缩面积。

在对背面供电这一方向的关注可以回归到晶体管堆叠所需要的两个条件:首先需要将一个晶体管放在另一个晶体管之上,其次需要将它们互连。晶体管互连必须以非常有效的方式完成,因为晶体管堆叠的主要目标之一是增加晶体管密度,在每个单位区域内放置更多晶体管,如果因为互连增加了占用面积,那么晶体管堆叠的优势也将不复存在,有可能会在实践操作过程中大打折扣。

因此,需要使用具有超低占位面积的互连技术,例如背面触点、PowerVia等等,让晶体管堆叠的意义得到有效发挥。

供电领域的材料和设备突破

IEDM 2023上,英特尔还展示了一项大规模的3D单片工艺,将氮化镓和硅CMOS集成在一起,采用了可以称之为“层转移”的工艺,在300毫米硅晶圆上完成了全部。这一被称为“DrGaN”的技术,是业界领先的CMOS驱动器与氮化镓功率器件集成技术。

早在2004年,英特尔就率先提出了DrMOS的概念,即CMOS驱动器与硅功率器件集成。这一想法最终成为个人电脑和数据中心供电的行业标准。如今,DrMOS已无处不在。

那么,为什么要将驱动器和功率器件集成在一起呢?因为这种集成提供了更高密度的解决方案,具有极低的寄生参数,因此让半导体行业可以使用硅晶体管实现更好的供电解决方案。

随着将氮化镓和硅CMOS集成在同一晶圆上的3D单片工艺终于出现,具有20倍优势的氮化镓功率器件去年也已问世,通过进行DrGaN集成,可望充分发挥氮化镓晶体管的优势,使其供电效率能够跟上未来计算功率密度和效率需求的增长。

写在最后

多年来,英特尔始终在开发能够进一步微缩互连的创新技术,其次,还有晶体管的3D堆叠来实现微缩器件,以及如何在堆叠中实现高效互连,这些都是非常系统的工程问题。

此外,工艺也是一个重要方向,就比如在供电领域的创新中,为了向单个封装提供48伏的电力,英特尔聚焦GaN工艺开辟了一条独特的路径,英特尔正专注于氮化镓的低电压技术,特别是48伏及以下。

2634

2634

下载ECAD模型

下载ECAD模型