1.1 Timing Arc概念

在时序工具对设计进行时序分析时,经常会看到一个概念Timing Arch(时序弧)。Timing Arc是一个信号一个单元Cell的输入引脚Pin到该单元输出引脚Output Pin间的路径。对于一个单元Cell,可以存在多个时序弧,通过时序弧的信息,我们可以计算每一段路径的时延从而进行时序分析以及优化。

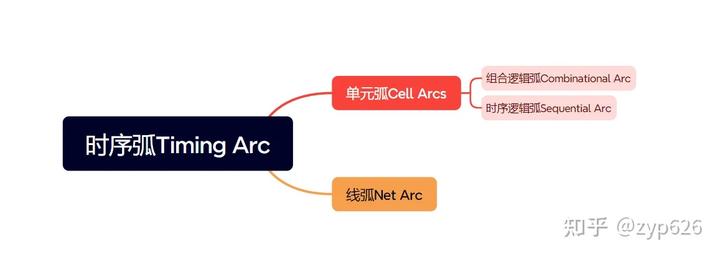

1.2 Timing Arcs的类型

时序弧分为单元弧Cell Arc和线弧Net Arc,单元弧有分为组合逻辑弧和时序逻辑弧

组合逻辑弧:信号从组合逻辑单元的输入引脚到输出引脚的路径

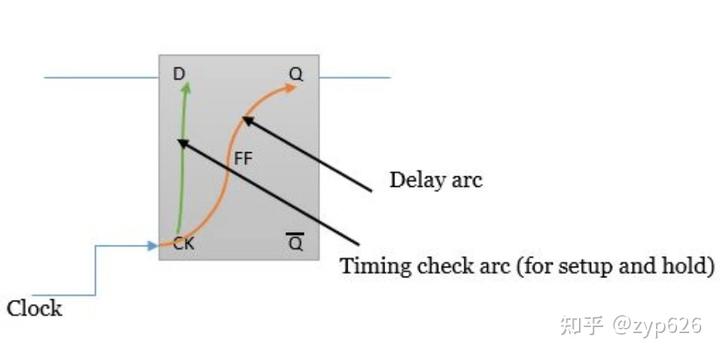

时序逻辑弧:信号从时序逻辑单元(如触发器FF和锁存器Latch)的时钟输入引脚Clock Pin到输出引脚,或者是时钟输入引脚到时序单元的其他输入引脚,下图中ck到D之间的时序弧即是用于setup、hold分析,CK到Q的路径为时序单元内部的传输时延。

线弧:一个单元的输出引脚到另一个单元输入引脚之间的路径即为线弧Net Arcs,线弧引起信号在时序路径中的Net中存在传输时延。

1.3Timing Sense(时序感知)

Timing Sense时序感知是时序弧中源引脚到目的引脚的边沿传输变换,可以分为三类:Positive unate,Negative unate和Non unate,Timing Sense也可称为Unateness(单边性)。

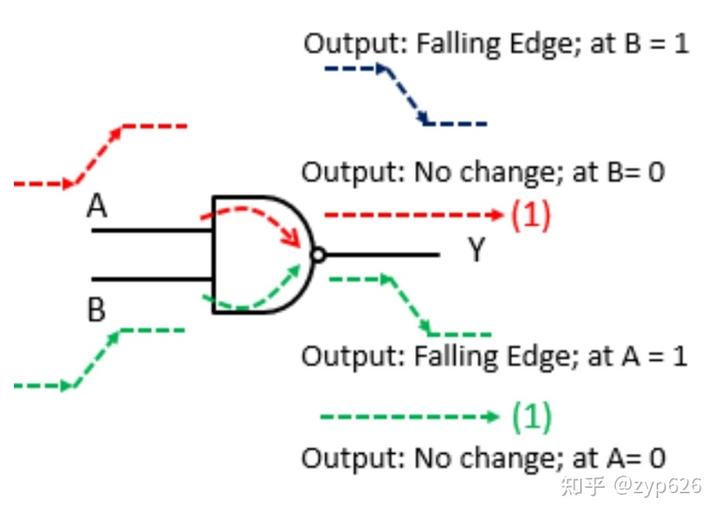

Positive unate arc: 如果源引脚的上升沿切换能引起目的引脚的上升沿切换,则该段弧即为正级弧。如AND与门单元,OR或门单元,缓冲器BUFFER以及所有的Net arc都属于Positive Unate arcs。

以AND门为例,AND逻辑门真值表如下图

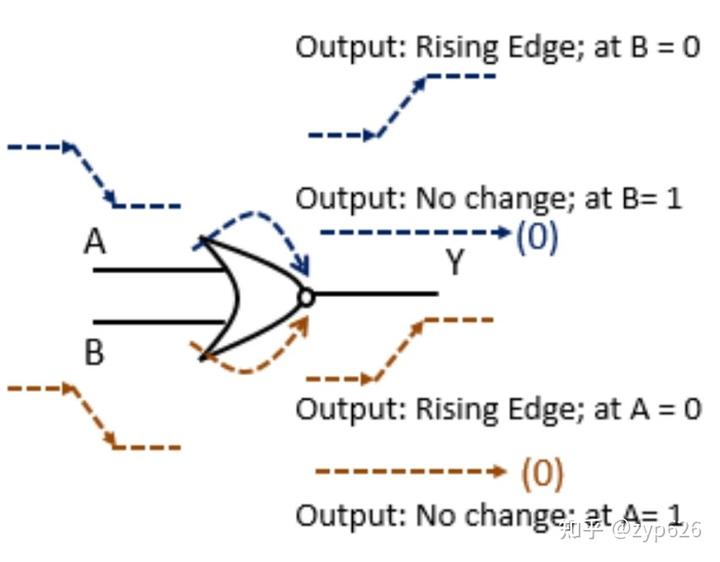

分析如下:

A=0,B为0-》1时,输出Y不会变化,一直为0

A=1,B为0-》1时,输出也是上升沿切换

B=0,A为0-》1时,输出Y不会变化,一直为0

B=1,A为0-》1时,输出也是上升沿切换

上升沿切换图如下

下降沿切换如下图

因此,AND存在4个时序弧:上升沿时,输入引脚A,引脚B到输出Y,下降沿时输入引脚A,引脚B到输出Y.

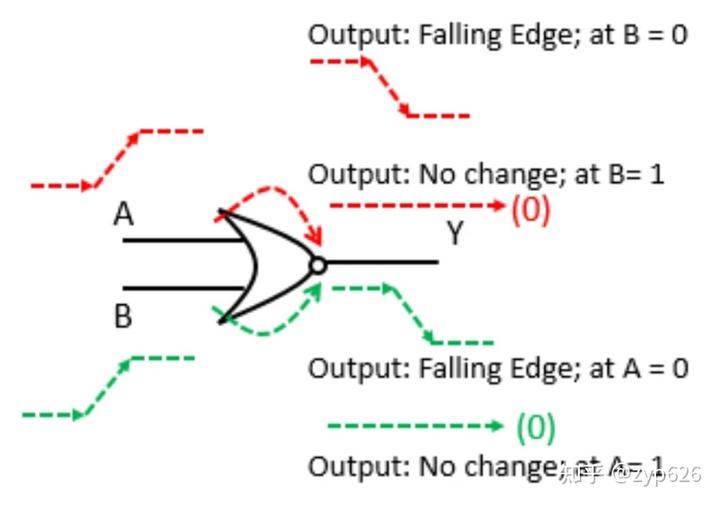

Negative unate arc:如果源引脚的上升沿切换能引起目的引脚的下降沿切换,则该段弧即为负级弧。如NAND与非门单元,NOR或非门单元以及反相器都属于Negative Unate arcs。

以或非门为例,真值表如下图

分析如下

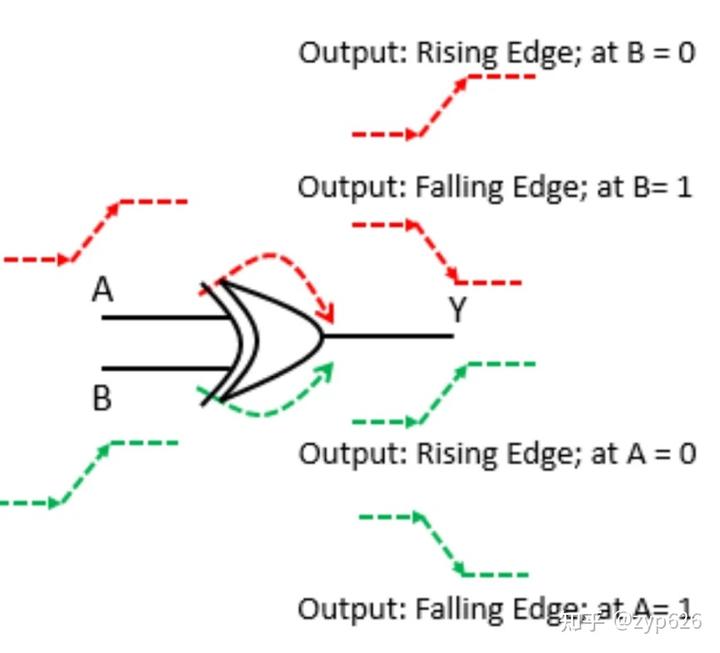

A=0,B为0-》1时,输出Y下降沿切换

A=1,B为0-》1时,输出Y不变,为0

B=0,A为0-》1时,输出Y下降沿变换

B=1,A为0-》1时,输出Y不变,为0

上升沿切换如下

下降沿切换如下

同样地,NOR存在4个时序弧:上升沿时,输入引脚A,引脚B到输出Y,下降沿时输入引脚A,引脚B到输出Y,和Positive unate arc不同的是输出边沿切换与输入相反。

Non Unate arc:如果源引脚的边沿切换与目的引脚的边沿切换无相同或相反的关系,则该段弧即为Non-unate时序弧。如XOR异或门单元

异或门的真值表如下图

分析如下:

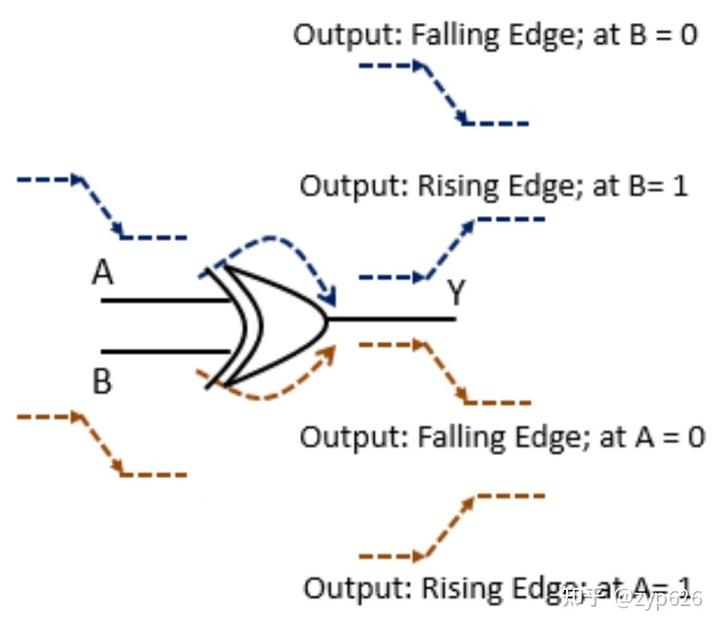

A=0,B为0-》1时,输出Y上升沿变换

A=1,B为0-》1时,输出Y下降沿变换

B=0,A为0-》1时,输出Y上升沿变换

B=1,A为0-》1时,输出Y下降沿变换

上升沿切换图如下图

下降沿变换图

通过这种变化关系,可以知道输出的边沿变换无法仅仅看一个输入引脚的变换。对于B上升沿的切换,输出Y还和输入A有关,A的值会影响输出Y是同边沿还是反边沿切换

1.4 参考资料

https://www.vlsi-expert.com4

芯耀

芯耀

2575

2575

下载ECAD模型

下载ECAD模型