EDA是集成电路设计工业软件,应用于芯片的设计、制造、封测、封装等多个环节,承担着电路设计、电路验证和性能分析等多项芯片开发过程中的核心工作,可以说是半导体产业的根基。作为关键基础软件,我国EDA的发展不仅需要解决关键受限问题,也需要形成技术优势,从而打造新一代的世界级工业软件。

在这些趋势和机遇下,国产EDA企业逐渐崭露头角。上海合见工业软件集团有限公司作为其中的一员,定位于自主创新的高性能工业软件及解决方案提供商,以EDA为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题。成立两年多以来,合见工软从数字验证EDA产品率先切入市场,陆续推出了自主自研的数字功能仿真器UniVista Simulator(UVS)、数字仿真调试器UniVista Debugger(UVD)、验证回归管理平台UniVista Verification Productivity System(VPS)、原型验证系统UniVista Advanced Prototyping System(UV APS)、以及先进封装系统级设计协同Sign-off工具 UniVista Integrator (UVI)等主流EDA工具,获得了上百家客户的部署与认可。日前,合见工软发布了五款覆盖系统、IP、实现、验证和芯粒/封装/PCB的全新EDA工具,并接受了<与非网>等媒体采访。

国产EDA为什么要打造全流程工具链?

当前,我国EDA产业发展正处于关键阶段,一方面,市场需求日益旺盛,国内比较有规模的芯片设计公司在快速成长,年复合增长率超过28%;另一方面,国产EDA软件的发展速度有了显著提升,中国EDA市场年复合增长率为14.7%,超过了全球EDA市场的增长速度(年复合增长率10.9%)。

尽管机遇空前,但国产EDA面临的挑战也是巨大的。合见工软CTO贺培鑫认为,首先是技术壁垒高、投入大;二是世界级的领军人物、技术人才难觅;三是国内的EDA公司现在多数在做单点工具(point-tool),很少能够做出全流程的工具链,并且,国内公司大部分都缺乏并购经验、以及产业上下游生态建构的经验。

应对上述挑战,贺培鑫表示,首先要不断保持技术创新,才能真正解决受限问题,这需要不断引入国际知名专家,培养国内一流的人才梯队。其次要构筑整个生态,不光是芯片,还有芯片上下游的系统、封装、PCB等,要能够做到协同设计,并且要确保整个设计的flow可以收敛(converge)。合见工软致力于打造全流程的工具链,并且会持续通过并购和整合发展壮大。

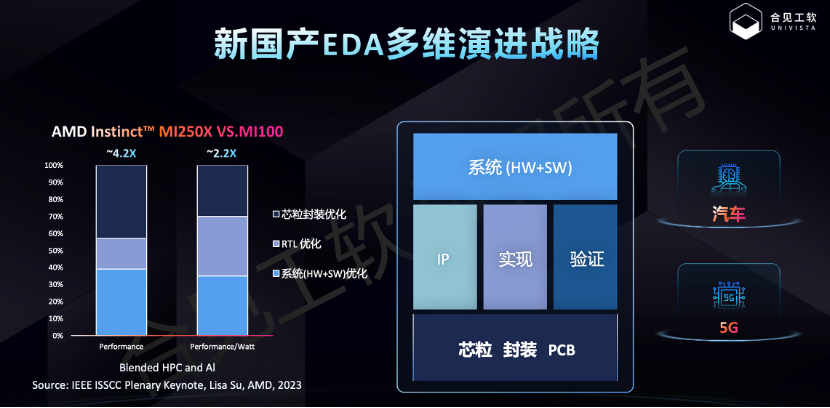

“之所以要打造全流程的工具链,是因为点工具很难把整个流程都做起来,难以实现收敛、协同优化。而如果做不出全流程的工具链,就没有办法真正地解决受限的问题”, 贺培鑫解释说,“也正是在这样的背景下,合见工软明确了‘国产EDA多维演进’的产品战略。”

新趋势下软硬件协同优化的必要性

现代电子系统设计中,不论是AI、超级计算还是汽车、5G电子系统,都需要首先进行系统设计,不仅包括芯片,还包括整机系统和软件,这涉及到IP选择、数字实现、RTL code转化等,然后才能送至代工厂制成芯片。

这其中首先需要确保IC实现的功能是正确的。由于IC越来越复杂,设计和生产中的任何错误都可能导致IC无法工作。因此,验证成为非常重要的环节,甚至在芯片设计过程中,验证所花费的时间和费用可能超过设计实现和IP选择。

此外,在IC设计中使用不同的芯粒(chiplet)越来越成为显著趋势。由于芯粒之间的通信协议会对整个系统的性能和能耗比产生重大影响,因此需要对可能产生的问题进行提前预测。

AMD的MI100加速器芯片就体现了软硬件协同优化所带来的巨大优势。相关数据显示,与上一代MI250X相比,MI100取得了4.2倍的性能提升和2.2倍的能效提升,但这些提升并不是从更先进的制程工艺得来的,而是通过系统优化、RTL优化、芯粒封装优化获得,这与合见工软的策略不谋而合。

多维演进战略:系统、IP、实现、验证和芯粒/封装/PCB的全面覆盖

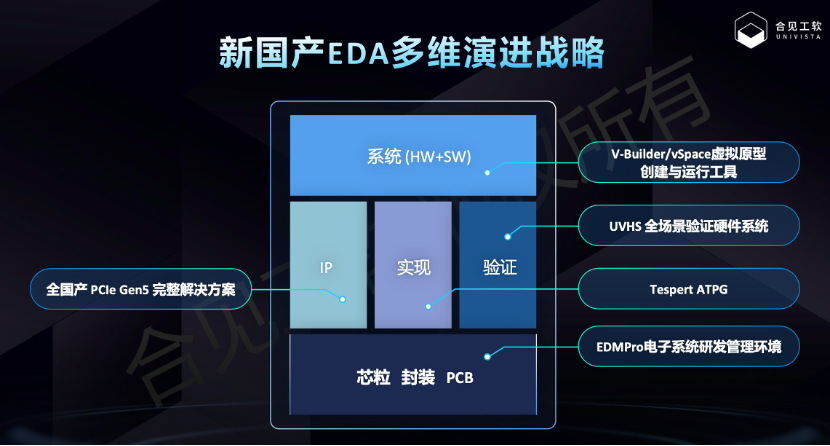

合见工软最新发布的五款基于“多维演进战略”的EDA工具分别覆盖五个维度:系统、IP、实现、验证和芯粒/封装/PCB,再结合三款在售的EDA工具:UVS/UVD(数字仿真器/调试器)、UVAPS(原型验证系统),以及UVI(先进封装互连检查工具),这五大维度进一步得到了提升和全面覆盖。

1、测试向量自动生成工具,大幅加速集成电路测试

UniVista Tespert ATPG是合见工软最新推出的商用级、高效测试向量自动生成工具,拥有自主知识产权,该工具创新自研了多线程并行引擎,相比传统单线程引擎,可以利用48线程实现高达29倍的提速,同时配合高效的测试向量生成算法,提高了最终测试向量的有效性和高故障覆盖率。同时,UniVista Tespert ATPG支持基于时序逻辑的硬件压缩,相比于传统的组合逻辑的压缩结构,具备更高压缩比,可以帮助测试工程师解决越来越严峻的芯片“大”规模、“少”管脚带来的挑战,大幅降低测试时间和成本。

集成电路的测试是整个集成电路设计和生产过程中不可或缺的核心环节,高品质、低成本的测试是保证芯片质量的关键,也是获得商业成功的重要保障,而高效的测试向量自动生成工具(ATPG)则是获得最优测试的必要保证。数据显示,在可测试设计(DFT)中,项目调试的时间占整个设计验证周期的50%以上。

UniVista Tespert ATPG在提高测试效率和测试质量的同时,还可以与合见工软自研的数字功能仿真调试工具UniVista Debugger无缝集成,提供功能强大、直观易用的图形界面,加快用户定位和分析出包括设计规则违例、低测试覆盖率和仿真mismatch的根本原因。此外,UniVista Tespert ATPG Debugger支持千兆门级规模设计,并具有较低的响应延时,可以从网表、电路图和层次结构树中查找和追踪对象,可大幅加速达到十数倍。

对于该公司在数字芯片实现领域推出首款产品的重要意义,以及在整个数字芯片设计实现流程中所扮演的重要角色,合见工软副总裁敬伟表示,“从设计开发到量产的过程中,DFT(Design For Test;可测试性设计)是最关键的环节,随着芯片规模越来越大,工艺越来越先进,成本、良率和缺陷率成为关注焦点,DFT成为提高芯片量产竞争力的重要手段之一。而量产竞争力主要体现在两个方面:一是如何降低测试成本(测试成本占芯片成品成本的20%以上),二是如何降低产品缺陷率,这是DFT的两大关注点。”

由于降低测试成本和提高测试覆盖率是芯片设计的重要目标,这需要借助DFT在ATPG方面的实力。对于几亿门级的大型芯片,可测性设计规则的违反、覆盖率缺陷或测试向量不匹配等问题,会使调试变得异常困难。为解决这些问题,UniVista Tespert ATPG提供强大的调试引擎和数字仿真调试器UVD,可在数亿门的电路网表上快速定位各种规则、故障、缺陷、仿真不匹配等问题。

敬伟强调,UniVista Tespert ATPG的自动测试向量生成引擎内核采用了自研的高性能并行计算技术,可以在48个线程上实现接近30倍的提速,同时保持非常低的内存占用率,在这方面,我们拥有业界领先的水平,这是在过去十多个客户测试项目上得到了充分验证的结果。

2、商用级全场景验证硬件系统,加速大芯片设计软硬件协同开发

商用级、高性能、全场景验证硬件系统(Unified Verification Hardware System, UVHS)的推出,与近年来智能驾驶、数据中心、人工智能等大规模芯片应用不断涌现,芯片公司的设计与验证团队持续面临的复杂多样性的挑战息息相关,而这主要是设计规模和功能集成度所带来的仿真性能和验证任务挑战。

对于芯片公司而言,一方面,急需解决数十亿门规模以上的设计如何在系统软硬件验证阶段,通过几周到一个月的时间,快速实现设计启动,并获取10MHz以上的仿真性能,从而在有效的时间内执行完软硬件协同调试任务;另一方面,也渴望更早开始以更快的速度执行更为复杂的应用软件,例如20MHz以上甚至高达100MHz,以进行更为广泛的系统测试和量产软件开发。

敬伟表示,“芯机联动”概念日益得到认可,其背后的逻辑就是在强调“芯片公司如何与整机设计公司进行充分的联动”,尤其是在当前“软件定义网络”、“软件定义汽车”流行的时代,复杂的工具如何帮助用户构建最好的芯片架构,以确保最终的产品符合预期,需要在更早的阶段去做充分的验证。

UVHS以全国产自研的硬件系统设计与核心EDA工具链,成功实现了单一系统可以根据验证任务的不同,在不同性能要求、接口方案的使用模式和应用场景之间进行灵活切换以及设计数据与环境的平滑移植,轻松解决了其他已有方案里切换模式的跨度大、难度高、效率低、时间久的难题。目前,该产品已在多家客户的主流大芯片项目中成功完成单一设计超过60亿门设计规模的实际商业化部署,并实现成功流片迭代。

中兴微电子有线系统部部长贺志强在评价这款新工具时谈到,合见工软的高性能原型验证平台UV APS已在中兴通讯的多个项目中得到成功部署,而最新推出的高效能的全场景验证硬件系统UVHS,为其软硬件协同验证方面所面临的性能和调试挑战提供了一个优异的解决方案。

他解释说,因为在项目中,他们经常会在硬件加速器上执行一些长软件测试用例,所以运行性能和快速定位问题的能力是必须要求。UVHS的高效定位调试功能非常有用,结合全信号可见能力,能够助其迅速找到问题根源。

3、商用级虚拟原型工具套件,提升软硬件协同开发效率

一个完整的电子系统级解决方案通常包括芯片本身和运行在芯片上的软件,软件的开发和测试需要依赖硬件环境,而随着系统对软件需求的不断增长,软件开发现已成为芯片开发过程中最耗费时间和资源的环节之一,需要尽可能的在芯片开发周期中让软件的开发测试工作提前开始,不再依赖于芯片硬件的开发状态,通过软硬件协同以并行开发,加速产品整体开发的进度。

为此,创新的商用级虚拟原型设计仿真平台UniVista V-Builder/vSpace在性能方面,能够支持分钟级快速原型创建与平台编译,典型系统运行性可达10-100MIPS;支持第三方调试器扩展,支持命令行界面、故障注入及自动化回归测试;支持仿真与软件Profiling等用户友好功能,可以更好地解决日益增长的系统复杂度与更短的产品上市时间之间的矛盾,

此外,UniVista V-Builder/vSpace还可以与其他工具组成混合仿真环境,包括在汽车电子行业中的在环测试中,与Simulink构成物理模型组建混仿平台,支持用户进行虚拟在环测试;与硬件仿真器组成混合仿真平台,有效解决硬件仿真的容量及编译性能限制等问题,通过支撑项目从RTL早期IP级、子系统级、到SoC级完整生命周期的验证平台创建;以及支持与虚拟机设备(VirtualBox)构建主机(x86)与PCIe板卡(虚拟原型)连接,帮助调试主机侧驱动以及整体软件流程。

燧原科技验证平台负责人任承志在介绍合见工软对大算力平台的支持时谈到,“虚拟原型技术通过将软硬件集成开发验证左移、以及灵活易用的快速部署特点,当前已证明为燧原科技产品高质量高效率交付提供可靠的流程保障。我们与合见工软的专家团队深度合作,在项目设计中选用UniVista V-Builder/vSpace工具套件,它可以支持用户自研标准TLM模型导入,同时在第三方处理器模型集成、支持PCIe SR-IOV、多线程仿真加速等多个关键技术点上可以提供业界一流的解决方案。我们很高兴能够看到国产自主知识产权的虚拟化仿真方案能支持燧原科技的云端算力产品进一步演进。”

4、首款自研全国产PCIe Gen5 IP解决方案,应对更复杂应用需求

UniVista PCIe Gen5 IP解决方案的推出,是基于合见工软2023年5月对北京诺芮集成电路公司的收购。据了解,诺芮集成电路主要提供已经硬件验证过的Ethernet、FlexE、Interlaken等多款IP产品,包括成熟可靠支持多协议的全国产400G/800G以太网控制器UniVista Ethernet Controller IP,支持完整FlexE应用和小粒度协议的全国产灵活以太网解决方案UniVista Flexible Ethernet IP,以及全国产高带宽低延迟Interlaken PHY层编解码控制器UniVista Interlaken Controller IP。

UniVista PCIe Gen5 IP包含了32G PHY、PIPE、DL、TL、DMA、AXI接口等全功能 PCIe接口解决方案,支持RP和EP,以及X1至X16等等多种配置及模式,数据传输速率最高达512Gbps,功耗350mw/lane,性能处于业界领先水平。

合见工软IP事业部总经理刘矛认为,随着设计复杂度的提升,EDA和IP的互动正变得越来越紧密,尤其是在HPC领域,客户在设计芯片的时候也会更多考虑“EDA+IP+定制化”的完整方案。因此要想做到行业领先,IP策略必不可少,这也是为什么合见工软选择收购诺芮的原因,希望能够加强IP设计能力,扩展IP产品线,提供更完整的解决方案,实现1+1>2的化学反应。未来,合见工软将继续关注IP领域新产品,扩展EDA+IP的产品策略。

5、新一代UniVista EDMPro电子系统研发管理平台

随着5G、AI、自动驾驶等技术的发展,电子系统已经越来越复杂,研发过程中的各类型管理问题也日显突出。例如,如何让设计团队使用统一、规范化的资源库?设计过程中的数据如何进行管理和版本控制?设计的阶段性成果如何进行评审和问题闭环?如何快速进行设计规则的自动化检查,及时发现和解决质量问题?都是目前设计工程师遇到的重点挑战。

为此,在前一代电子数据管理平台EDMPro的基础上,合见工软在新一代版本的多个组件上进行了技术创新与迭代。其中,新版本EDMPro ERC电子设计自动化检查系统采用全新的技术,具备了规则的自定义、多线程检查的能力,从而提升了规则执行效率,创新性的EDA工具协同方式支持多场景、多设计高效切换;新版本EDMPro ERC电子设计自动化检查系统与EDMPro ERS电子设计评审系统能够无缝对接,支持自动提问,检查结果闭环管理,有效提升了设计质量,提高了工作效率。

中兴通讯EDA经理储明聚表示:“UniVista EDMPro系列产品在针对目前电子设计管理问题,带来积极作用,如RMS对资源库的管理,有助于设计师更方便的选择需要的器件;ERS目前已经使用在一些项目上,问题提取、定位比之前要更加方便,基于线上的问题闭环管理,可以很直接地了解所有问题状态,掌握评审进度;结构化数据管理,对后续改善产品质量、提升设计能力都有参考意义。ERC的自动化检查也将提升我们在检查规则检查的效率,部署UniVista EDMPro平台,令我们的工程师能更专注在设计、创新上。”

“一群正确的人在正确的时间做了正确的事情”

对于合见工软在短短两年多时间内取得的成果,上海集成电路行业协会会长、华虹集团董事长张素心的评价是:一群正确的人在正确的时间做了正确的事情。

如何在短时间内迅速发展壮大、并推出经得起市场验证的产品?合见工软联席总裁徐昀表示,核心团队在创立之初就明确了平台化的发展思路,这对于公司的快速发展起到了关键作用。目前,合见工软已经成功实现了平台化发展,并购整合非常成功,多维产品在顺利推出,并且客户反馈良好。

此外,也得益于双轮驱动的企业发展策略和整体思路的构建。她解释说,所谓“双轮”, 首先是人才,国内很缺少国际顶级的专家团队,而合见工软吸引了国际技术职位的核心人才加入,并通过人才的虹吸效应,吸引了更多优秀人才;其次是商业落地能力,合见工软的运营团队具备卓越的商业落地能力,成员大多来自国际领先EDA企业,有着丰富的服务国内客户的经验,赢得了客户的信任和支持。

目前,合见工软也完成了对几家技术领先的EDA初创公司的投资和合并。验证方面,成功并购了上海华桑电子,并迅速融入合见工软验证EDA产品运营体系,大大加速了验证硬件类产品的上市过程;系统级方面,成功并购了北京云枢软件,大大加速了PCB解决方案的产品化进程以及国内头部整机企业的商业推广进程;IP方面,今年上半年完成了对北京诺芮的收购,成功进入设计IP市场,诺芮的controller IP与合见工软的验证、DFT和其他系统级想法互补,形成全面的战略布局。

对于当前的业务布局和未来发展,徐昀表示,虽然合见工软是初创公司,但是从营收、客户积累、行业口碑等方面来看,已经收获了不少认可,团队信心也非常足,要成为具备世界竞争力的领先EDA企业。“虽然离完美还有很大的差距,但是在正确的方向前进且进展迅速,我们正处在很好的一个机会点”,她补充。

来源: 与非网,作者: 张慧娟,原文链接: https://www.eefocus.com/article/1631945.html

芯耀

芯耀

1705

1705

下载ECAD模型

下载ECAD模型