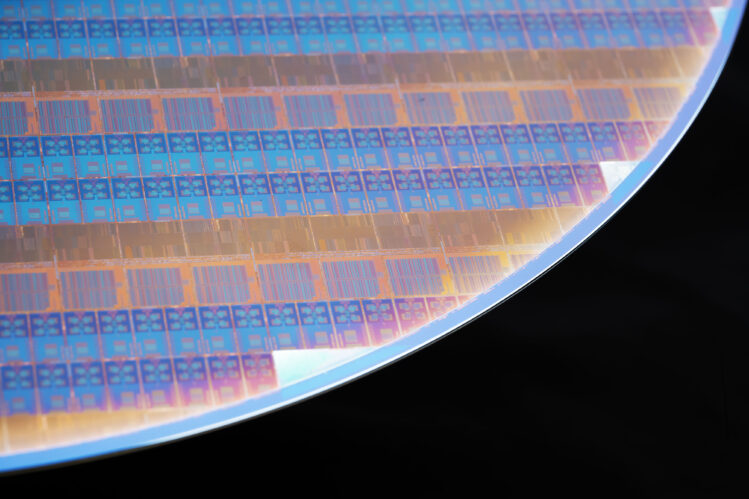

在现有的晶片互联架构下,电源跟讯号线路都集中在晶片正面,导致晶片正面变得异常拥挤,也不利于缩小晶片尺寸。为此,半导体业界一直在探索将电源分配网路(Power Distribution Network, PDN)转移到晶片背面可行性,以解决线路拥塞的问题。英特尔(Intel)近日宣布,该公司在晶背供电(Backside Power Delivery)领域取得重要突破,并成为业界第一家在类产品(Product-like)的测试晶片上实作晶背供电的公司。英特尔预计将在2024年量产的20A製程节点为晶圆代工服务的客户提供此一技术选项。

英特尔开发代号为Blue Sky Creek的测试晶片为业界首次在类似真实晶片上实作晶背供电的成功案例,此一突破解决数十年来的互连瓶颈,预计将于2024年成为Intel 20A製程节点的其中一部份

英特尔技术开发副总裁Ben Sell指出,PowerVia是英特尔「4年5个节点」策略以及迈向2030年达成单一封装内含1兆个电晶体过程中的重要里程碑。使用试验性的製程节点及随后的测试晶片,让英特尔降低晶背供电对于领先製程节点的风险,并让英特尔在晶背供电导入市场方面,领先竞争对手一个节点世代。

英特尔将PowerVia从电晶体的开发中分离出来,以确保实作于Intel 20A和Intel 18A製程节点晶片时,该技术已准备就绪。与Intel 20A的RibbonFET整合之前,PowerVia已在其内部测试节点进行测试和除错,确认该技术具备良好的功能性。製造该测试晶片并测试之后,PowerVia已被证实能够显著且有效地利用晶片资源,单元利用率超过90%,让晶片设计人员能够在产品中提升效能和效率。英特尔将于6月11日至16日在日本京都举行的VLSI研讨会上,发表两篇论文来介绍这些技术。

PowerVia为晶片设计人员首次解决日益严重的互连瓶颈问题。随著人工智慧和电脑图形在内等领域的应用不断增加,需要更小、更密集和更强大的电晶体来满足不断成长中的运算要求。过去数十年来直至今日,连接电晶体的电源线和讯号线架构总是在争夺相同的资源。藉由分离这两者,能够提升晶片的效能和能源效率,为客户提供更好的结果。晶背供电对于电晶体微缩十分重要,让晶片设计人员能够在毋须牺牲资源的情况下提升电晶体密度,提供相较过往更高的功率和效率。

Intel 20A和Intel 18A均会导入PowerVia晶背供电技术和RibbonFET环绕式闸极技术。作为一款全新的电晶体电源传输方式,晶背供电实作也向散热和除错设计提出新的挑战。英特尔工程师开发出避免散热问题的缓和技术,除错小组也发展出新技术,确保新款设计结构能够被正确除错。实作测试的结果显示出稳定的良率和可靠性指标,于整合RibbonFET架构之前就展现出该技术优秀的内在价值。

该测试还利用极紫外光(EUV)微影的设计规则,其结果包含在晶片大面积上达成超过90%的标准单元利用率,提升单元密度同时降低成本。本测试还显示出平台电压下降幅度改善超过30%以及6%的频率优势。英特尔也迎合逻辑单元微缩随之而来的高功率密度,在PowerVia测试晶片达成所需散热特性。

于VLSI举行期间公开的第三篇论文,英特尔技术专家Mauro Kobrinsky将解释英特尔对于部署更先进PowerVia方法的研究,例如在晶圆的正面或背面同时实现讯号和电源传输。

芯耀

芯耀

1922

1922

下载ECAD模型

下载ECAD模型

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

-1.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

-1-%E5%89%AF%E6%9C%AC.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍