先进封装技术的进步,让IC设计者得以将系统单晶片(SoC)裡整合的各种功能分拆成小晶片(Chiplet),再藉由封装技术将其整合成一颗元件。许多大厂都在近几年大力拥抱这种异质整合式的晶片设计概念,并在近几年陆续将其运用在自家产品上,因而让Chiplet成为半导体业内的热门关键字之一。

但异质整合概念的风行,也让半导体产业必须有所调整。异质整合在理论上打破了晶片开发者必须包办所有设计整合工作的局面,一颗晶片裡可以包含来自不同供应商的Chiplet,但事实上目前这种跨供应商合作的案例仍非常罕见。

Chiplet成大势所趋 壁垒依然存在

研究机构TechSearch总裁Jan Vardaman指出,Chiplet不仅让IC设计者可以更灵活地实现自己想要设计的晶片,同时也让晶片製造的成本变得更便宜。因为不同功能电路可选用最具性价比的製程技术来生产,不必全部採用最先进製程。

由于Chiplet可以带来更高的灵活性与更好的成本结构,近几年市场上出现许多採用Chiplet架构的元件。但目前市场上的Chiplet产品,是各家大厂自行发展出来的成果,故目前半导体业内存在多种不相通的Chiplet互连技术,导致Chiplet生态系呈现碎片化的局面。

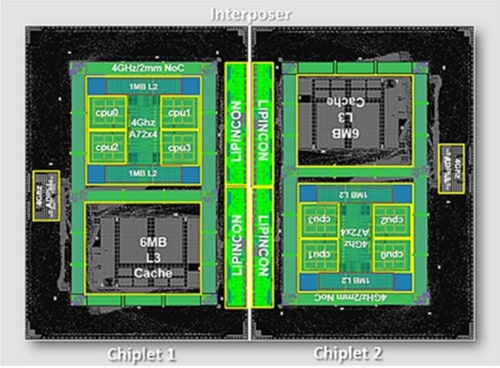

事实上,为了实现基于Chiplet的晶片设计,许多领导大厂都已经投入可观资源来研发必要的底层技术。以Chiplet的互联为例,超微(AMD)就已经自行发展出名为Infinity Fabirc的独家技术,台积电也有自行研发的LIPINCON介面技术(图1)。虽然这些大厂同时也都是UCIe标准的支持者与发起者,但这些业者会放弃辛苦累积的独特技术,全面转向开放标准吗?Vardaman对此持相对保留的态度。

图1 台积电与Arm联合展示藉由LIPINCON介面连接,採用Chiplet架构的处理器SoC

除了大厂自行研发的独特技术外,其实业界很早就看出,Chiplet互联的标准化将是推动异质整合向前迈进的关键,因此在UCIe问世之前,就已经有Open Domain- Specific Architecture(OSDA)、Bunch of Wires(BoW)这些开放标准存在,只是这些开放标准不像UCIe,几乎获得所有大厂的一致支持。

因此,Vardaman认为,以打破藩篱为诉求的UCIe标准,是Chiplet生态系一个重要的发展里程碑,但不会是所有问题的解答。

产学强化交流方能协助Chiplet人才培育

除了大厂已经投入研发的技术资产该如何继续运用外,由大厂带头攻坚的异质整合,相关技术经验该如何向外扩散到学术界,让学界可以早日展开相关人才培育工作,也是攸关异质整合未来发展的大事。

日月光院士既资深技术顾问William Chen(Bill)就指出,要进一步推动Chiplet生态系发展的关键,在于如何将产业的研究成果转移到教育体系。目前与Chiplet有关的设计方法、技术,都掌握在厂商手中,学生在教育体系裡面没有机会接触,导致熟悉Chiplet设计的人才养成相当困难。

人才对于半导体产业的发展,重要性自不待言。如果教育体系能培养出具有Chiplet基础知识跟经验的学生,对于异质整合的发展,会有相当大的帮助。

应对IC设计典范转移 EDA工具做足准备

益华电脑(Cadence)研发副总裁Don Chan表示,对IC设计而言,大约每十年会出现一次重要的典范转移,EDA工具的发展重心也随之改变。2020年到2030年,将是3DIC跟异质整合大放异彩的十年,作为协助IC设计者完成工作的EDA工具,自然也要为3DIC的设计流程做好准备。

藉由将SoC解构成Chiplet,再透过先进封装技术将其整合成一颗元件,IC设计者一直在追求的效能、功耗与面积(PPA)三大设计目标,有了新的实现路径。但这个趋势也为IC设计者带来新的挑战,例如原本整合在SoC裡的功能应该如何拆分、如何设计多颗Chiplet间的互连,以及晶片堆叠后最棘手的散热问题等。这些新挑战都需要对应的设计流程、方法论与工具来支援。

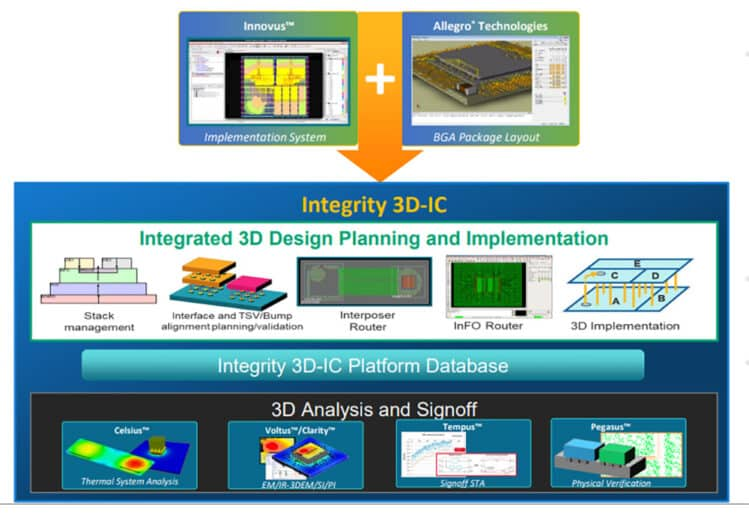

Cadence资深副总裁暨数位与签核事业群总经理滕晋庆则指出,藉由Integrity 3DIC 的推出,目前该公司已经有一套可以完整支援设计规画、设计实作与分析、签核的流程,能够协助IC设计者完成3DIC的设计工作(图2)。这是Cadence独特的优势所在,因为其他EDA工具业者大多只能为某几项特定流程提供工具,无法搭建出涵盖全流程的工具平台。

图2 针对3DIC设计,Cadence已能提供涵盖全流程的工具平台

但滕晋庆也预期,客户的需求不会一直停留在现状,未来客户一定会要求更多先进功能,例如更强大的设计分割(Design Partitioning)工具。此外,3DIC也改变了IC脚位配置(Pin Assignment)的规则,传统的IC脚位配置都集中在晶片的四周,但在3DIC时代,除了晶片四周外,还会有大量垂直方向的互联脚位。IC设计者肯定会需要更好的工具来因应日益複杂的工作。

抢搭Chiplet风潮 中国台湾IC设计产业急起直追

虽然国际大厂导入Chiplet的进展速度居于领先地位,但这个中国台湾的IC设计产业也已经开始尝试开发基于Chiplet的新产品。

联发科製造营运副总经理高学武就指出,对IC设计者而言,Chiplet最有趣,也最有价值的地方在于,这个概念让IC设计变得像在调鸡尾酒,只要调和不同的素材,就能实现出独特的产品。

另一方面,市场对下一代产品的要求越来越高,一颗晶片上的电晶体预算却受到光罩尺寸的限制,加上摩尔定律趋缓,使得联发科很难光靠製程微缩来满足客户对下一代晶片的功能跟性能要求。因此,藉由设计分割,把客户期望的功能分成多颗晶片来实现,再透过先进封装技术整合成一颗元件,是最好的解法。

而在联发科研发Chiplet的过程中也发现,设计分割确实可以带来节省成本的效果。因为有部分功能可以用较成熟、性价比更高的製程来实作,而且个别晶片的面积也变小了,让联发科得到更漂亮的良率数字。

事实上,一颗SoC裡面,有很多功能区块是无法从採用先进製程裡获得好处的,例如类比区块、SRAM、I/O,这些区块用比较成熟的製程节点,例如N-1节点製造,不仅性能不会受到太大影响,成本效益也好。不过,对于追求极致性能的产品,SoC还是会有比较好的优势,毕竟Chiplet之间的通讯频宽还是有瓶颈存在。所以,IC设计者必须在性能跟成本之间做出正确的权衡。

高学武透露,目前在联发科的产品线裡面,针对高效能运算应用所设计的晶片,已经採用了Chiplet架构,因为这类晶片的尺寸实在太过巨大,往往超过200平方公釐,更需要透过设计分割来让成本最佳化;在智慧型手机处理器方面,未来联发科应该也会一部分产品由SoC转向Chiplet,毕竟有些手机处理器SoC的尺寸也超过100平方公釐,再考量到先进製程的成熟度,其成本是相当可观的。

从高学武的分享,或许我们即将在2023年看到中国台湾IC设计产业在Chiplet的导入速度上急起直追,不再让国际大厂专美于前。

台积电积极建构3DIC生态系

晶圆代工龙头台积电,近年来在3DIC 领域也是动作不断。在该公司的2022开放创新平台生态系统论坛上,台积电宣布将成立开放创新平台(OIP)3DFabric联盟。此3DFabric联盟是台积公司的第六个OIP 联盟,也是半导体产业中第一个与合作伙伴携手加速创新及完备3DIC生态系统的联盟,提供最佳的全方位解决方案与服务以支援半导体设计、记忆体模组、基板技术、测试、製造及封装。

台积电科技院士/设计暨技术平台副总经理鲁立忠博士表示,3D晶片堆叠及先进封装技术为晶片级与系统级创新开启了一个新时代,同时也需要广泛的生态系统合作,以协助设计人员透过各种选择及方法寻找出最佳途径。在台积电与生态系统合作伙伴共同引领之下,3DFabric联盟为客户提供了简单且灵活的方式,为其设计释放3DIC的力量。

从台积电积极建构涵盖价值链各方成员的生态系统,不难看出台积电想藉由提供完整方案,成为协助客户快速实现3DIC设计的赋能者(Enabler),进而在市场竞争中占据优势的意图。而随著台积电登高一呼,众多生态系成员纷纷加入的情况来看,我们肯定能在2023年看到更多晶片商推出基于Chiplet、3DIC这类概念所设计出的新产品。

芯耀

芯耀

809

809