他山之石可以攻玉。综合敏捷开发在其它行业的经验,并结合其在芯片开发流程中的历史、现状,芯华章初步提出敏捷验证的主要发展目标,以发展出下一代EDA 2.0的核心验证流程。

文章首发于《中国集成电路》,由国家工业和信息化部主管,中国半导体行业协会主办的官方专业期刊。感谢《中国集成电路》对芯华章的认可!

敏捷开发理念在芯片开发中的应用

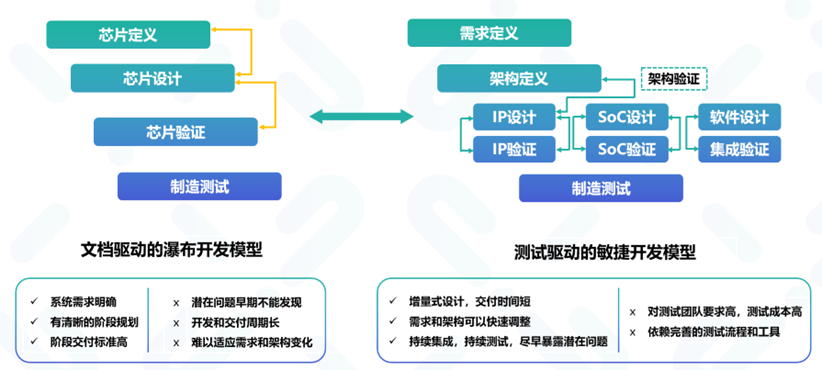

1970年温斯顿·罗伊斯(Winston Royce)提出了著名的开发流程“瀑布模型”。瀑布模型是将产品开发的各个周期按固定顺序而连接,形如瀑布流水,最终得到产品。直到80年代早期,它一直是被广泛采用的软件开发模型,在同时期的芯片开发项目中,也基本是采用瀑布模型。瀑布模型的优点是阶段划分明确,有明确的文档输入输出,但这种流程交付周期长,对阶段交付标准要求高。90年代开始一直到2000年之后,随着软件定制要求快速提高,以“Scrum”和“Agile”命名的敏捷开发方法逐渐发展,敏捷的核心在于更快、更多、更好的迭代,以更早的集成、测试、交付来发现问题和调整产品。但是敏捷开发方法对测试工具和测试团队提出了更高的要求。

敏捷开发并没有一个标准的定义,常见的特点有:

拆分和并行开发:大系统拆分成可以并行开发的子模块,各模块并行开发、并行测试,并能够集成为最终系统进行系统级测试;

持续集成、持续部署、持续测试:尽快尽早把各系统模块进行组合,并以最终面向用户的形式进行测试,并及时把结果反馈给开发;

自动化流程:把代码提交、模块测试、系统集成、系统部署、系统级测试的多个步骤形成自动化流程,自动化后即能用更多的高效与廉价算力来代替人工投入,并增加测试迭代次数,尽快反馈Bug,提高质量;

以测试来驱动开发:因为从代码到系统的部署和测试流程完全自动且更加及时,因此敏捷流程中往往测试代码先于功能代码开发,用测试代码来驱动功能代码的开发和测试;

尽可能复用成熟模块:复用现有的、经测试的可用模块,是降低开发和测试成本的重要手段。

敏捷验证解决芯片开发的瓶颈

敏捷开发实际上是一种理念而不是标准,与经典的“瀑布流程”之间并没有明确的分界线。虽然在软件特别是互联网软件领域应用得较多,但敏捷的理念已经逐渐被应用于很多工程开发领域。芯片开发制造作为一种特别复杂的系统工程,同样也不例外。如果我们回顾上世纪六、七十年代到九十年代的芯片设计和EDA发展历程,在开发流程上可以总结为如下图的变化,即芯片开发从早期的“定义-设计-验证-制造”瀑布模型逐渐细分,芯片越来越复杂,需求和架构的定义逐渐成为不同的阶段,而设计阶段随着RTL语言的发展也分化为IP、前端设计、后端设计、软件设计、系统集成,每个设计步骤都需要有对应的验证,并诞生了对应的建模、集成、验证的各类语言和工具。

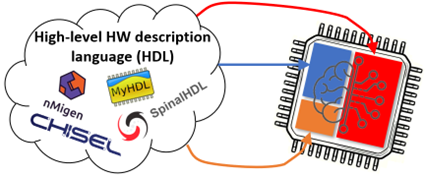

除此之外,近年来基于“敏捷设计”的理念,出现了多种提高RTL语言逻辑表达层次的电路描述语言,比如Bluespec、Chisel、SpinalHDL、nMigen等HDL语言和框架,它们基于Scala或Python等语言,加入RTL级描述和代码构建功能,主要出发点是简化从架构定义到硬件逻辑描述的流程,并能从这样的硬件逻辑描述自动生成RTL级电路实现。同时基于类C语言等高层次语言的HLS综合方法学,也在过去十几年逐步发展。这些都在推动芯片开发敏捷化的发展。

(图片来源于网络公开信息)

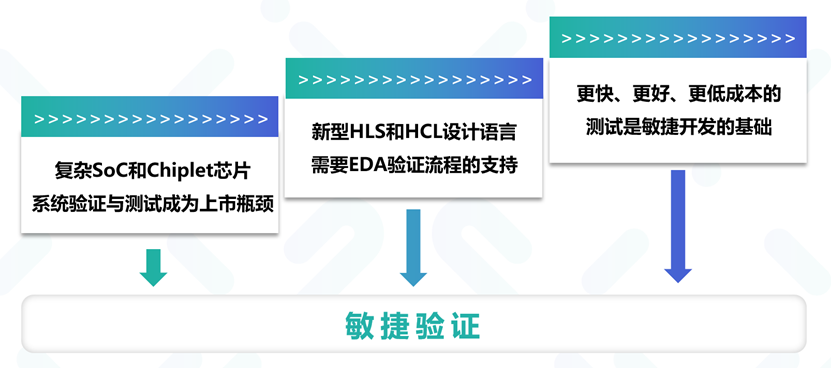

目前的HLS或HDL等高层次设计语言,更多集中在从架构定义到逻辑设计、电路实现的敏捷流程,侧重于提高芯片设计抽象层级,用可参数化、可复用的高级语言做设计,目的是让架构和逻辑的修改能快速反映到设计实现中。但是存在的问题是脱离了传统芯片电路级验证、调试、修改的流程,验证环节没有加速反而一定程度上让验证与设计脱节,增加了验证困难,因此在芯片开发流程中还没有得到普遍应用。

随着芯片的规模和复杂度越来越高,对芯片的验证要求越来越高。如何更有效地完成芯片所有功能的验证成为最大的挑战,芯片验证工作已经占用了整个开发流程的70%时间和资源,成为实际上的瓶颈。在芯片开发周期的所有阶段——包括架构、模块设计、综合、系统集成、软件开发和物理设计阶段,都会引入错误,而且很多错误是无法在当前阶段完全发现和解决的。这个背景也非常符合敏捷理念所面对的问题:用更快更完善的迭代流程,让设计和验证更“敏捷”地进入下一阶段,才能更早发现每个模块在后期阶段才能暴露出的潜在问题。

从上文可以看出,没有自动、智能、快捷的验证流程和工具,就无法完成复杂大规模芯片的低成本敏捷开发流程,也无法推动EDA工具流程向敏捷开发方向发展。因此,优化和完善芯片敏捷开发流程,首先要解决如何实现设计验证敏捷化的问题。

芯片敏捷验证的发展目标

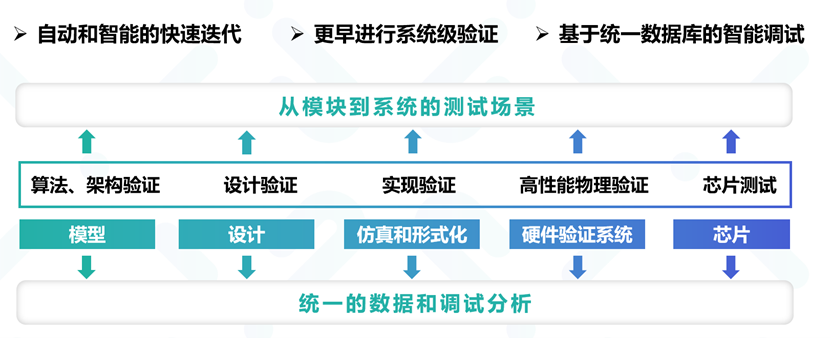

综合敏捷开发在其它行业的经验,并结合其在芯片开发流程中的历史、现状,我们初步提出敏捷验证的主要发展目标,以发展出下一代EDA 2.0的核心验证流程。

特别值得一提的是,这里列出的每一个点目标,都需要EDA算法团队、EDA工具厂商、芯片设计团队、计算平台供应商这整个生态的紧密结合和配合,不仅仅从技术角度,还需要从应用模式角度变革,才能快速推动现有EDA流程的发展。

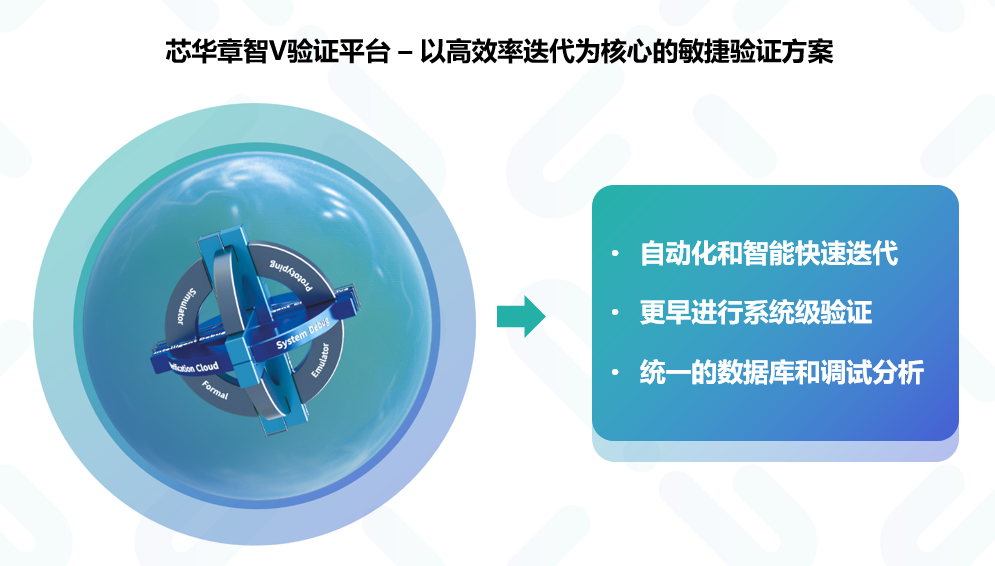

自动和智能的快速迭代

EDA验证的本质是基于特定流程的大量计算,而近年来全球算力发展的突飞猛进,让超大规模计算的成本大幅降低,这给计算替代分析的工程方法学带来了更多空间,敏捷验证在迭代流程和计算优化方向的发展目标包括但不限于如下优化点:

支持自动化的快速部署、持续迭代流程

自动化流程是整个敏捷验证和敏捷开发的核心基础,目前的模块和IP级开发,一般基于UVM等测试框架,使用自动化脚本完成仿真流程并收集测试结果和覆盖率数据,单个工具的流程自动化已经比较完善。但是,面向功能测试或约束随机的测试用例,还是需要大量的人工分析和编写。同时多种EDA工具之间的协同,特别是到集成验证阶段,还经常需要大量人工介入来完成集成和实现,因此实际情况往往是各种工具单独使用,模块验证和集成验证相互隔离。我们需要发展更自动和智能的平台级EDA工具,实现多工具协同下的测试用例生成、设计编译、实现、验证计算、数据收集一直到部分调试分析的自动化,以支持敏捷开发中“快速部署和持续迭代”的工程方法学,缩小从设计到验证的周期及成本。

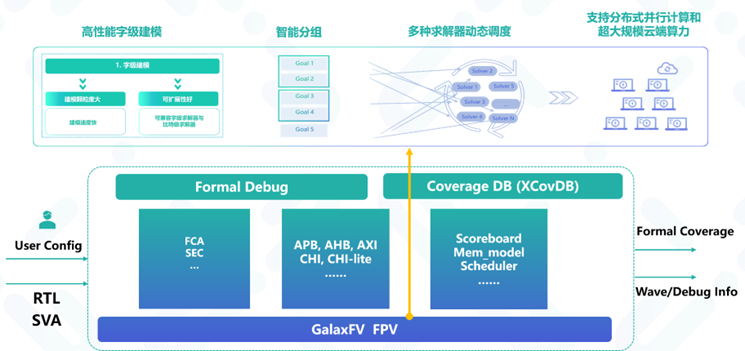

更多使用基于大规模算力的形式化验证方法

形式化验证方法能够从数学建模角度全面地验证设计是否正确,是对仿真验证方法的有效补充,也对验证自动化的发展有利。但过去形式化验证的应用往往受限于求解空间和计算量。随着近年来全球算力规模的大发展,以及AI方法在辅助形式化验证求解方向开始取得进展,将会有效推动形式化验证得到更广泛使用。同时,形式化验证工具也需要从计算性能、核心调度算法、应用场景支持、云计算应用不断改进,基于新型形式化验证EDA工具,验证流程会更加依靠大规模算力而不是人工投入。如芯华章科技的GalaxFV形式化验证产品,已经在形式化验证工具的前沿发展上取得了一定进展。

更早引入系统集成验证到迭代流程中

设计者越来越认识到,芯片设计的后端实现过程以及与软件的大系统集成,往往会引入新的问题或者暴露设计的深层次问题,而且未来Chiplet级芯片的创新发展,会对EDA系统级验证提出极高要求。因此,EDA验证过程,需要基于自动化的EDA工具、各种功能、性能、互联模型的支持以及多验证平台的联合仿真,在验证迭代中尽早引入后端的实现验证和软硬件系统集成,推动EDA前端仿真、功能验证、后端实现、后端验签等全流程步骤的自动化,让架构和设计的任何修改都能够快速反映到验证系统中,并进行从模块级到系统级的迭代测试,让架构和设计的问题尽快暴露在更接近真实环境的系统中,这也包括了系统级性能和功耗的提前验证。当然,更早实现系统级的验证迭代不意味着放松模块级的测试要求。

更敏捷的验证计算

EDA算法优化 :EDA验证相关的核心逻辑和求解器的算法优化和异构实现;

EDA计算并行化 :基于多核、多节点、高速联接的并行计算网络结构,加速EDA验证的并行计算;

EDA计算规模化:基于架构灵活、成本更低的大规模弹性云计算资源,在更高层次实现EDA验证集群的并行化;

EDA计算异构加速:EDA验证计算传统上主要依赖主流CPU主机,但随着异构计算的快速发展,新型CPU、GPU、光计算甚至量子计算平台,会越来越多地进入传统EDA计算的领域,以实现更高效、更低成本的大规模计算;

基于大数据的AI机器学习和“传统计算”的结合:大数据分析和机器学习被不断应用在前端验证、后端布局和验证、制造测试等不同的EDA验证阶段,是一个已经出现并会不断加速的趋势;

更早进行系统级验证

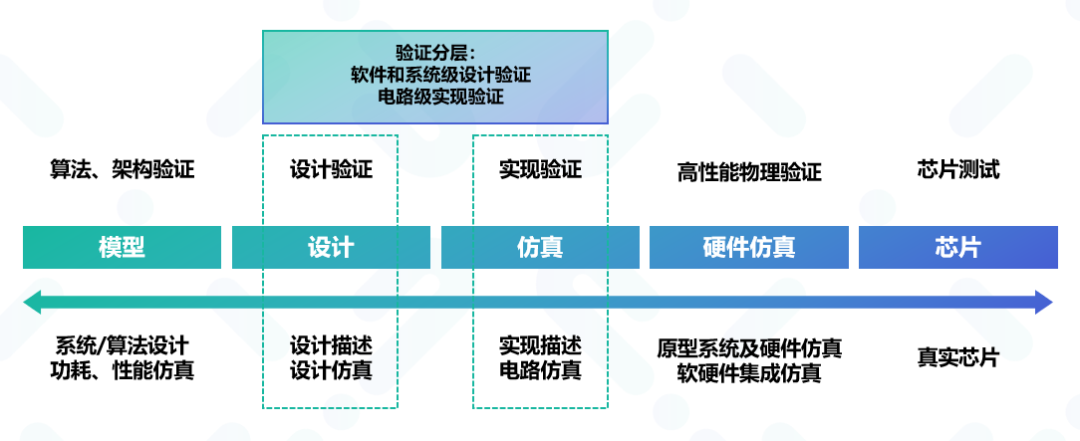

系统层验证和电路层验证分离

传统芯片硬件开发的特点是逻辑设计和电路实现紧密结合,在验证环节同样也是如此。但是随着SoC芯片复杂度提高,芯片验证的很大一部分工作更偏向于系统功能测试和软件测试,特别是依赖操作系统和大量中间层软件环境的系统测试,用传统的电路级验证语言很难支持。因此,EDA工具实现系统软件层功能验证和实现层电路验证的分离,让用户更多使用传统软件层的高级语言来完成系统层验证,是未来验证语言和验证工具的重要目标。

这可以有效降低对验证工程师的综合性要求,并减轻验证中的开发工作量,复用更多现有的软件生态,并在逻辑无关的底层实现级更多使用形式化验证、验证IP复用等方法自动验证。同时,未来chiplet多芯粒芯片的发展目标,也会逐步降低对电路实现层验证的需求,而逐渐加大对系统软件层面功能和性能验证的比重。

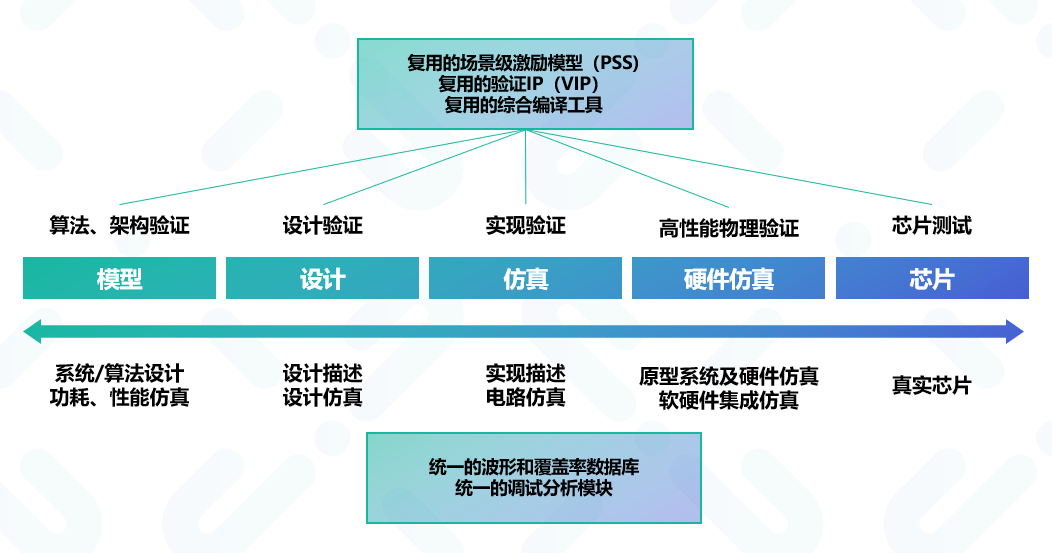

更多的验证复用

敏捷验证的另一个重要发展方向是从验证工具、验证数据、验证IP到测试用例的统一和大规模复用。例如基于PSS(Portable Stimulus Standard)标准和工具的复杂场景测试用例,可以覆盖从ESL级模型到最终芯片实现的多级测试复用。而更统一的设计编译工具,可以有效减少软件仿真、硬件仿真、形式化求解等多种工具相互迁移时的重复编译时间。最终多种验证工具所产生的互补的验证结果和数据,应该能集中到统一的中央数据库中,并通过管理工具进行项目验证进程的计划、管理。最终整个验证流程和多种验证工具不应该是碎片化的,而应该形成统一的验证平台(Verification Platform)。

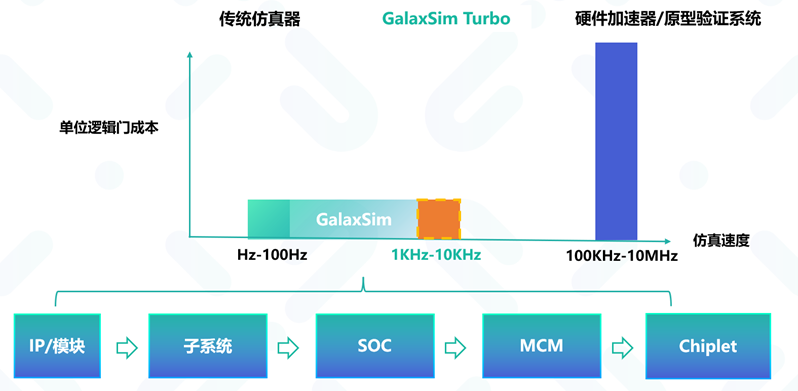

基于软硬件仿真的系统验证自动化

仿真是验证过程中的核心手段。随着SoC和Chiplet芯片越来越广泛应用,在验证过程中尽早启动系统级验证、并减少系统级验证的实现成本,是验证敏捷化的最重要需求。具体来说,大规模系统级验证在软件仿真阶段,过去没有很好的EDA手段,最近芯华章科技推出的GalaxSim仿真Turbo模式,首次填补了系统级软件仿真的空白,在提前做系统级验证、降低大规模系统验证成本方面走出了第一步。

同时,硬件系统平台仍然是大规模高性能系统仿真的必要手段。过去在硬件系统仿真上,我们遇到的很大困难是产品和人力成本的高投入,从设计到系统验证这个流程需要在多种软硬件平台上一次又一次地由工程师来实现。芯华章科技的硬件验证系统产品,致力于统一软硬件平台,降低客户在EDA成本和人力成本上的大量投入。

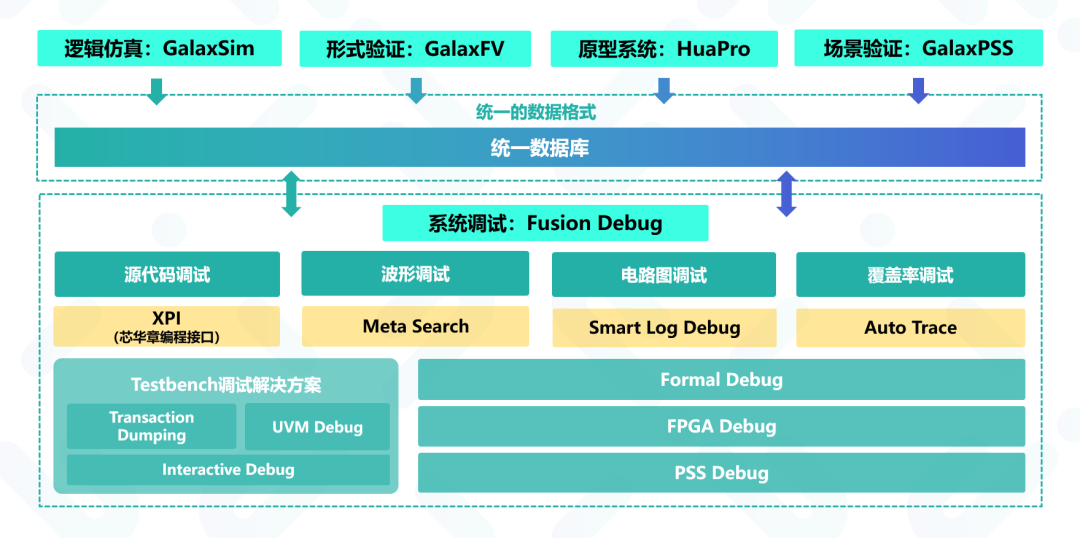

基于统一数据库的智能调试分析

基于统一数据的统一调试

除了利用多种静态和动态的验证方法和不同的验证工具,我们都知道,波形、源代码、电路的调试,以及覆盖率的分析和改进等工作,占系统芯片设计中4成以上的工作量。因此,更敏捷的验证需要各种EDA工具能统一和合并所产生的大量基础数据,并提供给芯片设计验证团队统一的调试工具,基于这些基础数据去进行分析调试,以贯穿整个验证环节,支持更敏捷的迭代。芯华章的FusionDebug,贯穿之前提及的系统验证技术与工具,具备开放的接口,高效的压缩和读写速度,支持分布式调试,能很好的支持敏捷验证快速迭代,分析与调试所需。

更智能和更高抽象层次的调试

验证计算与调试分析是不能分离的,所有验证过程中暴露出来的设计问题,目前都需要人工从电路到架构自下而上的分析去解决。但敏捷验证中的标准化接口模块复用、分析工具智能化、调试工具智能化,可以逐步辅助解决从电路、信号波形和Log数据向设计逻辑和架构的逆向映射,提高调试的抽象层次,并利用基于大数据的机器学习方法缩小问题分析空间,最终实现在设计层面而不是电路层面解决绝大部分的调试需求,并减少调试对人工投入的需求。

结语

敏捷开发思想已经普遍应用在软件和系统产品工程领域,而在芯片设计工程中还处于探索阶段,但敏捷的思想和价值对EDA及芯片行业的发展非常重要,因此发展更加敏捷的芯片验证技术,推动芯片的全流程敏捷开发真正实现,对实现芯华章科技提出的EDA 2.0发展目标极其关键,未来发展还需要整个行业的共同努力。芯华章针对数字芯片验证流程已经提供了多种验证产品,配合芯华章的通用基础技术模块共同构成“智V验证平台”。

同时芯华章于2022年成立研究院,目前也在开展敏捷验证相关的系列研究,欢迎行业专家与同仁的交流、合作,共同推动敏捷验证和敏捷开发在EDA设计流程中的应用。

1566

1566