该课程“神经网络加速器与SOC芯片设计”为系列课程,分为2部分,19个课时,特惠399元(原价:¥735)。

本课程以底层硬件为切入点进行神经网络加速器与SOC芯片设计,与高层次综合工具直接生成电路的方式不同,此课程是以主流、传统的方式进行芯片设计,因此更加关注于电路底层的细节(如每一个模块的功能、工作模式、效率、资源消耗等)。本课程将分为两个主要部分:SOC芯片设计基础与神经网络加速器设计,第二部分的课程依赖于第一部分的SOC设计基础。

第一部分以数字电路与硬件描述语言为出发点,讲述正确的模块设计方法、Verilog代码编写思路、模块间常用的通信模式以及“AXI4”总线协议,同时会对AXI4总线的开发、仿真、调试进行深入剖析,并以此为基础在FPGA开发板上完成SOC芯片设计。

第二部分从通用卷积神经网络对加速器的功能需求为出发点,定义了加速器所需支持的功能,划分加速器的功能模块。本课程将着眼于整个神经网络中运算量最大的功能——卷积运算,对卷积运算通路进行架构建模与分析,并进行模块的设计与验证工作。在FPGA上完成基本的功能验证后,会对硬件的性能进行测量与评估,进行性能评估时所使用的网络是VGG16。

金牌讲师:

蔡宇杰

多次参加电子设计竞赛、数学建模竞赛并获国家级奖项,以综合成绩100.72分从西安电子科技大学保送复旦大学微电子学院读研。在复旦期间荣获“华为企业奖学金”与全国研究生创“芯”大赛获得一等奖,同时有着丰富的实习经历。现已拿到大疆、华为等多家名企offer。

他的其它畅销课程:

课程特色:

网络上Verilog语法教程很多,但使用Verilog进行复杂模块设计、仿真方案、上板测试并且调试的教程却很稀少,通过HLS工具生成电路,你无法学习芯片电路底层知识,更难谈起“从底层对硬件进行优化”,可能连“工具产生的电路的瓶颈在哪、这个瓶颈如何导致、能否解决”都意识不到。对做实际工程、就业很不好,本课程将从硬件底层出发,你会对整个系统的工作模式、瓶颈、资源消耗等了如指掌。

本期课程内容:

基于缓存结构的卷积运算电路模块实现(二)

适宜人群:

- 想学习数字芯片设计、FPGA开发;

- 对数字电路设计有一定基础、想对硬件电路底层进行更加深入的学习的同学。

通过本系列课的学习,你将收获:

本系列课程目录:

本课程为系列课程,分为2部分,15个课时

第九节:DMA的工作原理与基于AXI-HP总线的DMA模块设计

第十二节:特征的内存映射方式、通用池化运算单元的功能需求与架构设计

工具列表:

可适用板卡:

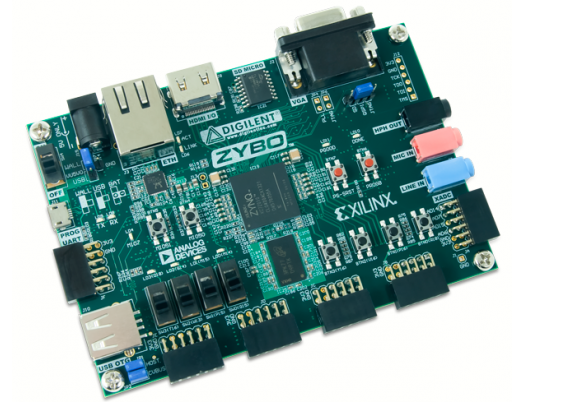

本课程适用于PYNQ,ZYBO以及所有带ARM硬核的FPGA开发板,若你有一定软核使用经验,也可使用纯逻辑开发板。

Zybo/Pynq开发板介绍:

Zybo是一款功能强大丰富,开箱即用型的Xilinx Zynq-7000 APSoC 软硬协同嵌入式开发板。Zynq系列芯片基于Xilinx全可编程片上系统架构(AP SoC),将双核Cortex-A9 ARM处理器与Xilinx 7系列FPGA紧密集成在同一芯片上。Zybo Z7板上搭载有丰富的多媒体接口和连接外设,在其本身就是一台功能强劲的单板计算机的基础上,进一步添加了FPGA功能,令其拥有无可比拟的开发灵活性与强大性能。Zybo Z7所集成的视频处理功能集,包括一个兼容MIPI CSI-2的Pcam(摄像头模块)接口,HDMI输入,HDMI输出和高带宽DDR3L,使之成为时下“嵌入式视觉”这一Xilinx FPGA最为热门的应用领域的一大高性价比解决方案。除此之外,Zybo Z7丰富的Pmod接口让用户能够十分轻松地进一步实现硬件功能的外设扩展,可搭配70多种Digilent专利的Pmod积木式传感模块使用。

Zybo是一款功能强大丰富,开箱即用型的Xilinx Zynq-7000 APSoC 软硬协同嵌入式开发板。Zynq系列芯片基于Xilinx全可编程片上系统架构(AP SoC),将双核Cortex-A9 ARM处理器与Xilinx 7系列FPGA紧密集成在同一芯片上。Zybo Z7板上搭载有丰富的多媒体接口和连接外设,在其本身就是一台功能强劲的单板计算机的基础上,进一步添加了FPGA功能,令其拥有无可比拟的开发灵活性与强大性能。Zybo Z7所集成的视频处理功能集,包括一个兼容MIPI CSI-2的Pcam(摄像头模块)接口,HDMI输入,HDMI输出和高带宽DDR3L,使之成为时下“嵌入式视觉”这一Xilinx FPGA最为热门的应用领域的一大高性价比解决方案。除此之外,Zybo Z7丰富的Pmod接口让用户能够十分轻松地进一步实现硬件功能的外设扩展,可搭配70多种Digilent专利的Pmod积木式传感模块使用。

Pynq-Z2是一款功能强大丰富,开箱即用型的Xilinx Zynq-7000 软硬协同嵌入式开发板。Zynq系列芯片基于Xilinx全可编程片上系统架构(AP SoC),将双核Cortex-A9 ARM处理器与Xilinx 7系列FPGA紧密集成在同一芯片上。板上搭载有丰富的多媒体接口和连接外设,在其本身就是一台功能强劲的单板计算机的基础上,进一步添加了FPGA功能,令其拥有无可比拟的开发灵活性与强大性能。此外,还支持Xilinx推出的开源框架PYNQ,支持使用Python进行应用层的开发与调用底层FPGA硬件加速,旨在使基于Zynq架构上的嵌入式开发更加简单易上手。使用Python编程语言以及丰富的第三方扩展包,开发者可以充分利用Zynq架构中的可编程逻辑器件和微处理器的优势,创造出更多好玩有意思的嵌入式系统项目。

芯耀

芯耀

487

487