1. 使用Verilog编写三分频电路,输出为50%占空比(10分)

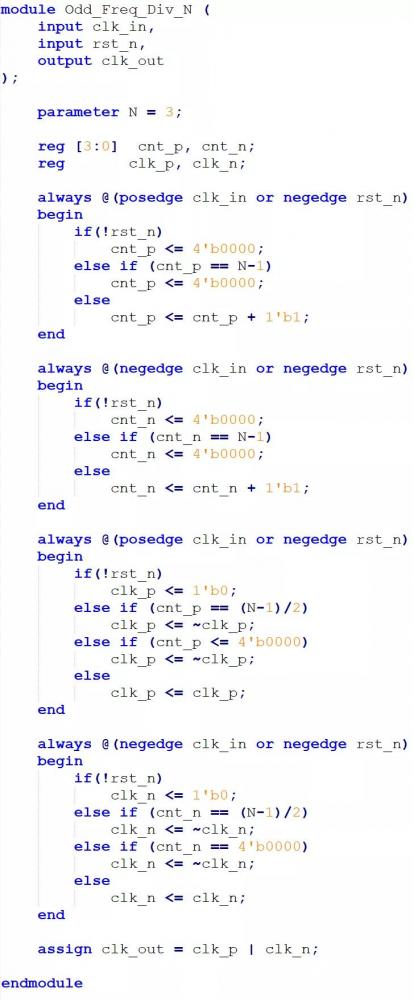

【解析】对于奇数分频,就是分别利用待分频时钟的上升沿触发生成一个时钟,然后用下降沿触发生成另一个时钟,然后将两个时钟信号进行或/与运算得到占空比为50%的奇数分频。具体方法详述如下:

Step1: 双沿计数器计数

使用2个计数器:cnt_up和cnt_down,分别在时钟的上升沿触发计数器cnt_up和cnt_down。[计数器进制:N进制;计数范围:0-N-1]

Step2:生成两个控制信号clk_up和clk_down

定义2个时钟信号clk_p和clk_n, 对于上升沿计数器cnt_p,当计数到0或者(N-1)/2时,均翻转clk_p信号;对于下降沿计数器cnt_n,当计数到0或者(N-1)/2时,均翻转clk_n信号。

Step3: 求出分频后时钟

若clk_p和clk_n初始复位为0,将2个时钟clk_p和clk_n通过或运算即可生成占空比为50%的分频时钟,且clk_out上升沿和原时钟上升沿对齐。如果clk_p和clk_n初始复位为1,使用与逻辑运算才能生成占空比50%的分频时钟。

占空比为50%的奇数分频(以7分频为例)的Verilog代码如下:

波形图就不挂出来了,勤劳的同学们自己跑一下仿真就可以看到结果了!

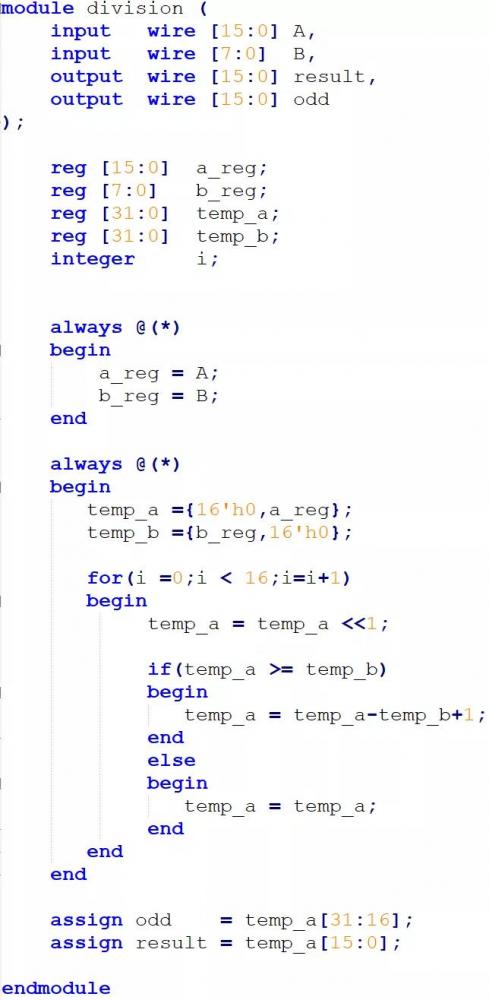

2. 除法器的Verilog RTL实现。16bitA,8bitB。C=A/B (15分)

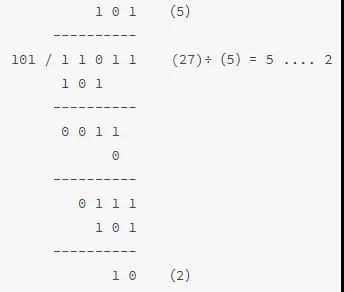

【解析】和十进制除法类似,计算 27 除以 5 的过程如下所示:

除法运算过程如下:

(1) 取被除数的高几位数据,位宽和除数相同(实例中是 3bit 数据)。

(2) 将被除数高位数据与除数作比较,如果前者不小于后者,则可得到对应位的商为 1,两者做差得到第一步的余数;否则得到对应的商为 0,将前者直接作为余数。

(3) 将上一步中的余数与被除数剩余最高位 1bit 数据拼接成新的数据,然后再和除数做比较。可以得到新的商和余数。

(4) 重复过程 (3),直到被除数最低位数据也参与计算。

程序按照以上原理编写如下:

3.简要描述AHB总线协议。包括有哪些信号,简要描述信号的作用(15分)

【解析】

AHB是AMBA总线系列中的其中一种,它是一种高性能的pipe系统总线。AHB总线细分,可以分为三组总线:写数据总线(HWDATA),读数据总线(HRDATA)和地址控制总线(HADDR)。

这三组总线相互分离互不干扰。对于每一组总线来说,同时只能由一个master或者slave来独占,这时需要仲裁器来决定将总线的控制权交与哪个设备,并控制多路选择器来选择已经获得控制权的那个设备来传输数据和地址信息。译码器根据地址来选择让哪个slave的数据通过选择器。

芯耀

芯耀

376

376

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍