摘要: 仿真和验证是开发任何高质量的基于 FPGA 的 RTL 编码过程的基础。本文档主要分享虹科设计过程中的关键步骤。

在IP核的开发过程中,面临着许多关键技术,比如IP核的规格定义、基于接口的设计、IP核测试存取结构标准、IP核的验证与打包等。对于IP核的验证,主要是建立参照模型和测试平台,然后进行回归测试和形式验证。

这里参照的模型主要用于对系统功能进行验证以及和RTL模型的对照验证,该模型主要用Verilog HDL等语言来构造。测试平台的建立与子模块设计并行,搭建验证环境和开发测试用例,并针对IP核的行为级模型对测试环境和测试用例进行调试,从而同步准备好用来仿真测试RTL级IP核的验证环境和测试用例。

仿真和验证是开发任何高质量的基于 FPGA 的 RTL 编码过程的基础。在本系列文章中,我们将分享我们设计过程中的关键步骤,并将基于虹科以太网IP核产品组合进行介绍。

整个过程的关键步骤如下:

- 面向实体/块的仿真:通过在每个输入信号上生成激励并验证 RTL 代码行为是否符合预期,对构成每个 IP 核的不同模块进行实体/块的仿真。

- 面向全局的仿真:一旦不同的模块被单独验证,则意味着下一步将整个IP仿真为单个 UUT(被测试单元)。

- (On)硬件测试:尽管扩展的仿真计划提供了良好的可信度,但仍有许多corner的情况无法在虚拟环境中验证。对于这些情况,需要基于硬件的测试计划,这也是获得高质量结果的最后一步。

一、面向实体/块的仿真

“面向实体或块的仿真”这一步骤意味着验证在 IP 核内具有特定操作的特定实体或模块的正确操作。每个 IP 核都由许多实体或块组成,为了测试它们,每个实体会有不同的测试平台,通过在输入受到刺激时观察设计的输出来执行设计,这将有助于检查预期的行为。举个例子有助于理解这些内容,在此之前,我们需要先介绍虹科以太网交换机 IP 核的过滤数据库。

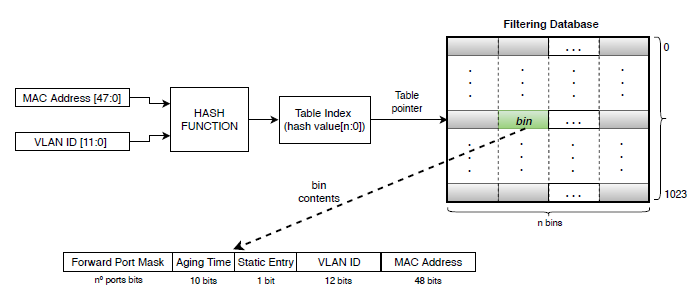

过滤数据库存储 MAC 地址及其相关信息以做出帧转发决策。它是一个基于哈希的存储器,每个地址条目都有一些存储过滤数据的 bin。该哈希算法还生成过滤数据库内存的索引。

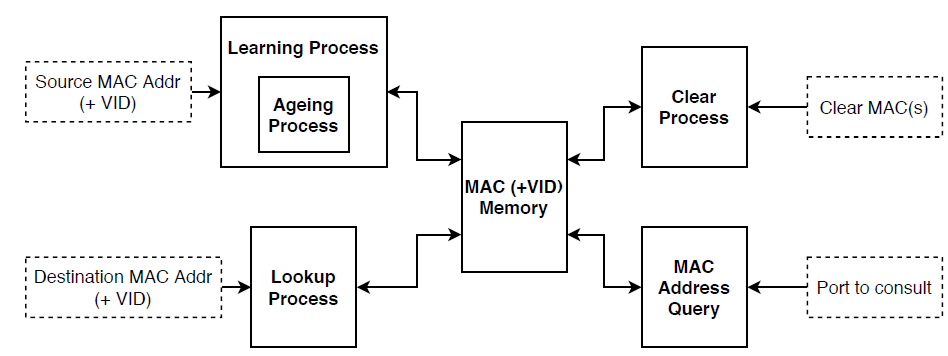

过滤数据库执行有三个主要过程:学习、查找和老化。

- 学习过程负责在满足不同条件时保存帧。

- 查找过程是在过滤数据库中搜索并获得帧的转发端口掩码的过程。

- 老化过程根据给定的时间段删除旧的 MAC 条目。

在这个仿真MAC表的具体案例中,请始终尝试测试构成过滤数据库功能的所有机制。从这个意义上说,就像学习不同的MAC,不同的查询、老化是并行完成的,最后需要清除MAC表并验证所有条目都已删除。此外,研究并始终能够测试可能的corner案例也十分重要。

测试和验证复杂 FPGA 设计的第二个关键步骤是面向全局的仿真。一旦形成 IP 核的所有实体都按预期工作,全局仿真就会发挥作用。

二、面向全局的仿真

全局仿真意味着验证整个IP实体的正确行为,包括构成产品的每个子模块。为了适应不同客户的用例,虹科SoC-e IP核解决方案在设计时充分考虑了灵活性,这意味着虹科所有的IP核都是高度可配置的,无论是在集成时(以优化 FPGA 中的封装)还是在运行时。借助于有着不同接口选项的寄存器映射(在下面的示例中,使用 AXI4),运行时配置成为可能。

这种灵活性也对仿真过程提出了挑战,因为需要根据仿真环境中的不同测试用例来配置IP。对此,虹科的合作伙伴SoC-e团队开发了一个令人惊叹的智能测试平台环境,在该环境中可以进行实时配置并实现自动化,开发人员可以通过“点击应用”的方式来执行复杂的仿真。例如,测试平台可以通过交换机发送以太网帧,并可以通过访问IP 核的统计寄存器来读取结果(并检查输出是否符合预期)。

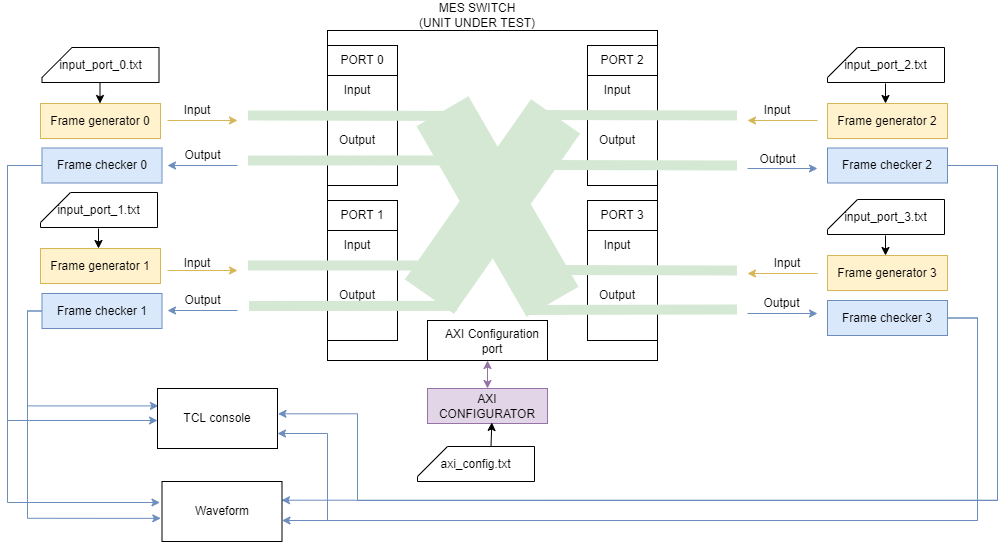

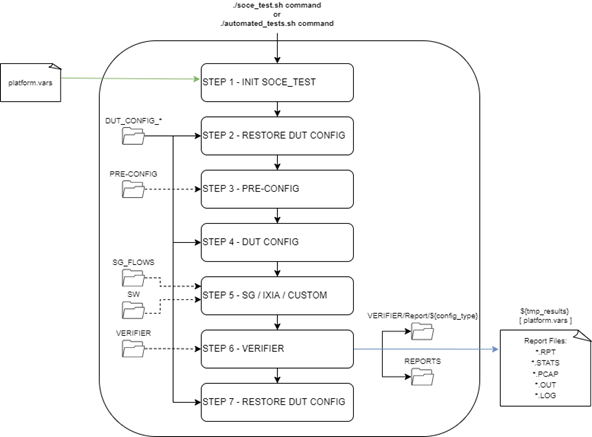

这极大地加快了调试过程,并允许开发团队执行快速迭代,而这在基于硬件的测试环境中会慢得多。在下图为具有此类全局测试平台架构的框图(基于虹科网管以太网交换机IP核):

网管型以太网交换机 (MES) 表示为UUT。其余的测试平台组件是符合整个环境的不可综合的 VHDL 模块:

- Frame Generator::该模块连接到以太网交换机 IP 的入口端口,负责生成激励(以太网帧)。

- Frame Checker:该模块连接到以太网交换机IP的出端口,负责分析交换机转发的流量。

- AXI Configurator:它控制 AXI4 配置总线以修改配置寄存器的内容(读/写操作)。

2.1 测试平台执行流程

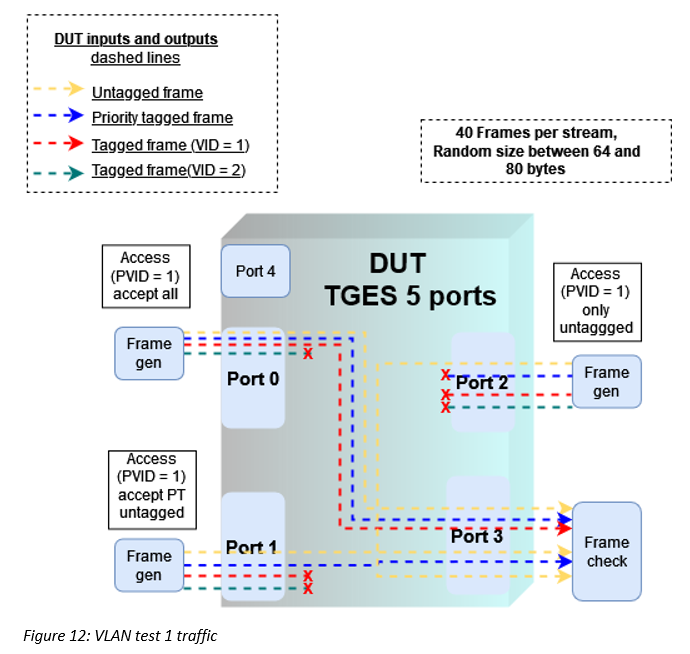

正常的测试平台执行流程如下:首先,AXI Configurator模块根据测试用例配置IP核。之后,每个Frame Generator都会生成测试帧,并将其发送到启用的入口端口。帧是通过循环重复某些特定测试文件中定义的内容来生成的。最后,Frame Checker接收帧(接收与否,取决于测试用例)。该块将检查每个端口对应的统计信息,并根据执行的测试用例确定输出是否符合预期的。

虹科SoC-e测试平台架构的一大亮点是Frame Checker可以自动检测多种错误,例如完整性错误、转发错误或帧丢失。这是可实现的,因为Frame Generator可以生成具有特定格式的流量(例如有效载荷中的特殊模式、序列号等),Frame Checker可以解释这些流量。

2.2 虹科测试平台测试计划

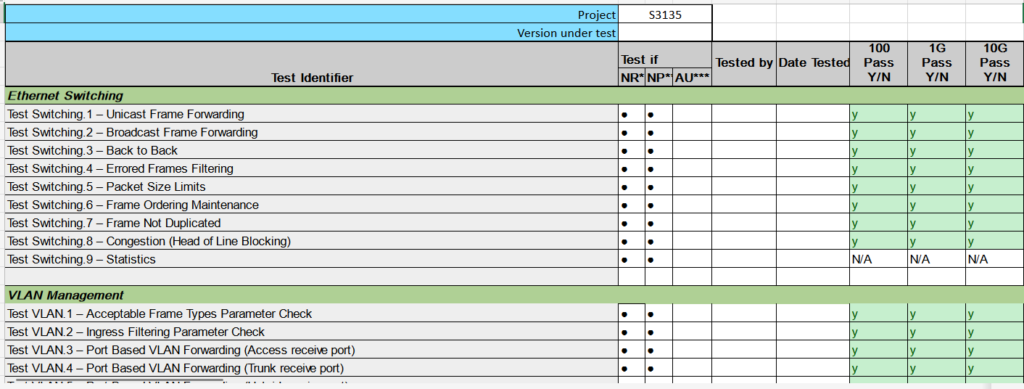

该测试平台套件的惊人灵活性还与SoC-e定义的严格测试计划相结合。对于每个IP核,都有一个测试计划,旨在在仿真环境中测试尽可能多的特性。

例如,网管以太网交换机IP的测试计划可以被划分为五个主要部分:

- 通用交换

- 自定义转发

- 过滤数据库

- 优先队列

- VLAN

这些部分旨在涵盖与网络相关的不同功能的行为,以及不同的流量模式和情况。

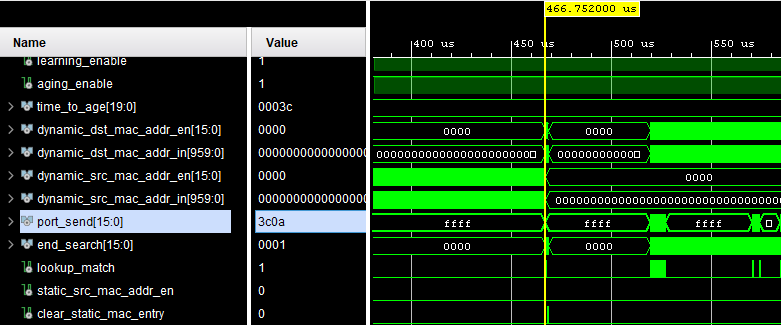

2.3 仿真波形和TCL控制台

测试平台的结果可以由开发人员或用户以不同的方式进行分析。TCL控制台用于快速反馈测试结果。然而,在某些情况下,在仿真的特定时刻深入了解特定信号值可能会很有趣。对于这种情况,虹科团队还开发了预先格式化的波形,以便于查找特定信号。

2.4 用于测试执行的命令行界面(CLI)

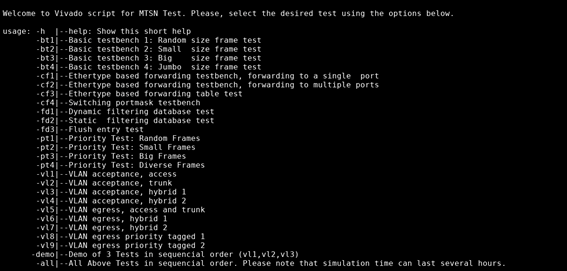

此测试平台环境中包含的最新功能之一是可以直接从命令行界面(CLI)执行所有测试,而无需打开RTL仿真工具(Vivado或其他工具)。这是一个很大的改进,因为它可以实现更高的测试自动化。它基于使用Vivado编译器命令的脚本(Python)的使用,以便用户生成易于解释的结果。下图显示了向用户显示的仿真菜单。用户只需选择相应的选项即可执行任何列出的测试:

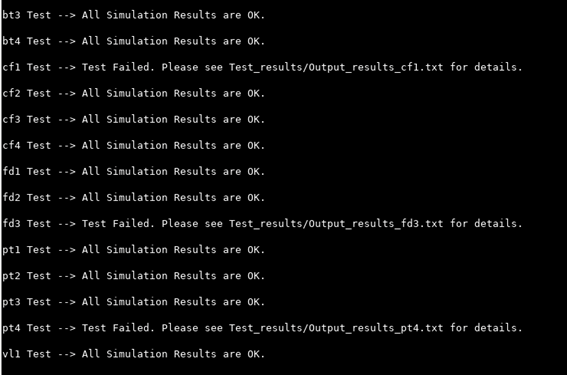

众所周知,仿真是一个需要大量时间的过程。即使在功能强大的计算机中执行,毫秒或以上范围内的复杂仿真也需要持续数十分钟,甚至更长。为了简化执行所有测试的过程(这需要几个小时),我们实现了一个“-all”选项,它允许在管道中执行所有测试,且无需用户交互。完成所有测试后,它将提供有关每个测试的报告消息(如下图所示),并在测试失败的情况下生成输出文件,以便开发人员稍后进行分析。

虹科SoC-e测试平台套件,现在作为产品提供!

虽然所有这些测试平台环境仅用于内部调试和开发目的,但由于不少客户有使用该测试平台的需求,因此虹科的合作伙伴SoC-e目前已将其作为产品,提供给那些使用虹科SoC-e IP核解决方案并希望能够执行高级仿真工作(系统级仿真)的客户。如果您对该产品感兴趣和/或想了解更多信息,请通过sales@hkaco.com联系我们。

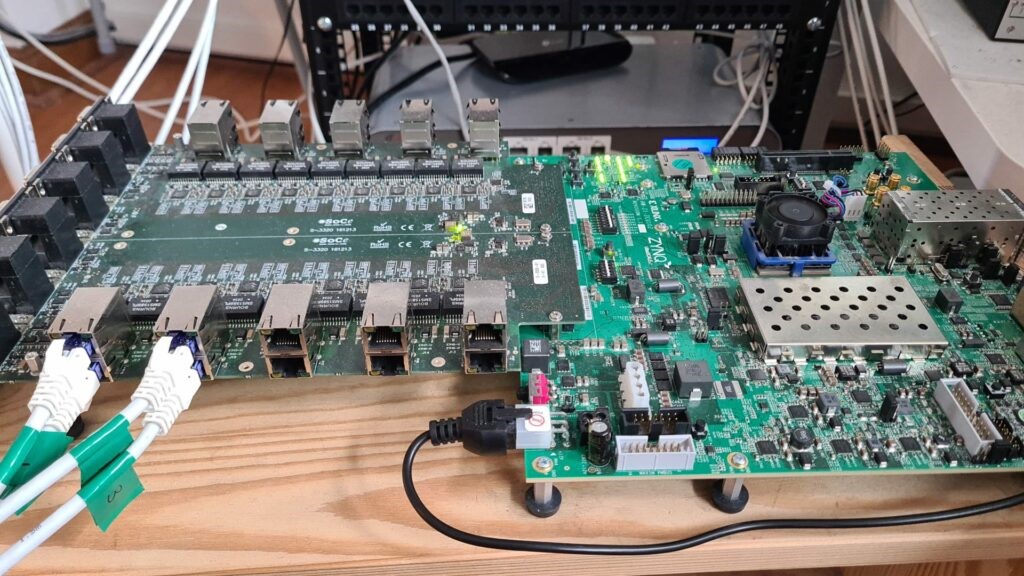

三、硬件测试

硬件测试是为IP核产品执行高质量测试和验证计划的最后一步,主要可以分为以下几个阶段:

1)测试准备:定义在产品开始测试之前必须完成的步骤

在这个阶段,定义了测试计划文档。在这个文档中,详细描述了必须在 DUT(被测设备)上执行的每一项测试。

2)测试执行:执行上一个阶段中定义的测试用例

3)问题报告:检查和报告在测试执行期间检测到的所有问题

我们提供了一个问题电子表格,其中将记录在测试阶段检测到的每个问题。每当注册新问题时,都会向开发团队报告,并且能够追踪哪些问题已解决,哪些问题仍有待审查。

4)测试结束:确定测试阶段何时完成,并创建测试结果文档,其中将包含成功执行的测试的摘要以及有关测试的更多相关信息。

3.1 虹科SoC-e测试工具

为了优化测试执行过程,我们使用了虹科SoC-e测试工具以进行自动化测试。该工具考虑了以下内容:

- DUT配置过程

- 流量注入和嗅探

- 记录从 DUT 返回的流量

- 验证保存的日志

- 将 DUT 设置为原始状态

3.2 SoC-e测试软件架构

该工具的第一步与DUT 配置的执行有关。这是通过名为 Platform.vars 的输入配置文件完成的。通过该文件,用户可以配置不同的参数,如 DUT SSH 参数、主机 PC 的 IP 地址或网络接口。

第二步,完成TS(测试站)和 DUT之间的流量注入和嗅探。我们有不同的第三方设备用作测试站,但最常用的设备之一是IXIA Novus One Plus。流量可以通过 IXIA 的 Python API 轻松发送。数据包操作是通过 Scapy Python 模块完成的。尽管 Scapy 允许传输该工具生成的所有流量,但它是使用不同的工具tcpreplay执行的。这使我们能够克服由 Scapy 引起的带宽和准确性方面的某些限制。在此步骤中,测试提供了自定义流量的灵活性,以验证不同的 DUT 功能。可扩展性不是问题,因为该工具支持添加额外的流量和测试端口。

第三步,该工具使用测试站或通过 Linux tcpdump 软件登记来自 DUT 的流量。

第四步,SoC-e 测试工具验证上一步中存储的信息(统计、寄存器转储(dump)等),以检查一切是否正常。通过这两个步骤,SoC-e 测试工具为测试用例的验证提供了一个很好的解决方案。

最后,第五步,也是最后一步。最后一步的主要目的是将 DUT 配置恢复到其原始状态,因为它可能在测试期间被修改。

IP核可以使开发人员减设计工作量并缩短产品上市时间。虹科目前已有丰富的IP核产品组合,包括TSN IP核、HSR/PRP IP核、以太网IP核、冗余IP核等,可以轻松集成到用户的FPGA中。若想了解更多信息,欢迎随时通过info@hkaco.com联系虹科工业控制团队!

联系虹科工程师:18922242268

联系链接:https://tl-tx.dustess.com/ChxLxfu6M0

芯耀

芯耀

3456

3456

下载ECAD模型

下载ECAD模型

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍