原标题:中国IC设计调查

01 什么是芯片IP

芯片,专业上也称集成电路,被喻为国家的“工业粮食”,是信息行业最核心和最重要的组成部分,被称作是信息时代的“基石”,它是衡量一个国家高端制造能力和综合国力的重要标志之一。

如果说石油是现代化工业的血液,那么芯片就是“中国智造”的灵魂,是发展“互联网+”必不可少的因素。数据显示,自2013年开始,我国每年进口的芯片价值超过2000亿美元,已经超过石油,成为最大宗的进口产品。

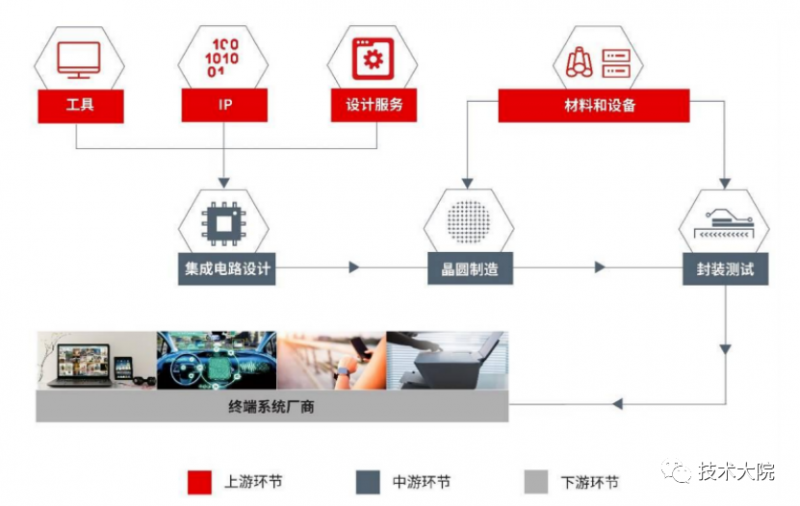

芯片设计位于半导体产业的最上游,是半导体产业最核心的基础,拥有极高的技术壁垒,需要大量的人力、物力投入,需要较长时间的技术积累和经验沉淀。而半导体知识产权的集中体现是享有独立知识产权的IP 核(Intellectual Property Core)。

什么是IP核?

IP核是芯片设计环节中逐步分离出来的、经过验证的、可重复使用的功能模块,通过使用IP核,设计人员无需从0开始对所有细节进行重新设计,而是借助特定的IP核经调整后快速完成某个模块的设计,以缩短开发周期,降低设计成本,降低设计错误发生的风险,提高芯片设计效率。

如果打开一颗芯片,我们能看到版图上很多个IP组成了整个电路。这些集成电路IP核在芯片设计中看得到摸得着,也能够完成一定功能,更重要的是可以通过授权不同客户实现复用。如果做一个比喻,那IP就是组成芯片设计的“乐高”模块。

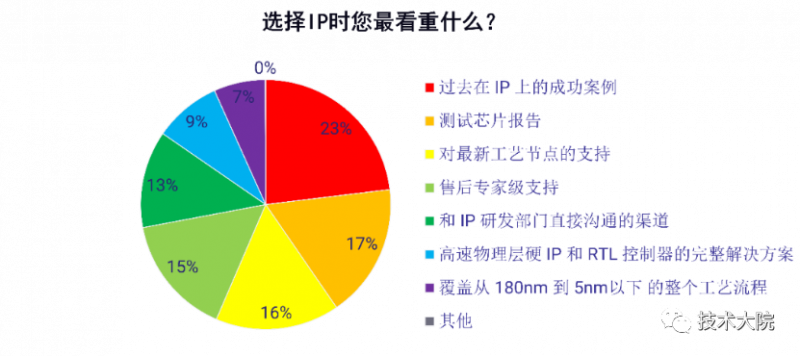

那么IC设计工程师在选择这些IP模块时,主要的考虑是什么呢?

根据调查,23%的工程师最看重过去在该IP上的成功案例,这样可以避免一些未知风险。其次最在意的是测试芯片报告(17%)和对最新工艺节点的支持(16%),看重这两点的原因是IP需要满足各种晶圆厂的工艺生产要求,如果不能做到兼容,Fabless在更换代工合作伙伴时就需要根据Foundry的半导体工艺设计套件(PDK/FDK)重新完成设计和硅验证。

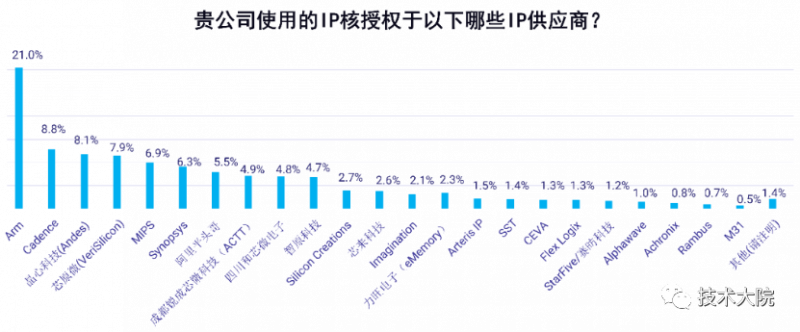

IC设计工程师可以选择的IP供应商越来越多,在调查列出的20多家IP核供应商中,从IP使用量的角度来看,Arm依然是最受欢迎的IP供应商,其次是Cadence、晶心科技、芯原微、MIPS和新思科技等。值得注意的是,RISC-V内核的关注度这两年一直在涨,也与中国推进芯片产业自主可控有关,排名前几位的Andes晶心科技、芯原微、阿里平头哥都是RISC-V架构的主要推动者。

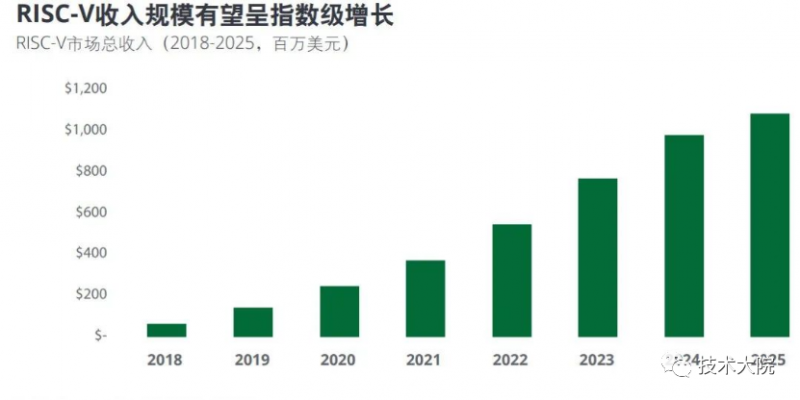

02 RISC-V IP核异军突起

在智能物联网需求多样化环境中,开源指令集的RISC-V架构具有广泛的发展前景。而且RISC-V处于发展早期,在量产化和产业化方面,国内外差距并不大。在这方面,国内的以Andes(晶心科技)为代表的企业这几年正在大力发展和推广RISC-V IP。

近期,RISC-V国际基金会的首席执行官卡利斯塔·雷德蒙德表示,估计市场上已经有100亿个RISC-V核心。从2010年诞生至今,RISC-V用12年左右的时间实现100亿核心数的出货量,展现了作为新架构的生命力。

影响指令集架构发展的因素:

- 外部环境

贸易战背景下,自主可控势在必行

政策驱动,集成电路产业迎来发展机遇

新一代信息技术加速渗透,新兴领域对芯片提出了更高的需求

- 内部因素

从产业内部角度来看,主流指令集架构复杂,硬件实现难度大

授权费用高企,芯片企业成本居高不下

RISC-V首席技术官Mark Himelstein说:RISC-V是一种开放的硬件,开放源代码的硬件指令集体系结构:

- RISC-V ISA是完全开源的,任何人都可以免费使用

RISC-V架构本身开源,但基于RISC-V架构开发的CPU IP核是收费的

类似于开源的Linux与收费的Redhat Linux一样,Redhat可以提供相较开源Ubuntu/Debian更好的稳定性及对上层软件的兼容性

同理,商业的RISC-V IP核可以提供比开源核更好的稳定性、发展连续性、售后服务等

- 一种精简的指令集计算机(RISC)架构

只有47条指令,相比之下,Arm有200多条指令

AMD和Intel使用的复杂指令集计算机(CISC)架构远超过1500条指令

- 可扩展性

模块化设计,只配置需要的部分严格规定兼容性

Engineer可以添加自己的指令集

可用于DSA(特定域的加速度)

RISC-V是一种简单、开放、免费的全新指令集架构。不同于过去x86、ARM等国外商业公司垄断的私有指令集架构,RISC-V最大的特点是——“开放标准化”,这种开放性,在CPU领域是彻底的第一次,也是CPU技术变革的一次绝佳机遇。

在很长一段时间里,x86和ARM两大架构各有所专,一个聚焦服务器、PC市场,一个聚焦移动处理器、物联网等嵌入式市场。但是,台积电等独立代工企业的出现拉平了其他芯片开发厂商与x86发明者英特尔的工艺差距,ARM也开始进入PC及服务器市场,苹果M系列处理器、华为鲲鹏、亚马逊Graviton等芯片的问世,让市场注意到ARM进入高性能计算市场的可能。

天下苦ARM久矣,当前市场整合、避免单一架构寡占、地缘政治优先事项和物联网终端的激增,正大力推动RISC-V得到更广泛地采用。这是自80年代以来芯片架构多样性消失之后,再次推动架构多样性的好机会。

在数据中心,服务器越来越以业务负载为中心,并且激增了大量的应用专用处理器来加速业务负载和提高效率。芯片更加多样化也为各种处理器架构创造了更多机会。推动RISC-V在高性能计算、超算、边缘计算以及AI、机器学习、深度学习等领域的应用,目前有141家会员单位从事RISC-V数据库、基准测试和应用的开发。

从竞争性角度看,Arm架构和x86架构分别在移动终端、PC和服务器市场垄断多年,在这些领域RISC-V新玩家渗透进去还非常需要时日。但在AIoT、新能源汽车电子、异构计算等新兴领域,RISC-V和其他架构站在同一起跑线,反而具备一些巨头们不具备的新起跑优势。

从成本角度看,RISC-V开源的特性对于芯片创业公司而言非常友好。选择这一架构,意味着初创公司可以在AI芯片研发过程中节省IP授权成本,将资源投入到最核心的技术研发,帮助公司加快芯片的迭代速度,灵活应对市场环境的变化。

从技术趋势角度看,RISC-V架构开源、精简和模块化的理念符合未来的技术发展趋势。计算体系结构宗师David Patterson(RISC-V的创始人之一)在ACM通讯上发表的论文中就指出了计算机体系结构的两个机遇,其中一个就是开源的指令集ISA,创建一个“面向处理器的Linux”。从目前来看,RISC-V无疑是开源指令集架构中最成功的一个。

从开发者角度看,RISC-V不需要像ARM一样考虑向后兼容,没有历史包袱,基础指令只有几十条,学习门槛相对较低;另一方面,RISC-V支持开发者按需拓展指令,这为芯片研发提供了更高的自由度。

从性能角度看,RISC-V架构内核的性能可与ARM内核性能抗衡。

从IP开发角度看,要把核心技术掌握在自己手里,坚持IP核心自主研发的技术路线,RISC-V架构则提供了这一可能,不用考虑可能面临的授权风险。

AI正在从云端智能下沉到边缘端和设备端,面对客制化应用场景,如何设计体系架构才能实现高性能和低功耗成为整个业界都在探索的问题,除了通过研发先进工艺降低边缘端功耗、芯片设计全流程的系统外,基于RISC-V的架构上创新也是一条可取之路。

笔者认为:不远的将来,RISC-V会跟X86、ARM形成三足鼎立的格局,大概率成为继X86和ARM架构之外,处理器架构的第三级(甚至是第二级)。

03 本次调查中 RISC-V 阵营最多采用者:Andes 晶心科技

身为RISC-V协会创始首席会员的晶心科技(Andes Technology)成立于2005年,Andes从早期拥有自己的第三代ISA架构到转到RISC-V。Andes晶心科技是老牌的处理器内核企业,拥有一定的客户积累和市场经验,根据本次调查,工程师在选择IP时,最看重的首推「过去在IP上成功的案例」,处理器搭建是复杂的工程,晶心科技累计十数年的经验能够提供客户提供额外的帮助。

据笔者了解,Andes目前的研发人力几乎全数投入RISC-V 系统,从入门到高效能运算,从32到64位,Andes 拥有较为完整的嵌入式RISC-V CPU IP产品组合,可对标ARM的 M0到A55。

Andes的集成开发环境--AndeSight™,晶心科技基于AndesCore®整合平台提供创新的嵌入式微处理器和SoC平台解决方案。把软件工具链、虚拟开发平台、硬件开发平台及Andes处理器核整合在一起,呈现给客户一个开发SoC及系统解决方案所需要的基础环境,能协助并简化嵌入式系统的开发,并为客户提供多功能的整合环境,包括出色的工具链与函数库、自动化操作脚本、AndeSim™近周期仿真器、方便的除错工具、分析工具以及操作系统感知开发。而且,AndeSight™也提供丰富的参考程序代码、优化程序库,让开发者可以轻松上手。

据了解,目前采用Andes核心的大厂客户,在手机方面包括联发科;MCU方面包括瑞萨电子、上海先楫半导体;在AI方面有希姆计算、韩国的SK telecom;在存储方面包括Phison等等,而使用Andes核心量产的客户,已经应用的制程从5nm到40nm均有,全球客户采用AndesCore® CPU累计出货已超过一百亿颗芯片量产。

Andes也提供整合开发多功能的Andes Custom Extension™ (ACE),在ACE的架构下,SoC设计者可以轻松且有效率地在Andes RISC-V处理器核心上定义新指令来加速目标应用程序,即透过ACE的简易脚本程序来描述指令的输入输出和功能,及使用ACE的精简Verilog来定义指令在RTL层级的实现方式。根据上述的设计数据,功能强大的COPILOT (Custom-OPtimized Instruction deveLOpment Tools)工具可以自动生成扩展晶心处理器所需的所有新组件,包括处理器的RTL、编译工具、调试器、整合开发环境和近似精确周期 (near cycle-accurate)的模拟器,以支持客制化的新指令。

而针对IoT或工业计算机等需要针对特定场域设计的项目,Andes也提供客制化工程服务,服务内容有AndesCore®设计及验证、FPGA原型设计及验证、SoC前段设计及验证、以及软硬件IP设计等。

此外,还有AndesBoardFarm,一个云端服务可以提供SoC设计人员从自己的计算机远程取得晶心FPGA开发板及管理软件的系列工具,让他们能立即体验开发AndesCore® RISC-V处理器。藉由使用晶心所提供的全面整合开发环境AndeSight™,设计人员可以透过网络以晶心最新的CPU核心运行他们的软件,进行性能测试并直接获得结果;同时,还可以探索晶心所提供的各种软硬件的功能。工程师善用AndesBoardFarm的服务,将大幅减少评估RISC-V处理器的时间和精力,为他们的SoC选择最佳的RISC-V CPU核心。

Andes的产品的也包括完整的售后服务,包括Andes e-Service及技术咨询服务,客户可透过Andes e-Service系统快速的提出服务要求,有效率地与晶心的客服工程师沟通,并且有系统地追踪服务的进度及质量。客户可联络晶心的业务或技术服务人员取得Andes e-Service账号,在Andes e-Service系统内注册技术服务要求。

至于AndesCore®的部分,主要包括高速算力的A系列、一般通用型、支持RTOS应用的N系列,支持RISC-V的SIMD / DSP指令集(P扩展指令集草案)的D系列、矢量处理器V系列、多核技术的MP系列,等等,这些嵌入式处理器及相对应系统芯片发展平台的设计与发展,主要的应用包括:

- 45系列内核均采用有序的8级双发射超标量技术,可提升效能适合高度平行运算的应用,搭配Coherence Manager和可选用的L2缓存控制器,满足如AR/VR、人工智能/机器学习、5G、车载信息娱乐系统(IVI)、先进驾驶辅助系统(ADAS)、视讯/图像处理、企业级储存装置、连网装置等等高负荷运算需求的应用

晶心的V5架构,除了符合最新RISC-V扩充指令,也支持V5创新功能,包括:

- PowerBrake、QuickNap™

- 可节省功耗的WFI、提供堆栈上溢/下溢(stack overflow/underflow)保护的StackSafe™

- 能在RISC-V C扩展指令以外进一步提高程序代码密度的CoDense™

Andes的RISC-V CPU内核IP已经攻破了多个市场,包括IoT边缘、个人和云数据中心。而且,Andes最近成为第一个与SGS-TÜV Saar GmbH合作完成ISO 26262功能安全开发过程认证的RISC-V供应商。产品开发流程经过了独立评估,符合最高ASIL D的CPU内核开发要求。

04 车规级产品 Andes 遥遥领先

Andes已成为首家获SGS-TÜV Saar认证ISO 26262功能安全 ASIL D等级完整开发流程的RISC-V CPU供货商。Andes的第一款功能安全IP N25F-SE,已有多家客户加入先期计划导入设计,针对多种车载应用开发车用SoC。该功能安全IP解决方案将在今年下半年正式开放对外授权。

2022年2月24日晶心科技宣布已通过ISO 26262认证,符合车用功能安全处理器内核开发标准。德国功能安全认证机构SGS-TÜV Saar GmbH进行独立评估后,确认晶心系统性的开发能力已达到汽车安全完整性等级(Automotive Safety Integrity Level;ASIL)的最高等级ASIL D,这包括ISO 26262标准Part 2、4、5、6、8 和 9等所有适用的章节。根据正式记录,在2020年12月晶心成为第一家同时获得硬件(ISO 26262-5)和软件(ISO 26262-6)流程认证的RISC-V处理器IP供货商。

相对于其他消费级工业电子组件,汽车电子组件需要面对更苛刻的外部工作环境,使用寿命要求更长,可靠性和安全性要求更高。车规芯片和消费芯片有几个显着的区别:

- 设计目标不同:消费类芯片主要考虑性能、功耗和成本(PPA);车规芯片还会综合考虑可靠性、安全性、一致性和长效性

- 工作环境不同:消费类芯片一般满足0-70℃环境温度,而车规芯片要满足-40-105℃的使用温度要求

- 设计寿命不同:消费类产品一般不超过5年;汽车设计寿命是10-15年,汽车芯片寿命也要按此设计

“车规认证”即是针对这些使用场景特点,对汽车芯片的生产流程和产品设定了相关认证要求,满足所有要求,才能通过“车规认证”。而车规级芯片,是指完全满足所有“车规认证”要求,并通过第三方认证机构认证的汽车芯片。

ISO 26262:汽车供应链的“准入门票”

- ISO 26262则是全面规范汽车零部件以及芯片功能安全的基本规则。功能安全强调的是保障功能正常,不会出现突发问题,能够正常报警、安全执行,是能力层面的保障

- 业内对于功能安全的认证较多使用ISO 26262《道路车辆功能安全》国际标准。所以通过这一标准的认证,也已成为时下汽车供应链厂商们的准入规则

- ISO 26262除了关注控制随机硬件失效外,还关注避免系统性失效的发生

- ISO 26262功能安全认证分为功能安全流程认证和功能安全产品认证

ISO 26262是全球车用电机及电子产业共同一致适用的标准,晶心藉由通过ISO 26262的认证,充分展现对于车用产品安全的支持与投入。

“晶心科技是通过SGS-TÜV Saar的ISO 26262认证的一流公司,”SGS 互联与产品事业群郭耀文副总裁表示。“功能安全的基础建立在产品规范、设计、实施、整合、验证和确认等基础操作上。在通过ISO 26262认证前,晶心在这些开发流程上早已建立了相当完整且扎实的质量管理系统。除此之外,他们经验丰富的安全工程专业人员付出了相当多的时间和努力,来建构起晶心科技一套遵循ISO 26262标准的完整系统。这些都是我们之所以能够按预定时程非常顺利完成所有独立评估和认证的原因,这对双方来说是一次非凡的经历。”

“SGS-TÜV Saar的认证服务获信誉卓著的德国认可委员会(DAkkS)认证。我们进行了多次全面审查,确认晶心科技已内化并遵循系统性的功能安全要求来建构其开发管理系统,管控的流程能兼顾充分的查核及落实实施的平衡性,符合了ISO 26262标准的最高等级(ASIL D)产品开发的规范要求。”SGS-TÜV Saar GmbH半导体功能安全产品经理Wolfgang Ruf表示。“我们在此致上诚挚的祝贺,也欢迎晶心在完成RISC-V CPU IP系列评估和验证后将其产品导入车用领域。”

“晶心科技深耕十七年,专注于开发强大的AndesCore®处理器系列,获得数百家客户采用于超过百亿颗芯片中,应用范围包括工业用MCU、企业级存储设备、5G基站和数据中心基础设施等等。”晶心科技总经理暨首席技术官苏泓萌表示。“随着车用电子组件的数量和复杂度快速增长,其安全性、可用性和稳定性对于人类福祉和可持续环境至关重要。此趋势对我们来说是绝佳的机会和责任,我们对这相当重视。晶心选择与业界领导者SGS-TÜV Saar合作,以确保我们的开发过程全面符合所有适用的ISO 26262功能安全标准,而不是仅符合部分条款便宣称适用车用标准。这充分展现我们对于车用电机和电子供应链严格且富挑战性的要求所付出的决心。”

芯耀

芯耀

2612

2612

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍