随着3D NAND技术的逐渐成熟,越来越多的闪存厂商开始向高层堆叠技术冲刺。2022年7月26日,美国存储芯片巨头美光发布公告称,原定于今年年底开始量产的全球首款232层3D NAND芯片,已经提前量产,预示着3D NAND芯片进入200+层时代。SK海力士也紧随其后,于8月3日宣布成功研发全球首款业界最高层数的238层NAND闪存,注意,这里SK海力士说的是成功研发,而不是量产,也就是说,量产级的200+层3D NAND芯片美光目前是只此一家。

目前,三星、铠侠以及长江存储等厂商也都在往200+层3D NAND闪存领域发力,竞争愈发激烈。

为什么各大厂商要追求高层堆叠技术呢?我们首先要了解一下NAND。

1、什么是NAND

NAND其实是闪存类型的一种。闪存(Flash Memory)是一种可清除的“只读存储器”,允许在其体内对资料进行多次的删除、加入或改写。

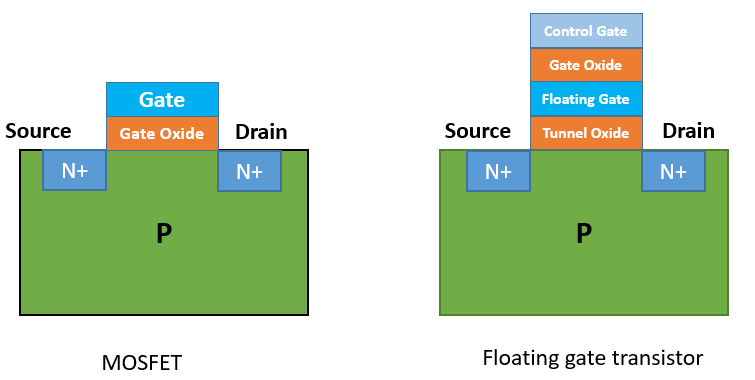

1980年,桀冈富士雄在东芝公司发明了NOR型闪存(NOR Flash)。1986年又发明了NAND型闪存(NAND Flash)。与NOR Flash不同的是,NAND Flash利用量子隧穿效应进行电子写入,而非传统力学方式。NAND Flash存储数据的基本单元是浮栅晶体管(或电荷陷阱存储单元,在3D NAND中常见)。我们以浮栅晶体管举例,它的基本结构为存储电子的浮栅极、控制极、P极、源极和漏极。与Mos管类似,在源极和漏极两头接通电压,若导通,则说明浮栅极中存在电子,定义为0,不导通则说明没有电子或只有少量电子,定义为1。在控制极通正向或反向电压,即可调整浮栅极中的电子数量,为写操作。由于浮栅是电隔离的,所以即使在去除电压之后,到达栅极的任何电子也会被捕获,这使得存储器具有非易失性。通过测量其阈值电压并与固定电压电平进行比较,就可以识别存储在浮栅晶体管中的信息,这称为闪存的读操作。

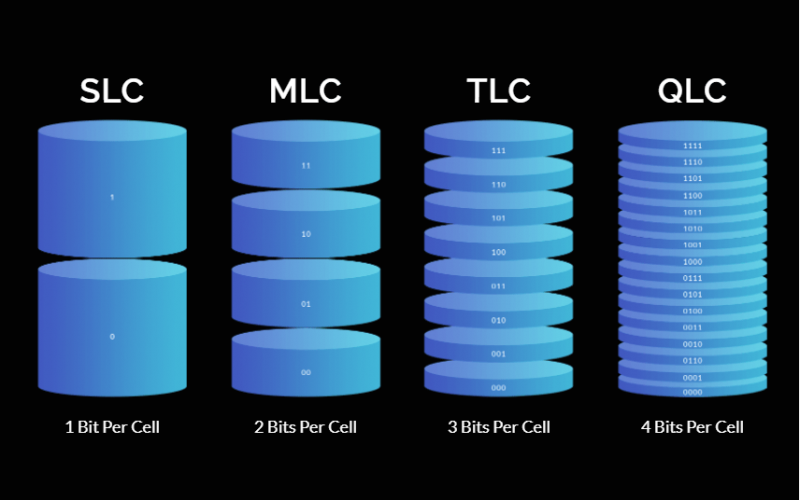

此外,通过对浮栅极中电子数量的精细控制与探测,可以使浮栅极呈现多种状态,即晶体管可存储多位数据。若存储一位数据,则一个浮栅晶体管具有0与1两种状态,若存储两位数据,则一个浮栅晶体管具有00、01、10、11四种状态,这也是SLC(一位)、MLC(两位)、TLC(三位)和QLC(四位)的区别。

NAND Flash具有较快的抹写时间,而且每个存储单元的面积也较小,这让NAND Flash相较于NOR Flash具有较高的存储密度与较低的每位元成本。同时它的可抹除次数也高出NOR Flash十倍。因此,目前我们见到的几乎所有消费级闪存都是NAND Flash。

2、为什么一定要追求高层堆叠

随着2D NAND节点尺寸缩小到十几纳米,每个单元尺寸变的非常小,单元中电子的串扰问题使得尺寸继续微缩变得愈加困难且不够经济。为了追求更大规模的存储方式,工程师们想到了在垂直方向堆叠互联多层结构的方式提高容量,于是3D NAND诞生了。

除了技术限制外,制造成本也是推动闪存颗粒走向3D结构的关键。

在特定的技术规模下,加工晶圆的成本是固定的。由于较小的制造流程需要不同的设备,因此加工成本存在差异。但是,每个硅芯片的成本几乎与其尺寸大小正相关。所以,最终可以安装在晶圆上的设备越多,每个芯片的成本就越低。

压低存储价格的关键在于降低每一位数据的存储成本。对于存储设备,这意味着在特定大小的芯片上存储更多位。在3D架构中,多层存储单元都基于硅片中的三维结构构建。这样可以为相同的表面积提供更多的存储空间,大大增加存储密度,且避开与较小的特征尺寸相关的问题。即使该过程使芯片成本增加一倍,将存储密度提高10或100倍,也可以显著降低每位成本。

追求更高层数的好处显而易见,这意味着单位面积有更大的存储空间,相应的,单位存储容量所需的成本也会降低。不过,NAND由2D转向多层3D,可不像堆叠起一张张打印纸这么简单。

3、3D NAND高层堆叠困难重重

在3D NAND结构中,存储单元以垂直堆叠的方式实现容量增长。在层层堆叠的过程中,沉积和蚀刻这两项工艺将面临巨大挑战。

Lam Research电介质首席技术官Bart van Schravendijk曾表示,3D NAND堆叠到96层时,实际沉积层数已经达到了192层以上,此时,氮化硅层的均匀性将成为影响器件性能的关键参数。

此外,在3D NAND结构中,必须通过蚀刻工艺从器件的顶层到底层蚀刻出微小的圆形孔道,将存储单元垂直联通起来。Lam Research表示,对于96层3D NAND晶圆来说,蚀刻的纵深比高达70:1,而且每块晶圆中都要有一万亿个这样细小的孔道,这些孔道必须互相平行规整。随着堆叠层数的增加,蚀刻工艺的难度也会逐渐增大。因此,在高层数NAND制造中,高纵深比要求的蚀刻工艺正成为限制3D NAND工艺发展的天花板。

目前,各大厂商的堆叠层数纷纷超越200层,可以想象,此时的NAND颗粒中早已“沟壑密布,水网纵横”。尽管目前似乎对层数没有任何严格的物理限制,但要超出此范围,可能需要结合使用不同的开发方法,以将3D模具彼此堆叠。

4、NAND技术如何发展,我国企业是否有一战之力?

3D NAND架构的提出,为闪存技术进步提供了无限可能。这两张闪存技术路线图可以清晰看出各大厂商对于技术规划时间节点的安排,其中包括三星、铠侠(原东芝存储)、美光、SK 海力士和长江存储等厂商的3D NAND技术发展路线。

2020年闪存峰会发布图片

2022年闪存市场网站统计数据

2007年,铠侠(原东芝)率先提出3D NAND架构,不过,三星是最先迈入3D NAND时代的厂商,2013年8月初就宣布量产世界首款3D NAND,并于2015年推出32层的 3D NAND。紧接着,SK海力士也于2014年推出3D NAND产品,并在2015年推出了36层的3D NAND。

美光在这一领域选择和英特尔进行合作。两者在2006年合资成立了Intel-Micron Flash Technologies(IMFT)公司,并联合开发NAND Flash和3D XPoint。不过后来两者分道扬镳,IMFT公司在2019年被美光收入麾下。英特尔则自立门户,拉起了自己的存储器开发团队。

国内厂商长江存储也在2018年推出了自己的32层NAND。虽然长江存储的起步较晚,但国内良好的半导体企业成长环境与市场的大量需求助推长江存储逐渐走向一线。今年8月3日,长江存储宣布第四代 3D TLC 闪存X3-9070研发成功,已经达到美国电子器件工程联合委员会(JEDEC)定义的多项测试标准。据供应链消息称,该闪存堆叠层数达 232 层,已经是目前业界的领先水平,想想长江存储2016年才成立,仅用短短6年追平了国际一线大厂,实属不易,也从一个侧面说明中国半导体业者打破技术壁垒和国际垄断的决心之大。

2022年过半, 200+层NAND领域已有多位玩家,离厂商规划的2023年冲击200层时间节点提前了半年左右,而大家对更高堆叠层数的追求和竞争还在继续,未来或许会出现“一层决胜负”的“白刃战”场景。

参考资料:

https://zh.m.wikipedia.org/zh-hans/%E9%97%AA%E5%AD%98 维基百科:闪存

https://diy.zol.com.cn/798/7985038.html 国货崛起,长江存储推出第四代 3D TLC 闪存,堆叠层数达 232 层

https://www.sohu.com/a/573837593_117925 全球首款!238层4D NAND闪存问世

https://www.sensorexpert.com.cn/article/85497.html 层数首次突破200层!美光全球首款232层3D NAND芯片来了

https://www.chinaflashmarket.com/News/2019-12/168970 3D NAND将会无限堆叠?沉积和蚀刻将是制约发展的两大瓶颈

2659

2659

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)