PCI-SIG在2022年1月发表了PCIe 6.0的正式标准规范,并利用PAM4编码技术,在尽可能维持电气规格与PCIe 5.0一致的前提下,实现了频宽倍增的目标。但由于PCIe 5.0的讯号传输距离已经远低于标准伺服器主机板的尺寸,业界最终还是得设法发展出更微型化的伺服器尺寸标准,否则互联设计过于複杂的问题,将无法解决。

主导PCI标准制定的PCI-SIG组织,在2022年1月发表了PCIe 6.0的1.0版本,正式完成了PCIe 6.0的标准化作业,并预期在12~18个月内,市场上将有第一款支援PCIe 6.0的应用产品出现。

与5.0相比,PCIe 6.0的频宽再度增加了一倍。在16通道配置下,单向最大频宽可达128GB/s,双向则是256GB/s。而为了支援这麽高的频宽,在PCIe 6.0标准中,导入了许多重要的新技术,不仅使6.0标准成为PCIe问世近20年来,变化最大的一次,同时也让6.0标准的实作变得极为複杂。

告别NRZ 全面导入PAM4调变

在PCIe 6.0之前的PCIe4.0/5.0,都是在3.0标准的基础上进行渐进式的革新。例如4.0跟5.0都沿用3.0标准所导入的NRZ(Non- Return-to-Zero)128b/130b编码,仅透过提高原始传输速率的方式来增加频宽。但PCIe 6.0已全面改用PAM4 128b/130b编码,让一个信号能承载四种编码(00/01/10/11),进而达成提升频宽的目标。

不过,也因为要在一个信号中承载四种编码,导致PAM4信号在传输过程中,理论上远比NRZ更容易出现信号错误,在信号完整度方面有相当大的疑虑,所以PCI SIG在6.0标准中,导入了向前纠错机制(FEC)作为配套,以保障信号完整性。

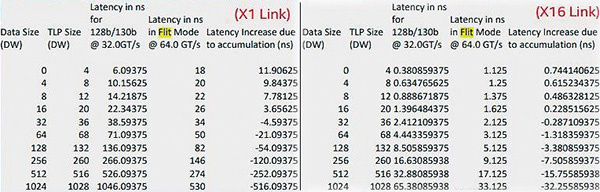

除了PAM4和FEC,PCIe 6.0在逻辑层还导入了流量控制单元(FLIT)编码。藉由这项技术,PCIe 6.0的有效频宽跟信号延迟,都获得了明显的改善。尤其是在高通道数与大资料传输时,藉由FLIT编码,PCIe 6.0的延迟可以比5.0改善超过30倍之多(图1)。

图1 PCIe 5.0与PCIe 6.0延迟性能比较

虽然从标准定义上来看,PCIe 6.0可说是PCIe发展至今最重大的一次更新,但这次更新所导入的新技术,严格来说并不新。不管是PAM4或FLIT,都已经广泛运用在200G以上的高速乙太网,因此对于有相关开发经验的设计工程师而言,要开发支援PCIe 6.0的应用产品,在某些方面来说,只要有对应的工具跟测试设备,不会是太大问题。

抢食PCIe 6.0研发商机太克动作飞快

在PCI-SIG发布PCIe 6.0基本规格和验证要求几週后,示波器大厂太克(Tektronix)即宣布推出业界第一个与PCI Express 6.0相容的基本发射器测试解决方案。

太克东南亚/中国台湾行销经理陈川迅表示,对于资料中心、人工智慧/机器学习(AI/ML)和高效能运算等资料密集型市场而言,PCIe 6.0是非常重要且可扩展的标准。为满足不断成长的效能需求,PCIe 6.0标准採用了PAM4信号编码和纠错技术。从量测的角度来看,这些更新主要都跟软体有关,故针对PCIe 6.0测试需求,太克提供的测试解决方案,也是在既有的硬体基础上,提供更多专为PCIe 6.0量测所设计的专用软体以及分析工具。

至于在硬体方面,针对PCIe 6.0,仪器本身需要增加一些新的强化功能,但客户如果已经拥有可以测试PCIe 5.0的仪器,可透过添购软体选项的方式,为既有的硬体提供PAM4 DSP功能和示波器上的杂讯补偿,来提高量测结果的准确性。

陈川迅进一步解释,由于导入PAM4,参考DSP方案发生了巨大变化。与PCIe 5.0中的4个极点和2个零点相比,CTLE现在变成了6个极点和3个零点;在DFE方面,複杂度则从3-Taps增加到16-Taps。在16GHz的条件下,PAM4允许的恩奎斯特(Nyquist)频率,跟NRZ编码是一样的,但眼宽和眼高急剧减小。在PCIe 6.0,开发者需要测量3.125ps的眼宽,眼高则是6mV。由于PAM4有3隻眼睛,我们在这裡指的是顶部的眼睛。

因此,从示波器硬体频宽的角度来看,我们仍然在PCIe 6.0中使用50 GHz的最小频宽,与PCIe 5.0没有什麽不同,因为信号的Baud Rate并没有改变。不过,在测试方法上,PCIe 6.0的Tx测试增加了一种新的测量方法,即信噪失真率(SNDR)。这个是从400G乙太网沿用过来的,如果有相关经验的工程师,对此应该很熟悉。

整体来说,从PCIe 5.0升级到6.0,跳跃程度不像从PCIe 4.0到5.0那样剧烈,因为奈奎斯特频率一样都是16 GHz。现在的挑战在于CTLE、DFE中,对DSP能力的新要求,以及如何应对由通道损耗引发的等化问题。

从测试和测量的角度来看,测试参数的项目越来越多,也越来越複杂。自动化和测试速度变得至关重要。太克很自豪能够率先发布 PCIe 6.0 Tx测试解决方案。我们的PCIe 6.0标准测试和调试解决方案可轻鬆整合进工程师的测试和调试工作流程中。

电气特性规范大致相同设计工程师喘口气

事实上,诚如陈川迅所分析,虽然PCIe 6.0看似导入了很多新技术,但对于硬体,尤其是跟线路设计有关的工程师而言,PCIe 5.0跟6.0的差别不大。有业界人士认为,这应该是PCI SIG刻意为之的结果,因为业界导入PCIe 5.0的过程,就已经相当吃力,如果6.0标准又来一次,其导入的时程恐怕会非常缓慢。

任职于某伺服器代工厂的RD 工程师就指出,从PCIe 4.0升级到5.0,对伺服器主机板的设计而言,是相当棘手的一件事。因为实体信号的速度大幅提升,所以PCIe 5.0信号的传输距离,是非常短的。

根据英特尔(Intel)所提供的设计规范,在PCIe 5.0,从CPU经过晶片组到连结的目标装置之间,整个绕线距离最长不应该超过13英吋。对标准伺服器而言, 13英吋的距离根本不够用,而且英特尔提供的设计规范,是建立在使用高阶、低损耗电路板的假定条件下,如果是使用损耗比较大的中阶电路板材料,PCIe 5.0的信号是跑不到13英吋的。

也因为信号能有效传输的距离太短,所以业界发展出两种解决方案,一种是用高架缆线的方式,让Tx跟Rx直线互连(图2);另一种则是在信号传输一段距离后,用Retimer还原PCIe 5.0的信号,让信号得以传输到更远的地方。这两种方法都会增加成本与主机板设计的複杂度,但已经是没有选择的解法。

图2 由于PCIe 5.0的信号传输距离很短,在主机板上用高架缆线实现直接互连,成为克服距离限制的方法之一

所以,PCI SIG在制定6.0标准的时候,在电气特性的规范方面,尽可能跟5.0维持一致,可说是相当明智的选择。如果6.0 标准又对电气特性定出更严格的规范,要把这项标准实际应用在可量产的产品上,将十分困难。

物理极限高牆横亘眼前伺服器微型化或为解方

虽然PCIe 6.0依靠新的编码方式,在电气特性规范、信号传输距离与5.0大致保持一致的条件下,实现频宽倍增的设计目标,但考量到PCIe 5.0本身的信号传输距离就已经很短的情况下,主攻高性能运算市场的业者,在规划其产品发展路线图的时候,恐怕还是得想办法把伺服器设计的微型化列为必须攻克的议题。毕竟,传统机架式伺服器的外观尺寸,对先进的高速互联技术而言,已经太过庞大,必须在板上使用更多元件来延长信号传输距离。

事实上,近几年在伺服器产业内,也已经有很多新产品放弃了传统机架外观,以便把伺服器整机做得更加小巧。原本主攻嵌入式运算领域的COM Express阵营,也正在全力朝HPC发展,试图以更精巧的外观,帮助伺服器用户实现更高的运算密度。

产品微型化一直是电子产业发展的主要趋势,只是在伺服器产业,因为要配合生态系的缘故,产品外观尺寸的演进速度,相对缓慢许多。展望未来,在高速传输介面的发展,越来越逼近物理极限的情况下,伺服器产业将有更充分与迫切的理由,发展出更微型化的产品。

1569

1569