近日,SEMI发布了一组有关半导体设备销售额的统计数据和预测:“预计2021年原始设备制造商总销售额将突破1000 亿美元大关,达到1030亿美元,比2020年的行业纪录(710亿美元)增加44.7%,到2022年全球半导体设备市场将扩大到1140亿美元。”这组数据表明,这两年的缺芯大环境带来了晶圆厂的短时急剧扩张,半导体设备总需求量也随之增加。

通常,半导体设备根据所处的半导体工艺环节的不同可分为前道(晶圆厂)和后道(组装/封装和测试),今天我们就来聊聊处在后道的ATE测试设备在芯片制程不断走向先进节点中的突破与改变。

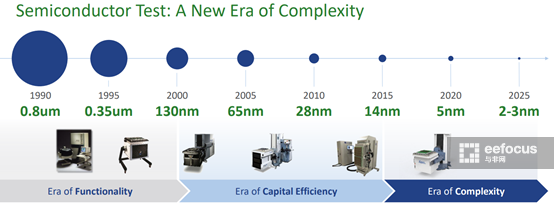

图 | 半导体测试设备在制程前进下的三个阶段

1990-2000:功能性时代

上世纪90年代,当时主流的芯片制程是0.35μm和0.13μm,这个时候随着CMOS工艺的蓬勃发展,通过集成模拟功能、数据接口等,SoC芯片的功能越来越强大。原先老的测试平台开始不能满足这种新生的模拟和高速接口测试的需求,于是ATE测试机开始了功能性的扩展,我们称这个时代为“功能性时代”。

2000-2015:资本效率时代

到了2000-2015年,芯片制程开始从0.13μm向90nm、65nm、28nm和14nm演进,芯片尺寸越来越小,芯片上面晶体管的集成度越来越高,为了适应这一变化,芯片对于测试专门设计,ATE测试机开始加强自身的标准化接口和DFT测试能力,从而满足SCAN扫描测试、BIST测试、标准化接口测试的需求。

此外,随着芯片规模的日趋变大,测试时间开始拉长,测试的成本在整个芯片售价之中的比例越来越高,一次只能测1颗芯片的单工位测试变成了芯片成本下降的阻力。于是ATE测试机不得不增加板卡上面集成的通道,增强自身的同测能力,从起先的单工位增加至2工位、4工位和8工位,我们称这个时代为“资本效率时代”。

2015-2025:复杂性时代

2015年之后,尤其是2020年前后,芯片制程进入5nm,甚至2-3nm节点,这个时候情况又开始轮回,晶体管数量的增长超过本身可测试设计的技术。此外,机台多工位测试也不可能无限次增加。而与之形成矛盾的是,芯片的生命周期却越来越短,消费类芯片从原来的2-3年变更为1年,AI芯片和AP高复杂度芯片开始逐年迭代,不同的领域要求ATE测试机作出不同复杂性的调整,我们称这个时代为“复杂性时代”。

复杂性时代面临“测试时间和良率”的双重挑战

随着先进工艺的演进,晶体管数量急剧增加,如果测试要覆盖到每个晶体管的话,芯片测试时间就会相应增加。测试时间增加根据芯片类型大概可分成两类:

第一类是处理器级别的大数字芯片,比如DPU,它的最大测试时间来自于Scan和BIST测试,与2015年相比,现在同样测试下的测试时间是当时的2.5倍,未来可能是3倍。

第二类是模拟和射频芯片,它的最大测试时间来自于模拟测试和Trim测试,Trim测试就是在测试之前内部需要先做trim调整,调整完之后再对芯片进行测试,这是额外的时间支出。

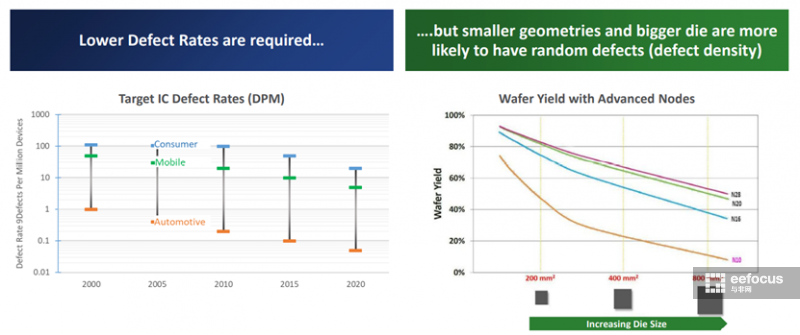

图 | 先进工艺带来了良率问题

除了时间成本的增加以外,先进工艺还会带来Wafer yield的挑战。当工艺尺寸不断缩减,初次yield对于wafer来说是不断下降的。此外,随着芯片的复杂化,每颗芯片的Die size不断增加,失效的概率也随之增加。当这两个因素一迭加,以800 mm²的die size wafer为例,初次yield不到10%。

但当我们从需求面去看时,却是截然相反的。众所周知,消费类芯片对失效率的容忍度是最高的,每百万颗芯片里面大概可以有100颗失效,也就是100个DPM。但是,从2020年开始有一个趋势,越来越多的消费类芯片被用到汽车里面去,一旦进入汽车场景,对于失效率的要求就会指数型增加,直接掉到10个DPM以下,甚至有些场景要求1个DPM。

这两种看似截然不同的趋势,实则告诉我们的是同一个需求,那就是ATE测试机一定要“测得准”。

“工位多”、“测得快” “测得准”,如何保障?

在半导体测试行业的人对泰瑞达的ATE设备肯定不陌生,比如测试偏简单芯片的低成本解决方案J750,测试复杂SoC芯片的UltraFLEX和UltraFLEXplus,以及测试功率半导体芯片的Eagle平台。值得一提的是,无论是J750、UltraFLEX还是UltraFLEXplus,用的都是同一套软件IG-XL。不同测试平台采用同一款软件的好处是在测试程序上可以做到兼容,对于熟悉某一种平台的工程师来说,不需要花费额外的时间熟悉一套新的套软件,提升了工作效率。

下面具体介绍一下UltraFLEXPlus。

得益于独创的PACE总线架构,UltraFLEXPlus与UltraFLEX对比,以纯数字芯片为例,单工位测试效率可以提升10-15%之间不等,且在这种架构下的每块板卡都是模块化、可升级的。

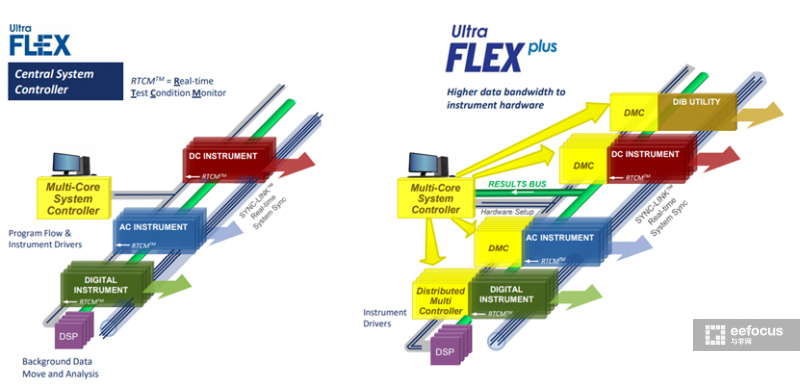

图 | PACE架构下的算力下放

那什么是PACE架构呢?简单的理解就是分布式计算控制下的算力下放,在原来的控制结构下,每块板卡的测量测试、计算、数据结果的传送都是是通过中间的工作站主控电脑来完成的,工作负重大。而对于新的PACE架构来说,依然有一台主控电脑,但是会把真正的板卡控制全部下放到每块板卡上面,因为每块板卡上面都有自己独立的CPU,在这上面可以完成所有指令的运行,最终只要通过RESULTS BUS传回主控电脑就可以了。根据统计,如果同时配合IG-XL软件,可以使工程开发时间从原来100%变成80%。

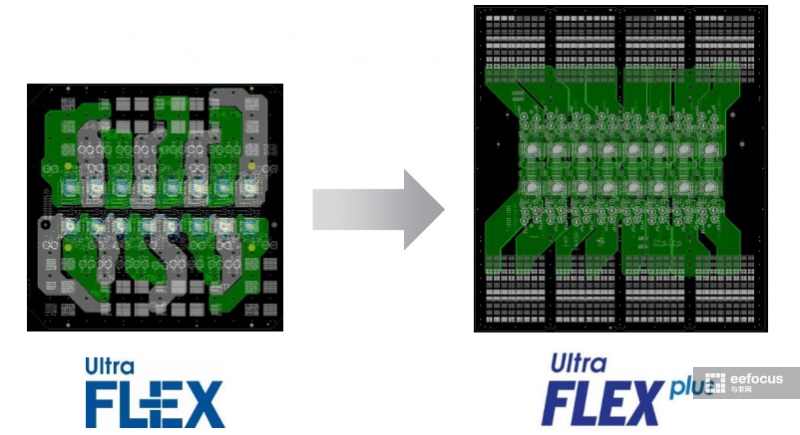

图 | 接口板的Broadside设计

此外,UltraFLEXplus还通过Broadside设计,在做大接口板应用区域面积的同时,由于采用了完全对称的Layout布局,减少了绕线的几率,PCB层数可以从60-70层降到50层左右,降低了加工难度,减少了失效率,保障了信号完整性和电源功率完整性,从而支持更多工位的同测。

值得一提的是,这个芯片测试接口板是根据每个芯片同测数需求专门设计的,因为芯片需要的数字通道、电源功率大小都是不一样的,所以属于专板专用。

总之,从上一代板卡UltraFLEX到新一代板卡UltraFLEXplus,无论是数据率,测量精准度,各方面指标都有极大的提升。

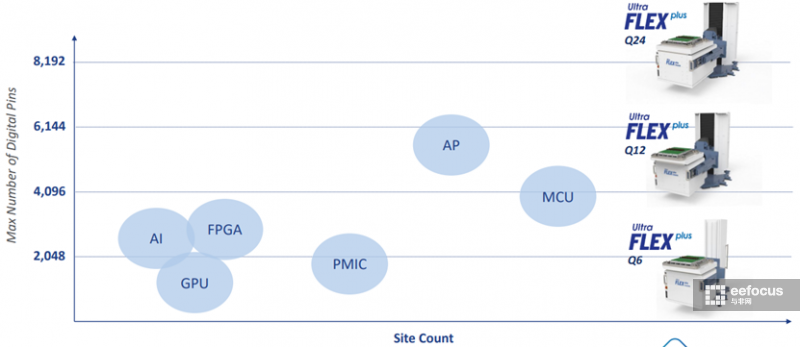

图 | UltraFLEXplus Q6、Q12和Q24选择参考

事实上,UltraFLEXplus根据最多容纳的数字通道的不同,可以分为Q6、Q12和Q24,这个数字代表的是卡槽数量,和同测能力线性相关。根据测试需求的不同,可以选择对应的ATE测试机台,比如AI、FPGA,测试芯片一般选用Q6就足够了,因为量没那么大,同测数要求不高;相对的,PMIC、MCU、AP手机处理器和简单数字芯片的同测数就更多一些,通常需要用到Q12;而对于5nm,甚至下一代2-3nm工艺的AP手机处理器来说,管脚会更多,如果要做到12-16工位同测,可能就要用到Q24。

1440

1440