1. 怎样的芯片算是好的芯片?

芯片的好坏,主要是由市场,性能和可靠性三要素决定的。首先,在芯片的开发前期,需要对市场进行充分调研,才能定义出符合客户需求的SPEC;其次是性能,IC设计工程师设计出来的电路需要通过designer 仿真,DFT电路验证,实验室样品评估,及样品出货前的FT,才能认为性能符合前期定义的要求;最后是可靠性,由于经过测试的芯片只能保证客户在刚拿到样品的时候是好的,所以还需要进行一系列应力测试,模拟客户端一些严苛使用条件对芯片的冲击,以评估芯片的寿命及可能存在的质量风险。

2. 芯片可靠性测试

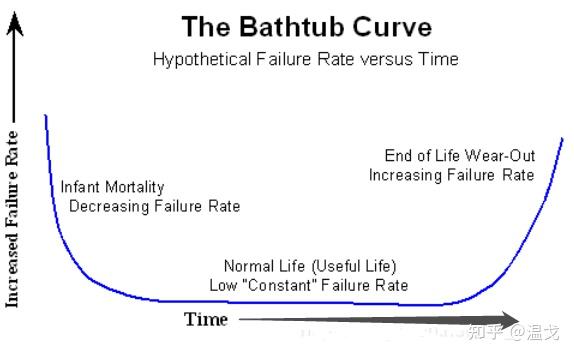

芯片的使用寿命根据浴盆曲线(Bathtub Curve),分为三个阶段,第一阶段是初期失效: 一个高的失效率。由制造,设计等原因造成。第二阶段是本征失效: 非常低的失效率,由器件的本征失效机制产生。第三个阶段: 击穿失效,一个高的失效率

浴盆曲线

可靠性实验就是通过施加应力,绘制出芯片的生命周期曲线,以便客户能在安全的范围内使用。

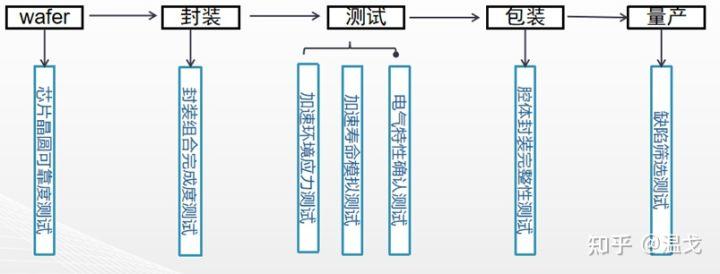

芯片在不同阶段要做的可靠性如下图所示:

对于新产品的可靠性来说,wafer,封装,包装和量产阶段的可靠性通常由对应的晶圆厂/封测厂把控,与旧产品之间的差异不大。新产品的可靠性需要重点关注的就是成品测试阶段的可靠性实验,下面针对这些可靠性实验进行简单介绍。

加速环境应力测试——主要考验产品封装的可靠性

- PC(precondition)

评估芯片在包装,运输,焊接过程中对温度、湿度冲击的抗性,仅对非封闭的封装(塑封)约束。模拟焊接过程高温产生内部水汽对内部电路的影响,是封装可靠性测试前需要进行的测试。

- HAST(Highly Accelerated Stress Test)

芯片长期存储条件下,高温和时间对器件的影响。仅针对塑封,分为带偏置(hast)和不带偏置uhast的测试,UHAST需要提前PC处理

- TC(temperature cycling)

检测芯片是否会因为热疲劳失效,TC也需要提前PC处理

高低温交替变化下机械应力承受能力,可能导致芯片永久的电气或物理特性变化

- HTSL(High temperature storage life test)

长期存储条件下,高温和时间对器件的影响,HTSL不需要做PC预处理

加速寿命模拟测试——主要考验产品电气可靠性

- HTOL(High Temperature Operation Life)

主要用于评估芯片的寿命和电路可靠性,可以用2种方式进行测试:DFT测试模式和EVA板测试模式。

- ELFR(early fail)

早期寿命失效率,需要的样本量比较大

- EDR(nonvolatile memory write/erase endurance,data retention and operational life test)

非易失性存储器耐久实验,仅针对包含该性能的芯片才需要验证

电气特性确认测试——主要考验产品的电气可靠性

- HBM(Human-Body Model)

模拟人体带电接触器件放电发生的静电放电模型

- CDM(Charged Device Mode)

模拟器件在装配、传递、测试、运输及存储过程中带电器件通过管脚与地接触时,发生对地的静电放电模型

- LU(latch up)

要是针对NMOS、CMOS、双极工艺的集成电路。测试正/反向电流和电源电压过压是否会对芯片产生锁定效应的测试。

任何一颗IC芯片,除了设计,流片,封装测试外,必须进行以上所述的可靠性验证。正常完成一批可靠性实验需要至少两个月的时间,而厂家至少需要测试3批次的可靠性才算将产品可靠性验证完成;此外,可靠性测试很多测试项需要在第三方实验室进行测试,测试板,测试座及测试费用都是一笔不小的开销。因此,可靠性测试可以称得上是一项耗时耗财的大工程。然而,正因为其测试项多,覆盖面广,所以才能保证客户使用的芯片足够可靠。因此,可靠性测试也是芯片生命周期中不可或缺的一部分。

723

723

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)