集成电路的历史从1958年TI的第一颗Flip-Flop电路开始,那时候只有两个晶体管组成一个反相器而已。发展至今已有十亿个晶体管的CPU了,而这些都不得不来自于半导体制造业的技术推进得以持续scalable。

半导体能够变成现实主要是它能够实现“0”和“1”的二进制转换,而在硬件上就是从真空二极管(Vacuum Tube)开始的。大概在第二次世界大战的时候,电子计算机开始投入适用主要用于通信密码破译,但是这些晶体管的性能会很快退化增加Trouble shooting的时间,间接阻碍了半导体行业的发展。

直到1947年,贝尔实验室的三位前辈其中一位是William Shockley他们发明了点接触的Ge晶体管,然后1950年,Shockley又发明了第一个BJT。这些和真空二极管比起来,可靠性和功耗以及尺寸都得到了很搭提高。尤其是BJT是三端晶体管可以当作电控开关(electrical switch),其中一个端子就可以作为控制端。1958年,TI的Jack Kilby在Silicon上做出了两个BJT,开启了“Silicon Age”。早期的电路都是用BJT做的,从BJT的原理可以直到,BJT是靠电流驱动的(Base加电流),而Ice又是双载流子器件,所以它除了驱动电流大之外,还有个问题就是静态漏电也大,所以如果你的电路非常庞大你的漏电功耗损失将无法接收,所以限制了它的适用。

再到1963年,仙童公司(Fairchild)公司发明了NMOS和PMOS对称互补器件组成的CMOS电路,这就是现在我们耳熟能详的CMOS技术。由于它的控制极Gate是靠栅极跨过Gate Dielectric电场耦合实现的,所以没有控制电流产生的静态功耗,所以理论静态功耗可以到“0” (当然实际上还是有Gate leakage)。实际上早期IC都是只用NMOS+BJT实现电路的,而没有用PMOS,因为那个时候没有Twin Well技术。直到1980年代CPU的晶体管已经到了几千个了,而这时候的功耗已经无法接收了,才不得不走入CMOS (Twin Well)时代。

接下来的年代就一直沿着1965年诞生的摩尔定律循规蹈矩的scaling了,带来速度、密度、性能的一次次提升。一路从Bulk-Si走到32nm走不下去了,才开始从Planar走向3D FinFET以及SOI技术。

MOSFET器件

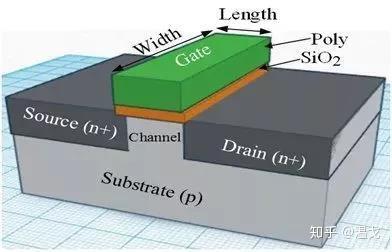

MOSFET来自Metal-Oxide-Semiconductor Field Effect Trasistor,Metal就是Gate栅极作为控制极的,而Oxide是栅氧作为场效应感应反型沟道的,Semiconductor自然就是衬底沟道的硅了,而Field Effect自然就是说它的工作原理了,它的控制极是靠栅极电压通过栅极氧化层感应产生反型沟道实现源漏导通,从而实现“0”和“1”的转换。

MOS结构

MOSFET是四端结构,分别是栅极、源极、漏极、和衬底(Body)。结构上面的栅极是低电阻的材料形成,他与衬底的沟道之间还要有个薄的栅氧化层。一般情况,源漏极是和衬底以及沟道相反的掺杂类型(比如NMOS的源漏是N-Type,而衬底和沟道就是P-type),所以源漏极之间因为各自的PN节就关闭了。但是当栅极加电压(NMOS加正电压,PMOS加负电压),通过栅极氧化层感应一个电场加在了沟道表面,所以衬底的少数载流子就被吸附到沟道表面累积并反型,最后变得和源漏极掺杂一样了,从而实现了源漏极导通。一般栅极的开启电压(Vt)会收到栅极与衬底的功函数以及栅氧的厚度/质量,还有衬底的掺杂浓度共同决定的。

为什么用Poly作为栅极材料

最原始MOSFET发明的时候用的栅极材料是金属铝,这就是为什么叫MOS,而不是POS了,哈哈。

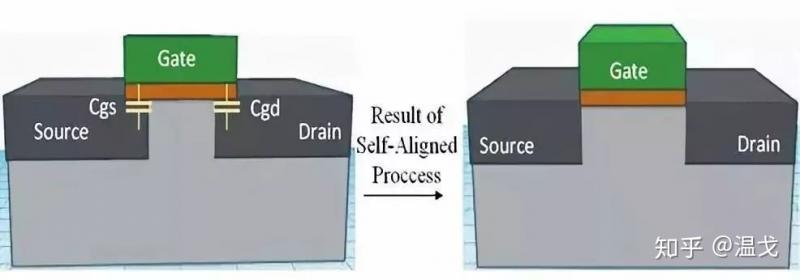

后来才发展到Poly了。主要是由于Metal Gate都是“Gate Last”制程,先做Source/Drain然后用铝做栅极gate,但是这样的问题是栅极和源漏必须要有一定的overlap确保栅极和源漏必须是链接起来的(一般2.5um的铝栅MOSFET的源漏Overlap是0.5um)。但是这样的overlay电容(Cgs/Cgd)导致了总米勒电容的增加电路速度的降低等。

解决栅极与源漏overlay电容的问题,就必须要用自对准的源漏,先做Gate然后用Gate做mask打Source/Drain的implant实现自对准,这就是“Gate-First”工艺。

而如果沿用原始的铝栅,则无法承受800C的高温(纯铝的熔点是660C,AlSiCu合金的熔点<500C)。所以才有了Poly作为“Gate-First”制程的栅极材料,但是Poly的电阻很高,所以后来有了doped poly。

也有说栅极材料换成poly的原因是功函数,Metal的功函数太高,使得Vt可以达到3~5V,这在以前的MOSFET可以接收,但是到submicron时代肯定不能接受了,所以可以用Poly通过doping来调节功函数进而调整Vt。

MOSFET的工作原理

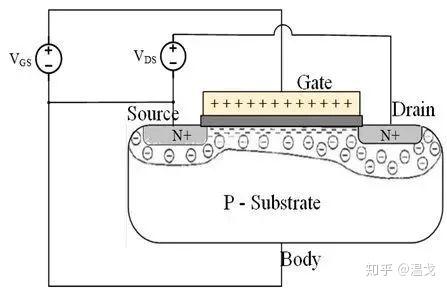

MOSFET的关键在于栅极,它控制着器件源漏的关闭和开启,所以它如同水龙头的开关。以NMOS为例(源漏为N-type,沟道和衬底是P-type),当栅极加正电压则衬底耦合感应出少数载流子到沟道表面直到沟道表面反型,使源漏连通起来。整个过程中源漏的N-type与衬底的P-type这两个PN结必须零偏或反偏(Source和Body接地,Drain接正电压),所以他属于PN结隔离型器件。

Small dimention Effect

引用《微机电系统基础》的一段话(Page-9),“不是所有的东西小型化之后性能都会变好,有些物理效应当尺寸变小之后性能反而变差。因为有些对于宏观范围器件可以忽略的物理效应在微观尺寸突然变得很突出,这就是比例尺定律。比如跳蚤可以跳过自身高度的几十倍,而大象却做不到”。

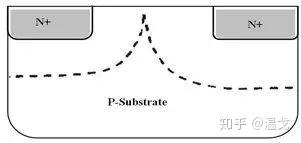

对于MOSFET来讲,当drain加反偏电压的时候,PN结的耗尽区变宽会延伸到沟道区,所以有效沟道长度Leff=Lpoly-2*Depletion,如果沟道长度足够长则Leff近似等于Lpoly,可是当Lpoly非常小的时候则耗尽区占Lpoly的比例则非常大而不可忽略,于是就有了短沟道效应。

接下来我们讨论等比例缩小带来的一些列问题:

载流子速度饱和以及迁移率下降

载流子在沟道里面的速度与沟道电场有关,当电场升高的时候,速度总会达到饱和的,这就是速度饱和效应,也就是为什么饱和区电流不随Drain电压的增加而增加了。而且在高电场下,载流子散射比较严重,也会导致迁移率下降,而且氧化层界面散射也会严重,所以载流子迁移率会进一步下降。

漏电压导致势垒降低

另外一个短沟带来的问题就是Drain端电压改变了沟道表面势垒,使得Vt降低。长沟器件的沟道势垒是由栅极电压Vg决定的,但是短沟器件的沟道势垒是由栅源电压(Vgs)和栅漏电压(Vgd)决定的。如果漏极电压升高,漏极PN结耗尽区会横向延伸进入gate下面,所以在Vg比较低的情况下,沟道表面势垒由于电场增加而降低,使得载流子还是能溜过去,这也叫亚阈值漏电(Subthreshold Leakage)。具体可见《MOS器件理论之–DIBL, GIDL》。

源漏穿通

这个我感觉和DIBL没什么差别,也是Drain端电压带来的问题,耗尽区宽度延伸进入沟道和源极的耗尽区不小心碰到一起了。和DIBL不一样的是,一个是针对沟道势垒而改变Vt,一个是针对源极导致漏电的。

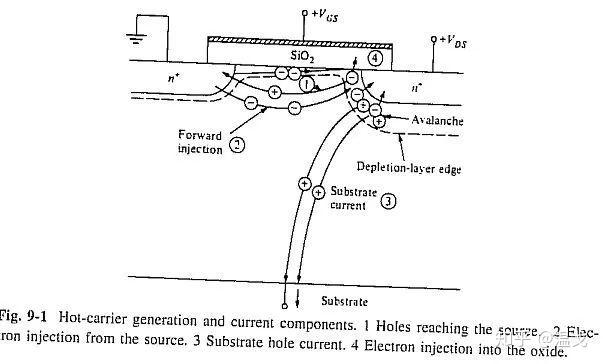

热载流子效应

这个也是一个道理了,沟道长度减小,沟道电场增加,如果Drain电压增加,使得导致耗尽区延展,靠source更近了,也会进一步使得源漏横向电场增强,所以沟道载流子碰撞激烈,产生很多的电子空穴对,而这些电子空穴对在栅极电压下的驱使下进入衬底形成Isub。那为啥叫热载流子呢?因为电场增加导致载流子加速,动能增加所以电子温度升高了,只是你感受不到而已,那为什么通常都是NMOS比PMOS厉害呢,因为NMOS是电子,质量小速度快,而PMOS是空穴质量大速度小,而动能E=1/2*m*v^2,所以速度才是dominate。

Scaling时代的创新

迁移率加速器: 应变硅(Strain Silicon)

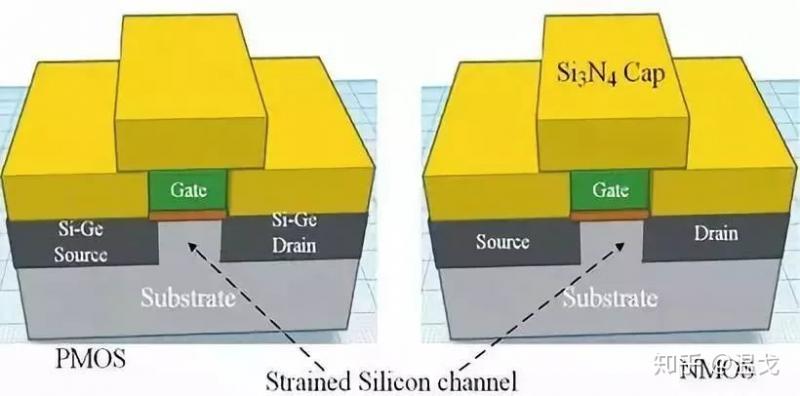

前面提到了当器件缩小带来的载流子迁移率下降问题,也不是无解。我们可以在沟道里用薄薄的锗(Ge)材料来提高载流子迁移率,或者试用应变硅引入沟道应力来提升沟道载流子迁移率。而应变硅技术包括使用张应力(Tensile)和压应力(Compress)来提升载流子迁移率从而得到晶体管性能的提升,比如PMOS的空穴载流子就可以通过channel的压应力来实现,这在45nm以下的时候就开始采用了 《Strained silicon — the key to sub-45 nm CMOS》。

对于制造沟道应变硅,需要在源漏区域外延填充Si-Ge层(20%Ge + 80% Si混合),由于Ge原子比硅原子大,所以产生了推向沟道的压应力,从而使沟道的空穴载流子迁移率提高,进而提高了电流驱动能力和电路速度。这种技术最早是Intel在2003年用于90nm CMOS上,PMOS电流驱动能力提升25%。而这种源漏嵌入Si-Ge技术称之为e-SiGe (Embedded-SiGe)技术,但是Si-Ge应变硅技术只能提升PMOS,而NMOS怎么办呢?对于电子必须要有Tensile的Stress才能增强它的载流子迁移率,把SiGe嵌入到源漏肯定不行了,那就把他嵌入到沟道下面也可以产生Tensile应力,但是这种工艺的实现难度几乎不可能,所以后来就有了在NMOS周围增加一个Si3N4,来产生额外的应力。这种方法可以让器件全部产生Compressive应力也可以全部产生Tensile应力,当然也可以分别对PMOS产生Compressive而对NMOS产生Tensile,但是用这种SiN产生的应力的晶体管对Poly Space的mismatch影响特别大(原因我还不知道。

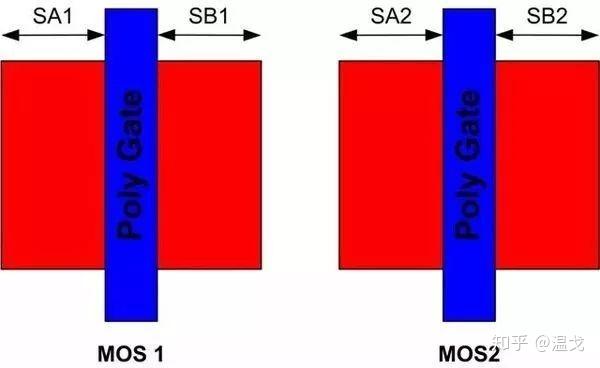

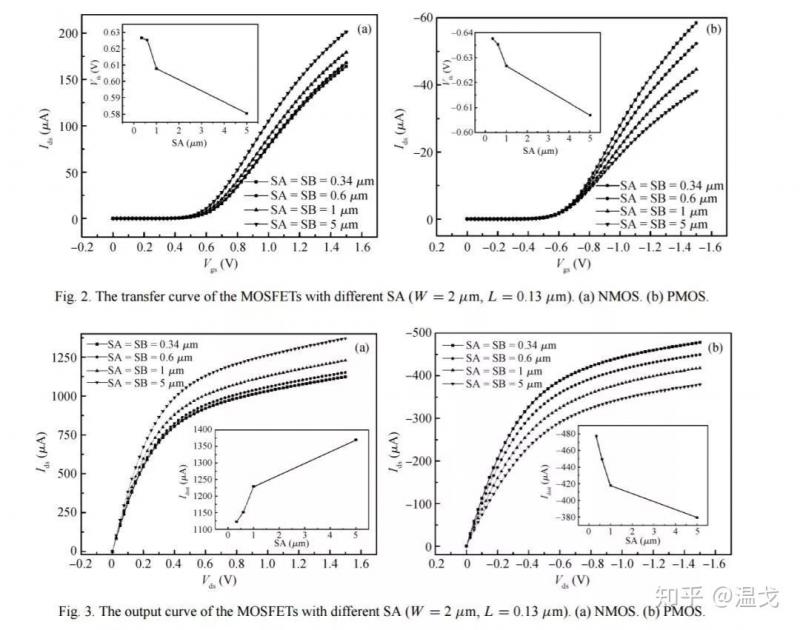

说到了应变硅,这貌似都是12寸的理论,离我们很遥远吗?其实8寸也有这个问题,我们0.18um及其以下技术都有个效应叫做LOD (Length of Drain/Diffusion),意思就是说沟道长度“L”的方向上有源区边缘离沟道边缘的距离对器件电流的影响,就是如下图的SA和SB,这个器件影响在SPICE仿真里面在BSIM 4.0以上的模型就有了,所以在Analog电路仿真非常care mismatch的时候(如: Current mirror, Differential pair,ADC/DAC等电路)一定要带入参数SA和SB,不要到时候又要来complain fab说mismatch不好。

原因是啥呢?主要是因为旁边都是STI,里面的HDP Oxide产生了compressive应力,所以按照e-SiGe的理论,PMOS的载流子迁移率会变大,而NMOS的载流子迁移率会变小,所以PMOS饱和电流会变大,NMOS的饱和电流会变小,如下图I-V curve。

那接下来的问题是,如果我SA和SB全部画成一样不就好了吗?模拟的世界你永远不懂!

假设如下图一个MOS有两个Gate组成的multi finger呢?这里就更复杂了。。。。这里需要SA11=SA21、SB11=SB21、SA12=SA22且SB12=SB22,MOS1才能等于MOS2。

如果再进一步把MOS1和MOS放到一个大OD上去呢?里面就没有问题了,可是最外面的SA和SB怎么办?如何消除LOD的影响?只能把OD拉大了,通常是SA或SB>=5um即可,或者最外面的MOS不要用,也就是dummy gate。

所以说device里面STI的引入会带来mismatch的原因知道了吧?

栅极漏电:High-K

栅极氧化层的厚度随着等比例缩小也一直减薄,到65nm的时候需要有效栅氧厚度(EOT)接近23A( phsical 16A),再往下将就比自然氧化层还薄了,direct tunnel (Quantum Mechanical Tunneling)漏电根本无法承受。回过头来想,我们为什么要薄?因为我们要得到更高的夸导来感应沟道反型,那夸导来自于什么?公式自己查一下就知道了来自于电容,要提升电容你要么降低厚度,要么提高介电常数,既然降低厚度走不下去了,那就换介电常数吧。于是就有了High-K栅极介电材料。

High-K栅极材料的突破的突破来自于2007年,首次发明于Intel的45nm采用了HfO2 (Hafnium),它的介电常数是25,而我们的SiO2是3.9,自己比一下吧。

多晶耗尽效应: Metal Gate

我记得我以前的文章有讲过HKMG,栅极材料如果是多晶,那么它的掺杂是随着栅极电压会发生改变的,栅极底部靠近栅氧的掺杂会被电场吸上去,而底部近似不掺杂的poly会变成绝缘体,被计入栅极氧化层厚度里,导致夸导降低。当然除了改用High-K材料外,还有就是换金属栅极,当然不能是铝,后面源漏激活的高温受不了。所以必须是难熔金属,而且必须有合适的功函数,否则Vt就守不住了。

和High-K材料一样,Metal Gate也是Intel率先在45nm上引入量产的,还是Intel牛啊。

器件结构的创新

上面讲的都是传统的MOS结构,一直缩小遇到的各种问题及解法。但是总有黔驴技穷的时候,所以该结构势在必行!也就是现在流行的SOI和FinFET技术。主要目的就是最大化Gate-to-Channel电容并且最小化Drain-to-Channel电容。

SOI技术

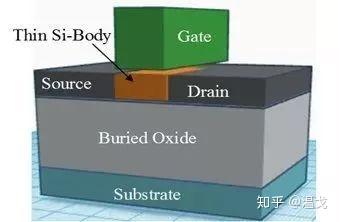

和传统MOS最大不同是Well底部有个Oxide隔离着,所以叫做Silicon-on-Insulator (SOI),所以它还是传统的Planar结构。它的结构分三部分,上面的Silicon是器件部分,中间的Oxide是Insulator隔离作用,底部的硅是支撑用的,也叫“Handle Silicon”。

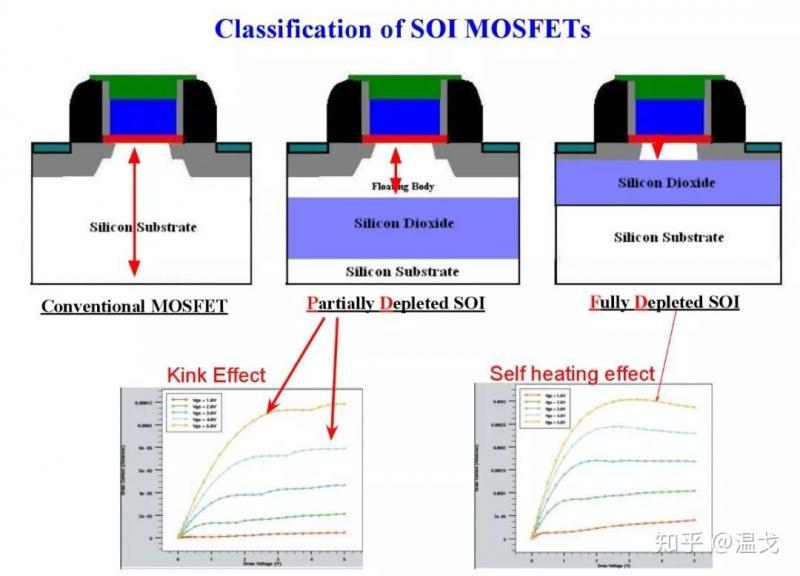

MOS结构上看有两种,一种叫做PDSOI,一种叫FDSOI。前者是表面硅的厚度几乎等于PN结深度,所以源漏PN结靠近Well的耗尽区就被Buried Oxide隔离掉了,所以传统的PN结隔离该用了Oxide绝对隔离了,所以漏电非常小,寄生电容也变小了,所以电路变快了。但是这种器件当栅极耗尽并反型的时候,表面沟道只有一两百埃,所以沟道下面的硅还有一部分属于Well/Bulk,所以这种SOI技术叫做部分耗尽SOI (PDSOI: Partial Depleted)。

那问题就来了,PDSOI的Bulk四周都被隔离了,Bulk的电极如果不接出去的话会带来什么问题?对,浮体效应(Floating Body Effect),所以Vt会拉低,电流会拉大,所以IV curve上你会看到包河区电流上翘,这就是Kink-Effect)。当然如果要解决的话就是把衬底想法接出去即可,只是牺牲点面积而已。那么要解决衬底浮体的问题,又不想多接Bulk那怎么办呢?也好办,让整个反型区全部耗尽即可,也就是FDSOI (Fully depleted),这样结电容更小了,所以更快了,也叫RFSOI了。但是它也不是免费的午餐,这么薄的SOI (~200A)上的Silicon,制作工艺非常难,而且Silicon与下面的BOX的interface的漏电会导致沟道漏电的哦,还有这个沟道的self-heating会很严重。

FinFET

最后讲一下SOI和FinFET,SOI如果能够取代FinFET,那自然是好,毕竟它还是Planar技术,比较成熟。而且它还可以通过back-gate加上BOX来控制Vt,这在multi-Vt以及low power领域都是有优势的。

未来,让我期待更先进的器件结构及制造技术,技术远不止于此!比如碳纳米管, nano-wire FET, FinFET+化合物半导体,等等。

8.3万

8.3万

下载ECAD模型

下载ECAD模型

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)