在现代科技领域,嵌入式系统接口作为信息交互的核心枢纽,扮演着不可或缺的角色。各类接口通过标准化的通信协议与规范,实现了设备间的高效数据传输与智能协同。作为嵌入式开发的核心技术之一,接口的深入理解与熟练运用直接决定了嵌入式系统的功能实现与性能优化。本文将以SPI(Serial Peripheral Interface)接口为切入点,详细剖析其工作原理与技术特点,旨在为屏幕前渴望掌握嵌入式开发的小伙伴构建一个全面的接口知识体系。

一、基本概念

SPI的全称是Serial Peripheral Interface,译为串行外设接口。它是一种高速的,全双工,同步的通信总线,广泛应用于嵌入式系统,用于控制器和各种外围设备之间的数据传输。SPI接口具有全双工通信、传输速度快、协议简单等特点,因此在许多需要高效率、短距离的通信场景中使用。SPI接口经常被称为4线串行总线,以主/从方式工作,数据传输过程由主机初始化。4条线号线如下:

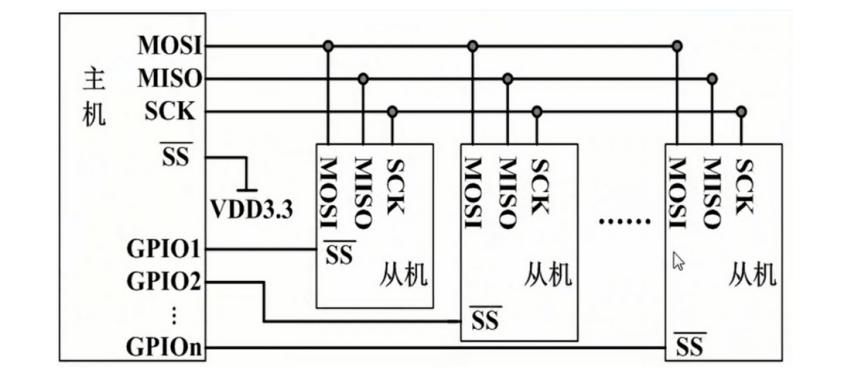

SPI采用主从模式,通常由一个主设备(Microcontroller等控制器)和一个或多个从设备组成。

在通信过程中,由主设备来控制从设备,主设备负责生成时钟信号,通过SCK引脚提供给从设备,用于同步数据传输。主设备通过MOSI向从设备发送数据,同时通过MISO从从设备接收数据,数据传输是双向的。

在SPI总线上,当一个主机和多个从机进行通讯时,主设备使用SS信号选择一个从设备进行通信,只有被选择的从设备会响应主设备的指令,其余从设备则保持不响应状态。

二、工作模式

SPI通常有四种工作模式(0、1、2、3),主要区别在于时钟极性(CPOL)和时钟相位(CPHA)的不同设置,决定了时钟信号在何时进行电平翻转和数据采样。

CPOL:时钟的极性;表示SPI在空闲时,时钟信号是高电平还是低电平。

CPHA:时钟的相位;表示SPI设备是在SCK管脚上面的时钟信号变为上升沿时触发数据采样,还是在时钟信号变为下降沿时出发数据采样。至于跳变沿是上升沿还是下降沿,取决于CPOL。

主设备会根据将要交换的数据来产生相应的时钟脉冲,时钟脉冲组成了时钟信号,时钟信号通过时钟极性和时钟相位控制着两个SPI设备之间核实数据交换以及何时对接收到的数据进行采样,来保证数据在两个设备之间是同步传输的。SPI主设备与通信的从设备时钟相位和极性应该一致。主设备SPI时钟和极性的配置应该由外设决定。

CPOL跟CPHA的不同组合构成了SPI总线的四种不同模式:

|

模式 |

CPOL |

CPHA |

|

MODE0 |

0 |

0 |

|

MODE1 |

0 |

1 |

|

MODE2 |

1 |

0 |

|

MODE3 |

1 |

1 |

模式0(CPOL=0,CPHA=0):

CPOL=0:空闲时候为低电平,第一个跳变沿是上升沿,第二个跳变沿是下降沿。

CPHA=0:数据在第一个跳变沿(上升沿)采样。

模式1(CPOL=0,CPHA=1):

CPOL=0:空闲时候为低电平,第一个跳变沿是上升沿,第二个跳变沿是下降沿。

CPHA=1:数据在第二个跳变沿(下降沿)采样。

模式2(CPOL=1;CPHA=0):

CPOL=1:空闲时候为高电平,第一个跳变沿是下降沿,第二个跳变沿是上升沿。

CPHA=0:数据在第一个跳变沿(下降沿)采样。

模式3(CPOL=1;CPHA=1):

CPOL=1:空闲时候为高电平,第一个跳变沿是下降沿,第二个跳变沿是上升沿。

CPHA=1:数据在第二个跳变沿(上升沿)采样。

关于SPI接口就介绍到这里,衷心希望这些内容能为屏幕前努力学习嵌入式开发的小伙伴带来实质性的帮助与启发。

芯耀

芯耀

1595

1595