在当今的许多高频系统中,关键规格的实现不仅需要对器件本身进行精确优化,还需要对其所有外围模块进行优化。为了获得最佳结果,必须对所有这些组件有透彻的理解并设计出良好的系统。这在射频采样模数转换器(ADC)的应用中尤其如此,其中采样时钟可能会使用高性能合成器来生成具有极低噪声的高频时钟信号。

这些合成器需要经过精心设计,以获得最佳的集成噪声性能,因为这会直接影响ADC的信噪比(SNR)性能。本应用报告有助于理解这些性能规格,展示了如何进行优化过程,并提供了有助于达到最高性能水平的相关信息。

1、ADC的SNR

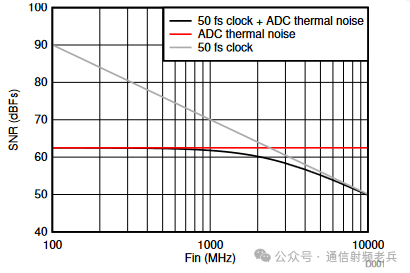

ADC的信噪比(SNR)是一项关键规格。该规格的高数值表明ADC能够更好地区分所需的输入信号和在采样过程中同时捕获到的不需要的噪声。ADC的SNR主要有三个贡献因素:ADC的量化噪声和热噪声(不随输入频率变化)以及时钟抖动(取决于频率)。图1-1显示了一个ADC热噪声为62.5 dBFs和时钟SNR(时钟抖动tclock_jitter为50 fs)的示例。时钟的SNR可以通过知道信号的频率和抖动(在第2节中讨论)并使用公式1来推导得出:

![]()

如图所示,ADC的高信噪比(SNR)在低输入频率时得以保持,但在较高输入频率时,时钟SNR开始成为主导因素。

图1-1 ADC和时钟jitter对SNR的贡献

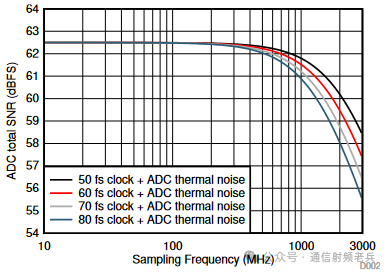

既然已经了解了当时钟抖动为50fs时,时钟抖动对总信噪比(SNR)的影响,接下来我们来看性能较低(抖动较高)的时钟所产生的影响。如图1-2所示,时钟的抖动越高,在ADC输入频率较高时,时钟性能对SNR的劣化影响就越严重。因此,确保时钟抖动尽可能低至关重要,并且可以根据高频合成器时钟源的不同参数调整这一规格,以实现最佳的低抖动值。

图1-2 不同时钟jitter对总的SNR的影响

2、理解相位噪声、抖动和信噪比(SNR)

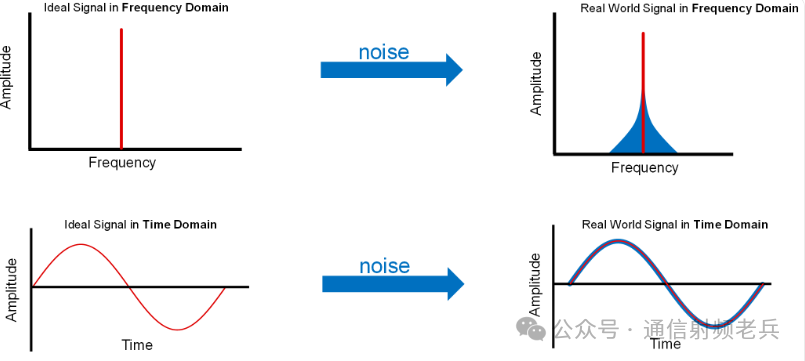

为了设计和找出最低的抖动,首先需要了解来自合成器的时钟信号的相位噪声。在时域中,理想的正弦波时钟信号看起来像图2-1左下角的波形。然而,在现实中,由于频率合成器组件的实际不完善性,会产生额外的噪声,使波形偏离其理想位置。同样地,将相同的正弦波转换到频域中,它在振荡频率处表现为一个单一的脉冲。噪声的增加以相位噪声的形式出现(位于理想脉冲旁边的裙边)。合成器的低相位噪声意味着信号更纯净,性能更好,并且最终用于为ADC提供时钟时抖动更低(将在第3节中讨论)。

图2-1 时域和频域中的相位噪声

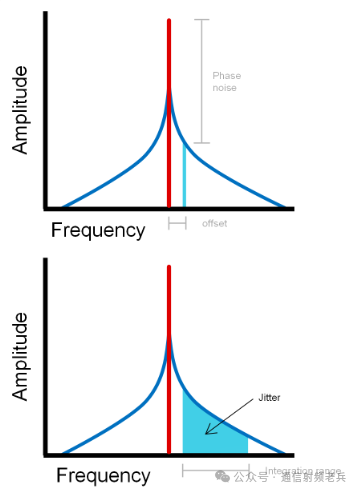

相位噪声定义为(在偏离振荡信号某一频率处,带宽为1赫兹的)噪声与振荡信号幅度之比。积分噪声本质上是振荡信号在定义范围内的所有偏移频率上相位噪声的总和(见图2-2)。抖动是通过使用积分噪声和信号频率,根据公式2推导得出的:

![]()

所选择的积分范围非常重要。这由ADC的采样设置决定。积分范围的下限(更接近振荡信号)由[采样率]/[FFT大小]的一半决定。例如,在采样率为2949.12 MHz、FFT大小为65536的情况下,积分范围下限可达22.5 kHz。因此,积分范围下限越低,较低偏移处的相位噪声就越重要。

图2-2 相位噪声和jitter的定义

3、最低抖动jitter的设计

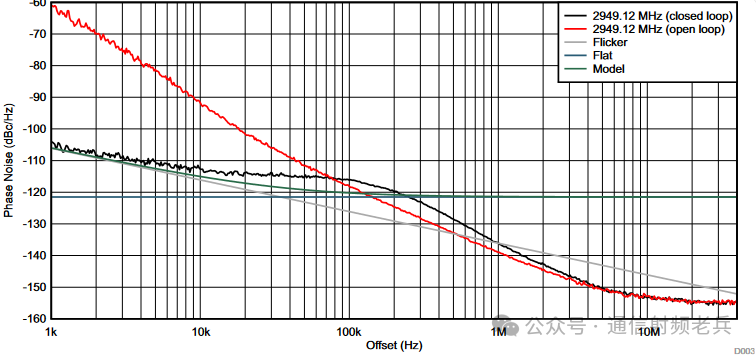

现在我们专注于如何使ADC时钟源的抖动尽可能低。图3-1显示了输出频率为2949.12 MHz时的相位噪声图。黑线表示闭环(锁定)相位噪声,红线表示开环(自由运行VCO)相位噪声。此外,PLL噪声由闪烁噪声分量(灰线)和平坦的PLL噪声基底分量(蓝线)建模。这两条线的总和即为PLL噪声。环路带宽(相位噪声开始滚降的位置)大约在100 kHz偏移处。如果环路带宽较低,VCO噪声会推入到较低偏移的相位噪声中;如果环路带宽较高,它可能会将PLL相位噪声推入到VCO区域。

通常,为了设计具有最低抖动的环路滤波器,PLL噪声模型与VCO相交的点是最优点(在本例中约为120 kHz)。这个环路带宽由时钟源的环路滤波器组件决定,或者在这种情况下,由RF合成器(集成PLL+VCO)决定。

图3-1 包含58fs jitter的2949.12M采样时钟

4、影响抖动jitter的因素

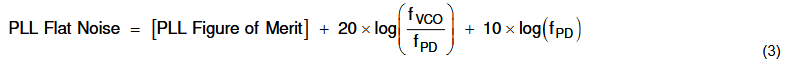

合成器的相位噪声主要是由相位锁定环(PLL)和压控振荡器(VCO)共同决定的。数据表上能告诉你能实现多低抖动的规格参数是归一化PLL噪声基底(PLL品质因数)、归一化PLL闪烁噪声(每十倍频变化10 dB)以及数据表上的VCO开环相位噪声。PLL品质因数和闪烁噪声分别在公式3和公式4中描述。从公式3中可以看到的关系是,fPD加倍基本上会使[20 × log]部分减少6 dB,而使[10 × log]部分增加3 dB,所以总体上PLL平坦噪声减少3 dB。这是改善PLL贡献的相位噪声的方面之一。

其中:

• fPD 是合成器的相位检测器频率

• fVCO 是压控振荡器的频率

![]()

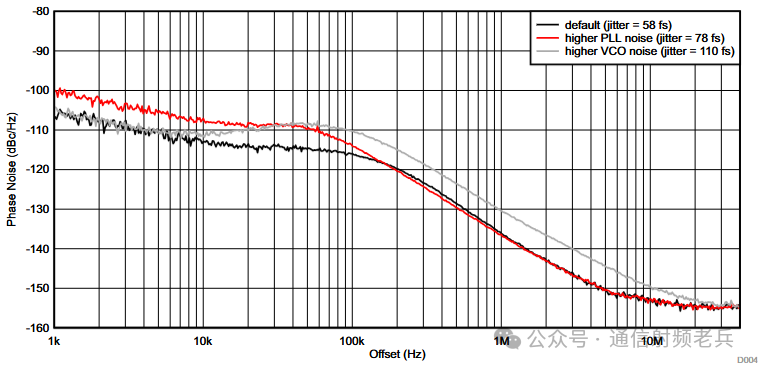

在图4-1中,黑线表示原始相位噪声,对应的抖动为58 fs。但如果PLL相位噪声较差,如红线中平坦部分所示有所上升,抖动就会增加(本例中为78 fs)。VCO相位噪声也有很大影响。观察灰线,在这种情况下,VCO相位噪声退化,导致抖动增加到110 fs。通过选择一个在这两个方面性能都良好的器件,然后为合成器设计一个性能优异的环路滤波器,以在环路带宽附近获得最佳的相位噪声响应,可以优化抖动至最低,从而为ADC提供最高信噪比(SNR)的时钟信号。

图4-1 PLL和VCO的相位噪声贡献

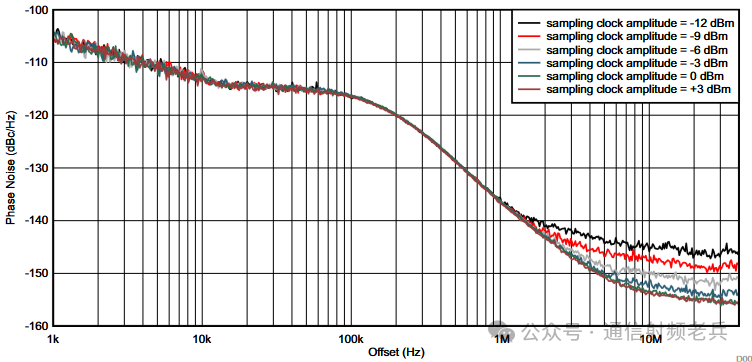

在信号幅度方面也有改善合成器抖动的考虑,因为信号幅度会影响噪声基底,从而影响由较高偏移引起的抖动。这一现象可以通过利森(Leeson)方程来观察,其中相位噪声水平基底随信号源的输出功率以(1/Ps)的因子变化。在某个点上,时钟源的噪声基底将占据主导地位,此时抖动将不再进一步改善(如图4-2所示,大约在0dBm左右)。因此,时钟源的幅度应设计至少达到这一水平。因此,需要一种具有极低噪声基底以及能够输出更高功率以达到该噪声基底水平的合成器器件。如前面关于抖动积分范围的讨论所述,上限越高,这种高偏移相位噪声对整体抖动的影响就越大。

图4-2 采样时钟幅度

芯耀

芯耀

3067

3067

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍