i.MX RT700系列提供了高性能、高集成度、先进功能和高能效的优化组合,为支持智能AI的边缘端设备赋能,例如可穿戴设备、消费电子医疗设备、智能家居设备和HMI设备。

在i.MX RT500和i.MX RT600跨界MCU的成功基础上,恩智浦宣布推出i.MX RT700,超低功耗、集成多核和eIQ® Neutron神经处理单元(NPU)。

新一代i.MX RT700系列组合了前两个系列的优势,进一步降低了功耗,同时通过增加内核和其他架构增强功能提高了性能:

- 集成了恩智浦eIQ Neutron NPU AI/ML加速器

- 高达7.5MB的低功耗内部SRAM阵列,具有30个分区,可实现卓越的多核访问

- 新的图形加速器包括硬件JPEG和PNG解码,以及矢量图形引擎和MIPI-DSI接口

- 与前几代产品相比,功耗降低了70%

- 1.2V低功耗eUSB标准支持,允许与标准USB2.0设备进行交互

i.MX RT700概述

i.MX RT700针对需要高性能感知、DSP和计算能力的深度嵌入式应用,同时保持低功耗特性以延长电池寿命。

带有eIQ® Neutron NPU的多核架构

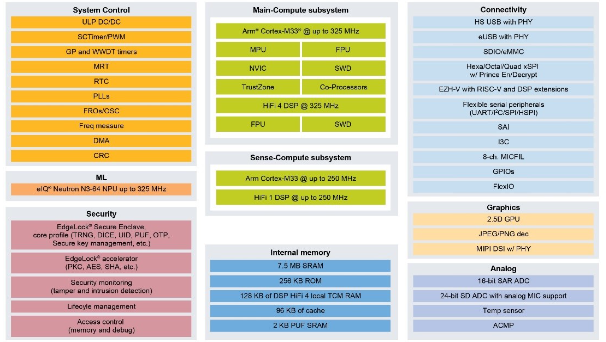

全新的i.MX RT700 CPU架构由高性能主计算子系统、以及“always-on”感知计算子系统和专用协处理器组成。

i.MX RT700结构框图

主计算子系统使用运行频率为325MHz的Arm®Cortex®-M33(CM33)核。与i.MX RT600跨界MCU一样,i.MX RT700包括Cadence Tensilica®HiFi 4 DSP。HiFi 4是基于超长指令字(VLIW)架构的高性能DSP内核,每个指令周期最多可处理8个32x16 MAC。它可用于分流对性能需求较高的信号处理任务,如音频和图像处理,并支持定点和浮点运算。

CM33用作通用执行平台,在系统启动时便可使用。它处理HiFi 4 DSP以及其他协处理器和外部存储器接口的初始启动。低功耗感知计算子系统由另一个250MHz的CM33核和低功耗Cadence Tensilica®HiFi 1 DSP组成。它主要用于需要始终在线的应用,能够访问为超低功耗运行而调整的选定数量的通用外设。应用包括PDM麦克风接口的唤醒词检测、实时传感器集线器和BLE音频处理。

为了支持人工智能和机器学习模型加速,i.MX RT700集成了eIQ® Neutron NPU。eIQ® Neutron是一种可扩展的硬件加速器架构,恩智浦专为人工智能和机器学习应用构建的多款产品均采用了该架构。

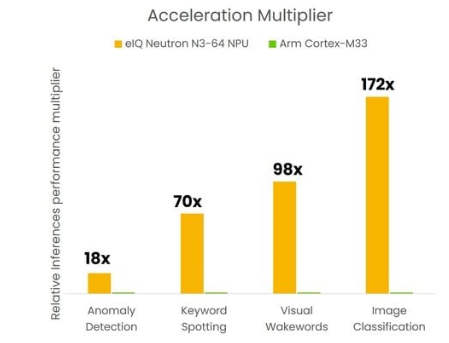

eIQ Neutron NPU加速倍增器

i.MX RT700采用eIQ Neutron N3-64 NPU,其性能介于MCX N947 MCU中的N1-16和高端i.MX 95应用处理器中的N3-1024之间。该NPU已针对深度嵌入式、低功耗应用进行了调优,与通用处理器相比,可以实现172倍的性能提升,同时每次推理的功耗只有其119分之一。

eIQ机器学习软件开发环境可为使用恩智浦eIQ Neutron神经处理单元开发AL/ML应用提供支持。该工具集为开发人员提供了一个工作流程,帮助他们将TensorFlow Lite等常见机器学习框架的代码转换为可以在NPU上加速的同等计算图。

i.MX RT700中另一个有趣的处理资源是基于开放式RISC-V指令集架构(ISA)的全新EZH-V IO协处理器。

EZH-V中的RISC-V ISA已实现了扩展:

- 添加硬件乘法和除法功能

- 添加浮点功能

- 添加位操作功能

- 提高了代码密度

EZH-V可以执行用于后处理图形数据的“SmartDMA”任务,并作为GPU、CPU和FlexIO与MIPI DSI等硬件接口之间的高速数据操作桥。它还可以用于任何其他通用IO任务,并连接到GPIO和大多数片上外设的多种触发输入。EZH-V的代码使用基于RISC-V LLVM的工具链开发,该工具链将在MCUXpresso SDK中提供。

面向处理、图形和存储的复杂内存架构

i.MX RT700中的内存架构针对不同内部处理资源之间灵活、低争用的互连进行了优化。一个7.5MB的大型SRAM阵列分为30个分区,每个分区都可由总线控制器访问,以减少CM33核、HiFi DSP、DMA控制器和EZH-V之间的争用。大型内部存储器可以快速访问大型图形帧缓冲区,并能够连接到内置的硬件JPEG和PNG解码器。

30个独立的SRAM分区都可以单独用于代码或数据存储,专用于CPU,或在各个内核之间共享。每个分区都可以独立地置于低功耗保留模式或完全断电状态。

有两个XCACHE模块用作专用系统和代码缓存,可由计算子系统主用CM33核、HiFi 4、EZH-V和两个eDMA外设实例访问。这些缓存可以显著提高访问外部存储器时的性能。HiFi 4有自己的本地紧耦合存储器(TCM)以及本地指令/数据缓存,用于放置性能关键的DSP。

外部存储器支持

与之前的i.MX RT500和i.MX RT600器件一样,i.MX RT700采用了不带闪存的架构。已包含3个xSPI外部存储控制器,用于与四线和八线闪存连接。其中两个xSPI实例支持与外部PSRAM连接的16位接口,用于添加非易失性存储器。

xSPI接口支持高达400MHz DDR和200MHz SDR传输。这样可以为大型ML模型、数据缓冲区和图形资产添加大块快速外部RAM。通过xSPI控制器连接的外部存储器可以通过系统内存映射进行访问。代码可以从外部连接的闪存就地执行(XIP)。xSPI接口被缓存,以确保最高性能。

xSPI控制器内置了一个灵活的基于查找表(LUT)的命令引擎,适用于几乎任何NOR闪存。i.MX RT700 Boot ROM可以使用连接到xSPI接口的闪存来启动系统。有几个选项可供选择,包括将启动代码复制到内部SRAM或直接就地执行(XIP)。加密代码可以在从外部闪存访问时即时解密。

大容量存储器可以通过SHDC/eMMC控制器连接。i.MX RT700的Boot ROM还支持从eMMC/SD卡启动系统。这使得SD/eMMC存储器既能启动i.MX RT700,又可用于存储配置和图形资产的典型文件系统。

面向空间受限产品的封装

i.MX RT700将提供324引脚7.3x7.3mm、0.4mm间距的扇出晶圆级(FOWLP)和256引脚6.025x6.025mm、0.35mm间距的晶圆级芯片级(WLCSP)两种封装。这些封装使设计人员能够将i.MX RT700嵌入到空间受限的区域。

适用于可穿戴设备和个人健身应用

高性能、超低功耗和密集封装技术能够显著提升可穿戴设备、个人健身设备、消费电子医疗设备和增强现实应用的性能和用户体验。

采用i.MX RT700的超低功耗、深度嵌入式设计

i.MX RT700代表着低功耗嵌入式处理技术的重大进步。i.MX RT700具有超低功耗和高处理能力,适用于许多需要长电池寿命的应用,同时通过专用图形加速器提供卓越的用户体验。

多核架构使设计人员能够灵活地进行产品设计。i.MX RT700组合了通用内核与高性能DSP以及强大的NPU,能够实现嵌入式产品差异化。

芯耀

芯耀

1177

1177