晶发电子专注17年晶振生产,晶振产品包括石英晶体谐振器、振荡器、贴片晶振、32.768Khz时钟晶振、有源晶振、无源晶振等,产品性能稳定,品质过硬,价格好,交期快.国产晶振品牌您值得信赖的晶振供应商。

在现代电子设备中,晶振作为提供稳定时钟信号的核心组件,其稳定性对整个系统的运行至关重要。然而,电路抗扰性不良往往会导致晶振失效,进而影响设备的整体性能。晶发电子针对这一问题,提出了以下关于晶振电路抗扰性及优化方案的分析和建议。

电路抗扰性不良的影响

晶振电路的抗扰性差意味着设备在运行过程中容易受到外部和内部因素的干扰。以下是两种主要的干扰源:

1. 电源噪声

电源噪声是影响晶振电路抗扰性的重要因素。它不仅会导致晶振频率的波动,进而引发失效,还可能对电路中的其他元件造成不良影响,进一步加剧系统的故障。

2. 电磁干扰

电磁干扰(EMI)是另一个不容忽视的问题。电子设备中的高频信号源可能会产生电磁干扰,影响晶振的正常工作。

提升电路抗扰性的优化措施

为了确保晶振电路的稳定性和可靠性,晶发电子建议采取以下优化措施:

1. 加强电源线路的过滤与保护

2. 优化地线和电源线路布局

-

良好地线设计: 合理设计地线,降低地线阻抗,减少地线噪声。地线应尽量宽且短,避免形成地环路。

-

屏蔽和隔离措施: 使用屏蔽罩、隔离层等手段,降低电磁干扰对晶振电路的影响。

3. 隔离其他干扰源

-

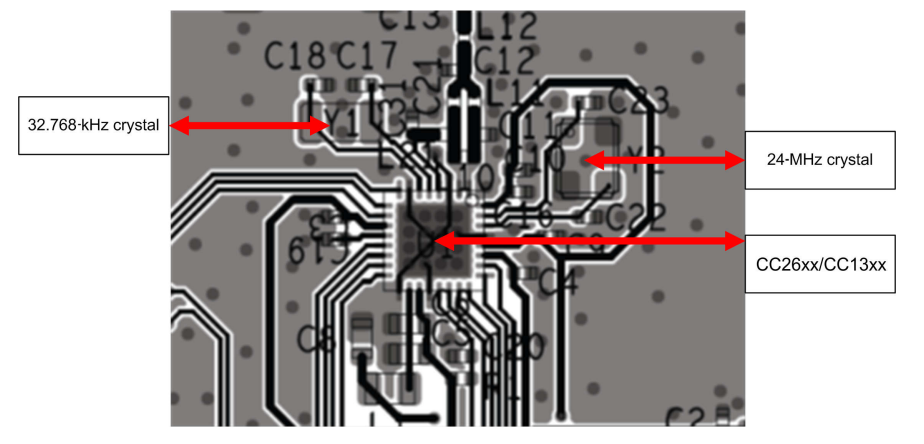

物理距离隔离: 将晶振与高频信号源、电磁辐射源等干扰源保持一定的物理距离,减少干扰。

-

断开干扰路径: 在设计过程中,尽量避免晶振电路与其他可能产生干扰的电路直接相连,以降低干扰风险。

通过上述措施,可以有效提升晶振电路的抗扰性,确保电子设备在各种环境下都能稳定运行。晶发电子的建议为电子工程师在设计和维护晶振电路时提供了宝贵的参考。

芯耀

芯耀

957

957