2.1 卷积神经网络原理

卷积神经网络(Convolutional Neural Network,CNN)是一种前馈人工神经网络,相较于传统的人工神经网络,它具有极强的处理能力,可以直接处理三维图像中的大量像素数据,而且具有良好的算法扩展性和特征提取能力,因此在机器视觉领域得到了广泛的应用。如图2-1所示CNN包含的运算层通常由池化运算层、卷积运算层,全连接运算层和激活运算层组成的。

卷积神经网络概念结构图

(1)卷积层

卷积神经网络的核心部分之一是卷积层,它利用卷积核来完成大量注入数据,从而抽取出数据中的有用内容。卷积核能够看作是一个过滤器,其大小和形状能够参照结合应当需要进行调整。卷积操作是一种将图像中的像素值与输入图像中的每一位像素值进行相乘并求和的方法,这样就可以获得一种新的特征值,即卷积特征值。卷积层通过多个卷积核的组合提取不同的特征信息,同时卷积层还可以保持空间信息的局部连接性,使得其在处理图像时具有较好的鲁棒性。单个卷积层的运算公式如式(2-1)所示。

——特征图的点(x+i,y+j)下的像素值;

k——卷积核的尺寸;

W——输入特征图的宽;

H——输入特征图的高;

——卷积核对应的权重参数值;

b——卷积核对应的偏差参数值;

——激活函数;

——输入特征图中以(x,y)为中心点坐标,并且卷积窗口大小为k×k的二维卷积的卷积输出值。

(2)池化层

池化层也称为下采样层,通过降低特征图维度来降低特征图冗余度和网络计算复杂度,有效防止过拟合。 池化层的计算公式如式(2-2)所示。它主要用于降低卷积层的输出维度,减少计算量和内存占用,同时增强特征的不变性和泛化性。池化层通常包括最大池化和平均池化。最大池化是在一个固定尺寸的矩阵窗口内寻找最大的值作为输出值,而平均池化则是计算窗口内所有值的平均值作为输出值。通过多次卷积操作和池化操作,卷积神经网络能够逐层提取图像特征图,并且不改变其深度。

式中:

——第n层卷积层输出的第j个特征图;

——激活函数;

——池化层的池化方式,常用的有平均池化、最大池化、混合池化和随机池化。

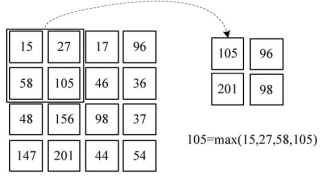

以最大池化方式为例,当池化步长为2时,最大池化的过程如图2-2所示。

最大池化层概念示意图

(3)全连接层

全连接层通常作为CNN中的最后一层,将卷积层和池化层提取的特征映射到输出的类别标签,是每个节点与上一层中的节点相互连接,组成一个全连接的神经网络层。全连接层通常采用softmax函数将最终的输出值映射到不同的标签上,从而实现分类任务。

除了以上三个基本组件外,卷积神经网络还包括其他一些重要的技术和概念,如批标准化、Dropout、损失函数、优化算法等。其中,批标准化可以使得神经网络的训练更加稳定和快速,Dropout可以防止神经网络过拟合,损失函数可以衡量神经网络的训练效果,优化算法可以通过梯度下降等方式对神经网络的参数进行更新和优化。

在卷积神经网络中,数据通常被表示为多维数组,如二维的图像数据、三维的音频数据等。对于图像数据,通常使用RGB三个通道来表示不同颜色的像素值,因此其维度为宽×高×通道数。而对于音频数据,通常使用频谱图或Mel频谱图来表示音频的特征,其维度为时间步数×频谱数。

卷积神经网络的训练通常需要大量的数据和计算资源。为了避免过拟合和提高泛化性能,常常使用数据增强和正则化等技术来扩充数据集和减小模型的复杂度。此外,还可以使用预训练模型和迁移学习等技术来加速训练和提高模型的准确性。

2.2 YOLOv5s目标检测网络模型

YOLOv5s网络结构图

YOLOv5(You Only Look Once version 5)是由Jocher在2020年提出的一种基于深度学习的目标检测网络,它可以用于对输入图像进行实时的目标检测和分类,在目标检测方面具有优异的性能和精度[80]。YOLOv5目标检测算法的原理是将输入图像分割成不同的网格,对每个网格预测其包含的物体类别和位置。对于YOLOv4、YOLOv5、YOLOv6、YOLOv7、YOLOv8的不同模型用PASCAL VOC数据集训练并进行参数量、运算量和精度的对比,如表2-1所示。

相比于YOLOv3和YOLOv4,YOLOv5的主要创新点在于引入了多种改进方法,包括更轻量级的网络架构、更高效的特征提取方法、更准确的边界框预测和更丰富的数据增强方法等,从而减少了总运算量,提高了检测准确率和速度;相比较对YOLOv6、YOLOv7和YOLOv8模型的大小和精度,YOLOv5系列的模型更加轻量,而其精度与其他模型仅有细微差距,使其更加适合在边缘计算硬件平台部署。

近年来,随着深度学习网络模型的发展,性能得到了极大的提高,同时其参数量和计算量也得到了极大的增加,这限制了其在资源受限的边缘计算设备中的嵌入。为了满足边缘移动端的武器硬件平台资源有限条件下对军用飞机目标检测的要求,则需要一种兼顾轻量化、平均精度和检测速度的军用目标检测算法,又因为YOLOv5n的参数量非常少,在硬件部署过程中经过量化会导致检测效果大幅下滑,故选取参数量较少而精度仅比YOLOv5m稍低的YOLOv5s作为基准算法。

YOLOv5s的网络结构采用了一阶式的目标检测模型设计,即在一个卷积神经网络中同时进行物体的定位和分类。这种结构相比于传统的两阶式目标检测模型(如Faster R-CNN)速度更快,但相对精度略低,也更适合部署在边缘计算设备中。YOLOv5s采用了一种全新的骨干网络结构,即C3模块,它可以在不影响网络深度和宽度的前提下,大大降低计算量和参数量。如图2-3所示,YOLOv5s的网络结构主要分为输入端、骨干网络、头部网络和检测层。

2.2.1 输入端

YOLOv5s网络模型在输入端部分主要进行了Mosaic数据增强、自适应锚框计算和自适应图像缩放,具体如下所示:

(1)Mosaic数据增强

为了改善待检测图像中的小目标分布不均匀和待检测目标所在环境恶劣导致模型在训练阶段的平均精度低的问题,在数据训练阶段,Mosaic数据增强方式将从训练集中随机选取的4张图片,然后以裁剪、排布和缩放等方式进行图片拼接,有效的丰富了输入端的训练数据集,通过以上操作来增强模型对小目标的检测性能,提高训练效率,适用于小目标检测。

(2)自适应锚框计算

YOLO算法中,针对不同数据集,计算预定义锚框。在网络训练中,以真实框位置相对于预设边框的偏移以进行拟合。网络在预定义锚框的基础上输出新锚点框位置信息,然后与真实框的位置进行比对,计算前后两个位置信息的差异,再反向更新迭代网络参数,使其能够更加精确的定位锚框的位置。

(3)自适应图像缩放

数据集中的图像存在长宽不相同的情况,在网络训练中,针对这种情况的做法通常是将原始图像的比例缩放到同一个尺寸,然后空余部分用灰白色进行填充,再送入网络中训练,即可以设置不同尺寸的图像作为输入图像。但如果缩放效果只是单纯的缩小,很有可能造成图片中的信息丢失。

2.2.2骨干网络

YOLOv5s网络模型主要采用CBS、C3和SPPF的模块结构。CBS模块是由YOLOv5网络提出的,其目的是为了防止下采样过程中的信息丢失。C3模块由三个卷积和一个CSP模块组成,CSP结构借鉴了CSP网络的思想,取消了残差输出后的卷积模块,其结构分为两支,分别为修正单元结构和基本卷积模块,最后将两个结构拼接并得到输出,其目的是通过局部的跨层融合获得更丰富的特征图,减少计算量;SPPF模块将步长固定为5,进行了三次最大池化,每次池化层的输出特征图会成为下一个池化层的输入特征图,从而减少操作数。对于CBS、C3和SPPF模块的具体细节如下所示:

(1)C3模块

C3模块由两个嵌套的残差模块组成。在不影响特征信息的情况下,简化了模型,减少了卷积模块的数量。根据应用位置的不同,C3模块可分为C3_1_X和C3_2_X。C3_1_X用在Backbone卷积神经网络部分,包含X个残差分量;X越大,网络结构越深。另一方面,C3_2_X应用于 Neck 并包含2X残差分量,其结构与C3_1_X的不同之处仅在于残差分量的数量。增加Resunit的个数可以增加不同层间反向传播的梯度值,防止网络结构更深导致的梯度退化问题。而且,增强了模型提取和融合网络特征的能力。因此,随着网络学习能力的提高,计算量和参数要求的降低,C3模块也提高了网络的目标检测精度。

(2)CBS模块

CBS模块是由卷积层、数据归一化层和激活函数层组成的复合卷积模块,是很多模块的重要组成部分。数据归一化层主要是对数据进行归一化,促进快速收敛,加速网络。激活函数层使用SiLU作为新的激活函数,本质上是对激活函数sigmoid的加权线性组合。SiLU函数是连续且平滑的。在更深的模型上,它可以增加模型的非线性并提高检测精度,它比原始激活函数LeakyRelu表现更好。它们的表达式如下:

(3)SPPF模块

如图2-4所示,SPPF和SPP的模块都是由三个最大池化层和连接层构成。首先使用CBS模块将特征图中的通道数减半,然后通过最大池化层对其进行下采样,最大池化层使用串联的三个大小为5×5的最大池化而不是并行的三个最大池化在SPP模块中进一步融合图像特征,之后将三个最大池化层的输出结果与图片的初始特征图进行叠加,将其局部特征与全局特征进行特征融合,以较小的代价将通道数变为原来的2倍,不仅提高了感受野,还可以解决多目标尺度的问题,即在一定程度上缩放和融合目标图像特征图。此外,SPPF模块还可以将任意维度的特征图转化为固定维度的特征向量,以此提高感受野。

2.3.3 头部网络

YOLOv5s网络模型的头部网络主要借鉴了PAN网络的思想,引入了特征金字塔网络(Feature Pyramid Network,FPN)与路径聚合网络(Path Aggregation Network,PAN)的结构。FPN是一种特征金字塔网络结构,它形式上是自上而下且向上采样,融合了多种尺度的特征图,因为网络的上层比较深,包含的语义信息比较多,这使得底层特征图的语义信息更加丰富。PAN是一种特征金字塔网络结构,它形式上是自下而上向下采样,也融合了多个尺度的特征图,因为下层的卷积层较少,能够获得更多的特征定位信息。FPN和PAN结构通过融合对方处理过的特征图而相互补充,使输出的特征图具有很强的语义特征和很强的定位特征,同时输出多尺度预测图。

2.3.4 检测层

YOLOv5s网络模型的检测层采用CIoU_Loss的回归损失函数和非极大值抑制(Non-Maximum Suppression,NMS)进行预测以提高模型检测性能。回归损失函数是一种深度学习中非常重要的评估模型训练效果的工具,它可以帮助我们将模型快速达到收敛状态,减少预测误差。损失函数越小,说明建模的学习效果越好,可以更有效地提高目标检测算法网络建模的准确度和可信度。近年来,回归损失函数被研究者重视,并做了很多研究相继提出了如IoU_Loss、DIoU_Loss、CIoU_Loss、SIoU_Loss等损失函数。其中IoU_Loss损失函数的缺点是对图像尺度不够灵敏,且只能得到真实边界框和预测边界框之间的交叠区域面积;DIoU_Loss损失函数把边界框的中心距离信息引入损失函数中;CIoU_Loss损失函数则是在DIOU的研究上,引入了边界框的尺度。SIoU_Loss损失函数在CIoU损失函数的研究上,引入了真实边界框和预测边界框之间的向量角度,重新定义了惩罚指标,提高了网络训练速度和网络推理准确度。在选择最优预测边界框时,采用NMS方法可以去除多余的预测边界框,当预测边界框和实际边界框的重合度高于设定的阙值时,可以认为它是同一类物体,并将最高值所在的预测边界框最终选择框。

2.4 基于FPGA的动态重构技术

基于FPGA的动态重构技术是一种能够根据实时应用需求重新配置硬件逻辑的技术。通过使用这种技术设计的动态重构硬件系统可以在运行时改变其硬件电路结构和性能,以适应不同的应用场景和任务,从而提高应用程序的效率和可靠性。又因为FPGA具备优异的可重编程能力来实现硬件逻辑的重构,故通常使用FPGA作为硬件部署平台。动态重构技术已经应用在很多技术领域,例如网络处理、高性能计算、数字信号处理、信息加密、图像和视频处理等。由于动态重构技术可以根据实时应用需求重新配置硬件逻辑,因此它可以提高系统的效率和灵活性,同时减少开发和维护成本,因而得到研究者们广泛的关注。

基于FPGA的动态重构系统在硬件逻辑层面可分为完全重构和部分重构。完全动态重构通过FPGA重新配置其所有硬件资源以改变其功能。部分动态重构(Dynamic Partial Reconfiguration,DPR)将整个FPGA的逻辑区域分为静态逻辑区域和动态逻辑区域,静态逻辑区域就是在FPGA中电路结构固定不变的区域,动态逻辑区域即部分可重构分区,它是FPGA中电路结构可以通过加载和卸载不同硬件配置文件而发生改变的区域。在实际硬件部署中,DPR允许通过加载动态配置文件来修改运行中的FPGA应用,当完整的硬件配置文件配置到FPGA后,通过板上系统加载配置文件的方式来修改FPGA的动态重构区域,而不会扰乱和破坏未动态重构配置的逻辑区域上正在运行中的工程应用。

部分动态重构示意图

动态部分重构结构示意图如图2-5所示,图中将FPGA区域分为两个可重构区域A和B,每个可重构区域中分配了足够的资源空间,通过空间复用的方式映射到A1,A2的可重构模块,在系统运行的过程中可以动态的从比特流库中配置所需要的可重构模块比特流配置文件,通过这种动态组合硬件系统的方式构建不同的硬件架构,而不需要让系统中断,即可完成不同的硬件计算任务,还能有效的解决了FPGA硬件资源受限的问题。

2.5 ZYNQ软硬协同开发

2.5.1 ZYNQ UltraScale+MPSoC平台

ZYNQ UltraScale+MPSoC是一款由XILINX公司开发的高度集成的多处理器片上系统。它所承载的ZYNQ MPSoC系列芯片采用基于FPGA和ARM处理器的异构架构,拥有可编程性强、低功耗、高性能等特点。该芯片的架构包括ARM Cortex-A53处理器、ARM Cortex-R5处理器和FPGA逻辑,这些模块可以实现高性能计算、实时控制、硬件加速、接口协议转换、数字信号处理等应用。其PS端的主控制处理器核心采用了ARM Cortex-A53和Cortex-R5架构,能够运行Linux等操作系统和FreeRTOS等实时操作系统。其中Cortex-A53处理器适用于应用程序处理和控制,而Cortex-R5处理器则适用于实时任务和硬实时控制。两个处理器能够协同工作,提供卓越的性能和实时性。此外,芯片的FPGA逻辑非常灵活,支持多种不同的应用扩展接口。如多个高速串行接口、千兆以太网接口、USB接口和PCIe接口等,可以满足各种高速通信和数据传输需求。以XILINX KV260 FPGA的边缘嵌入式计算平台为例,ZYNQ UltraScale+MPSoC系统架构框图,如图2-6所示。

2.5.2 高层次综合设计

高层次综合(High-level Synthesis,HLS)是一种自动将用高级语言描述的逻辑结构转换为低抽象级别语言描述的电路模型的过程。HLS通常使用高级语言,如C、C++和SystemC,这些语言具有更高的抽象性和可操作性,常常没有时钟或时序的概念,同时HLS已经被融入到Vitis统一软件平台中,能够通过在Vitis HLS开发设计平台上调用Vitis的视觉库,加速硬件设计的流程。而低层设计语言如Verilog、VHDL和SystemVerilog则通常用于描述时钟周期精确的寄存器传输级电路模型,这是目前用于ASIC或FPGA设计的最常见的电路建模和描述方法,但是其开发效率低,设计的复杂度高。

在近几十年中,特别是在FPGA领域,HLS已经引起了很多关注并得到了快速发展。近年来,FPGA学术大会上,HLS已作为学界和产业界最热点的课题,受到了关注和深入研究。其原因主要有以下几点:

(1) 采用更高级别的抽象技术来构建集成电路是当今芯片设计发展的必要步骤。RTL逻辑抽象技术无法满足当今芯片设计的要求,会给产品设计、测试和集成化提供巨大的挑战。相比之下,采用更高级的语言,如C和C++,能够将编码密度缩小7至10倍,进而大大简化工程设计,大大提高设计效率。

(2) 对于FPGA,现代FPGA具有大量成熟的固定功能和资源量的IP软核,可以被Vitis HLS开发设计工具充分利用。这将简化综合算法,提高综合电路的性能,同时增加IP重用的效率。

(3) HLS可以为软件系统和计算工程人员提供一种全新的方式来设计芯片和FPGA,它可以将硬件实现细节包装起来,使得软件系统和工程人员可以更加注重于上层计算的实施,从而更好地发挥芯片和FPGA的潜力。这意味着,不需要具备底层硬件设计知识的工程师也可以参与到FPGA的设计中来。

2.5.3 深度学习处理单元

深度学习处理单元(Deep Learning Processor Unit,DPU)是一种专门为深度学习任务设计的运算IP核,能够高效地执行深度学习算法[95]。DPU的硬件架构如图2-7所示,DPU从片外存储器中取指令来控制计算引擎的运算,这些指令由Vitis AI开发工具中的AI编译器生成[96]。AI编译器将模型映射到高效的指令集,并执行复杂的优化,如层融合、指令调度,并尽可能地重用片上系统级芯片上的存储器资源;存储器用于缓冲输入、中间和输出的数据,以实现高吞吐量和效率;计算引擎采用的是深度流水线设计;处理单元(PE)充分利用了Xilinx器件中的精细颗粒度构建块,如乘法器、加法器和累加器。

DPU IP核可以配置与卷积单元的并行性相关的各种卷积架构。DPU IP 的架构包括B512、B800、B1024、B1152、B1600、B2304、B3136和B4096。B是DPU大小的符号,后面数字的大小代表计算并行度,等于每个周期的峰值运算数。同时,每个周期的峰值操作数等于 DPU 卷积架构中并行度的三个维度的乘积:像素并行度、输入通道并行度和输出通道并行度。并行度越高,消耗的FPGA资源就越多。同时,如果资源充足,FPGA最多可以支持部署三个核心DPU。

DPU架构

芯耀

芯耀

2601

2601

下载ECAD模型

下载ECAD模型