一、前言

如今注重可持续发展和节能环保的社会背景下,超低功耗MCU(Microcontroller Unit)作为一种领先的技术,被广泛应用于生活中的节能要求。随着无线手持终端和物联网的发展,无线终端、智能电话、智能手表、物联网模块、智能水表电子产品都宣称比以往先进。手持消费类产品和物联网设备要求产品有丰富的功能、卓越的性能、小型化,在电池电量有限的情况下还要保持长续航;静态与动态功率需求是电源管理的关键,同时也是设计人员面临的挑战。

现在低功耗芯片的应用场景越来越广,很多工程师朋友在产品开发过程中遇到不少问题,那怕最后问题解决了,也是知其然而不知其所以然。下面带大家来了解低功耗芯片的工作和设计原理,通过讲解芯片设计中应用了哪些技术来揭开它的神秘面纱。

二、芯片功耗原理分析

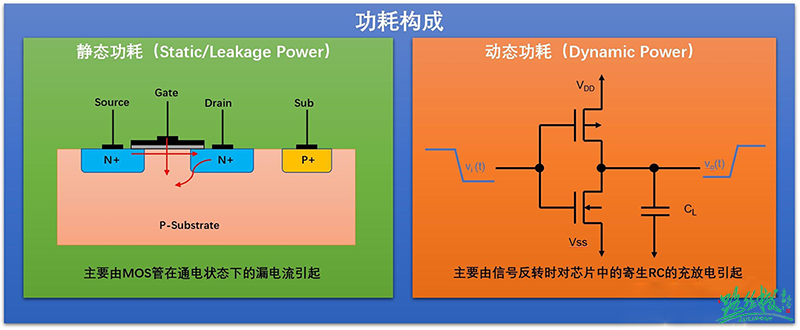

芯片的功耗主要由动态功耗与静态功耗两部分组成,动态功耗是指信号发生改变时所消耗的功耗,静态功耗信号没有改变时所消耗的功耗。功耗本质上就是电学术语中的功率,不同于一般简单的电学器件,芯片的整体功耗很难通过简单的电流,电压或者电阻值的的相乘来计算。

其原因在于芯片作为具有复杂功能的器件,其功耗会根据其不同时段的不同行为和不同的外部条件而发生很大的变化。在实际设计中一般会选取一些特定的条件,并辅以特定的功能设定来计算芯片的功耗。

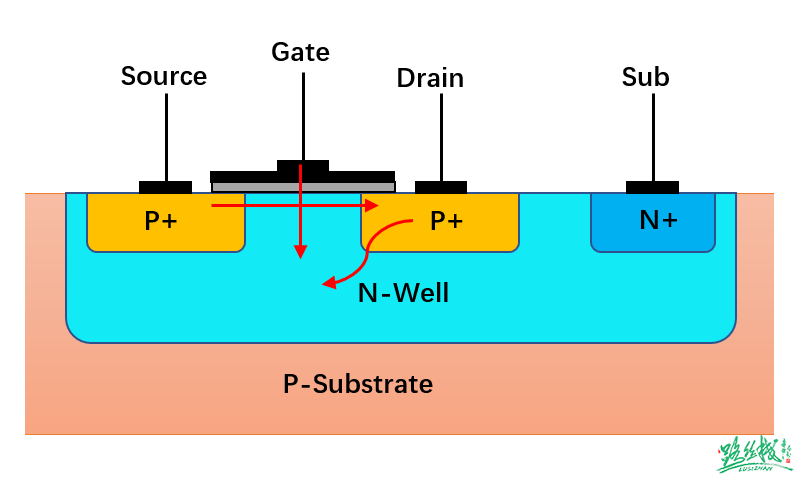

1. 静态功耗(Static Power),又称漏电流功耗(Leakage Power)。其原理请参见下图:

PMOS Leak 电流示意图

上图中红色箭头表明了在通电状态下PMOS内主要的泄露电流及其走向,意即:

泄漏电流(Leakage Current)= 漏极->N-Well + Gate->N-Well + 源极->漏极

泄露电流形成原因在MOS管中的多种掺杂区形成导电区域,同时这些区域会组成多个PN节,从而在通电后形成一系列微小的电流。

尽管在现今芯片的工作电压已经很低的前提下,每个MOS管的漏电流很小,但由于每颗芯片中集成的晶体管至多几亿甚至几十亿,积少成多,导致芯片的整体leakage power变得越来越恐怖。

后端设计中每个标准单元(standard cell)的leakage都集成在其liberty库文件(.lib)中,因此计算leakage power只需在制定条件下将design中所有的标准单元(包括各种Macro)的leakage值相加即可。目前所有的主流PR工具对此都有支持。需要指出的是,由于一个标准单元的leakage power和其面积成正比,因此在实际后端设计的各个阶段,尤其是low power设计中,一般会重点关注芯片中逻辑门的面积变化并以此快速推断design的leakage功耗变化。

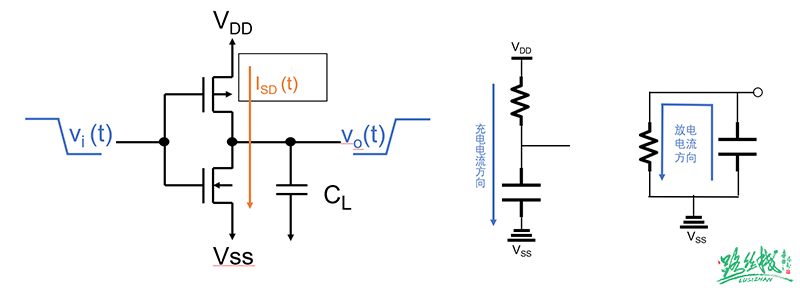

2. 动态功耗(Dynamic Power),主要包含翻转功耗与短路功耗两个部分,翻转功耗是指电平翻转对负载电容进行充放电时消耗的功耗;短路功耗是指PMOS和NMOS存同时导通时构成通路,形成短路电流。

翻转功耗(Switching Power)是由充放电电容引起的动态功耗,当芯片中的电路出现任何信号翻转都会产生dynamic power,其中所占最大比例的就是clock信号的翻转。下图展示了一个反相器(inverter)在信号翻转时的简单模型:

Inverter Dynamic Power Consumption

当我们把反相器简化成一个简单的rc电路时,就可以清晰的看清充放电时的电流走向。当芯片处于工作状态时,每一个工作中的标准单元都会随着clock or/and data的翻转而不断重复上述过程,从而产生大量的动态功耗。

短路功耗(Internal Power)又可以称为内部功耗 ,主要原因是直接通路电流引起的功耗,即短路造成的。

短路功耗是因为在输入信号进行翻转时,信号的翻转不可能瞬时完成。因此PMOS和NMOS不可能总是一个截止另外一个导通,总有那么一段时间是使PMOS和NMOS同时导通;电源VDD到地VSS之间就有了通路,就形成了短路电流。

三、芯片功耗计算方法

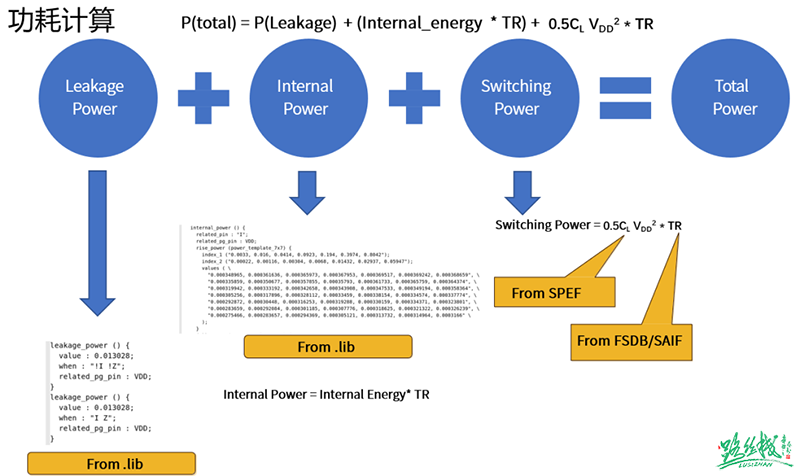

数字芯片CMOS电路中功耗分为静态功耗和动态功耗,动态功耗是由内部功耗和开关功耗组成的;其中动态功耗的分析依赖于前端VCS功能仿真提供的包含Switching Activity信息的FSDB波形文件或者SAIF文件。

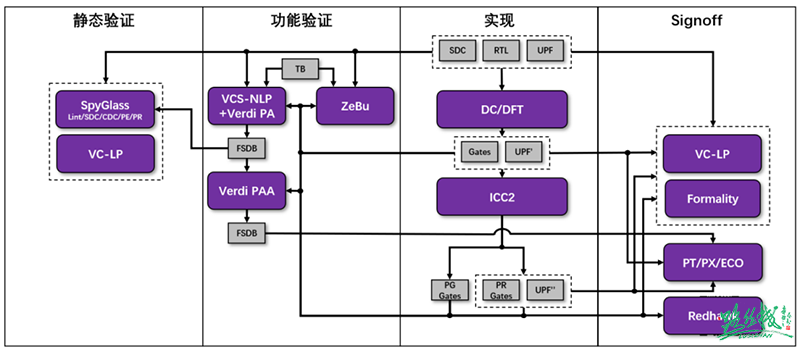

低功耗方法学是一项非常重要的学习内容,在数字芯片设计中可以利用UPF对power domain进行系统性的管理,从而提高芯片的能效比。

带UPF的低功耗设计流程中包括了前端 VCS-NLP 功能仿真和后端 VC LP 静态验证,在DC综合和ICC2布局布线中插入标准低功耗单元,每个标准单元(standard cell)的leakage都集成在其liberty库文件(.lib)中。Signoff阶段的Formality逻辑等价性检查以及PTPX功耗分析等。

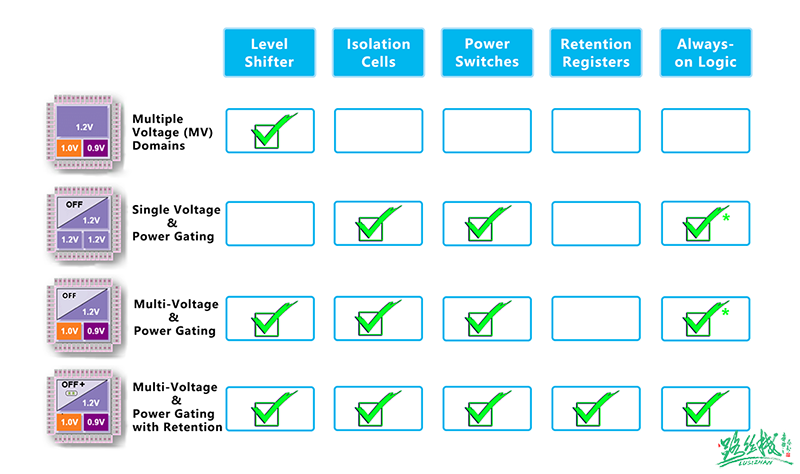

电源控制cell基本就五种类型:Level Shifter,Isolation Cell,Power Switches(MTCMOS),Retention Registers和Always-on Logic。其中AO包含buffer和inverter,一种取反一种不取反(新工艺库都包含这两种)。各种类型的低功耗技术所需的cell如下图所示:

1. 静态功耗(leakage power)只需在制定条件下将design中所有的标准单元(包括各种Macro)的leakage值相加即可。需要指出的是,由于一个标准单元的leakage power和其面积成正比,因此在实际后端设计的各个阶段,尤其是low power设计中,一般会重点关注芯片中逻辑门的面积变化并以此快速推断design的leakage功耗变化。

2. 动态功耗(Dynamic Power)由于和芯片的功能息息相关,因此在计算的时候会引入翻转率(toggle rate)的概念。翻转率是衡量单位时间内device上信号翻转时间所占的比率。在实际计算dynamic功耗的时候,又会分成两个部分。一部分为标准单元内部的dynamic功耗,又名Internal Power,这部分的计算是嵌入liberty库文件内部,通过标准单元的input transition和output load来查表得到的;另一部分为互连线(net)上的dynamic功耗,这部分的计算通过将所有net上每个翻转周期的功耗乘以其翻转率并相加得到。反转率通过某种固定格式的文件传入EDA工具,比较常用的格式有SAIF(Switching Activity Interchange Format)、VCD(Value Change Dump)以及FSDB(Fast Signal Database)文件。

四、低功耗芯片常用技术

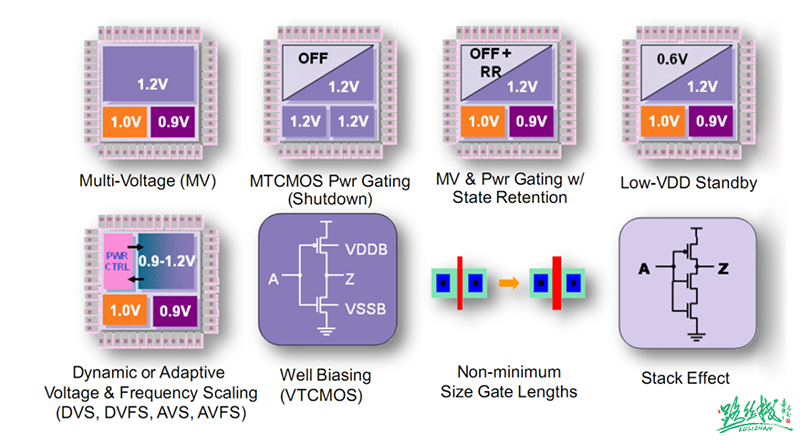

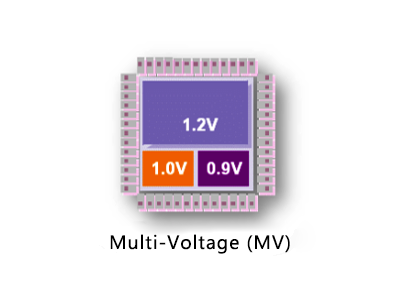

1. 多电压域(Multi-Voltage )

多电压域设计思想就是让SOC内的每个模块/IP根据自己的需要,工作在不同电压域,这样可以减少所有模块共电压域造成的功耗浪费。

信号在不同电压域间进行传输时,可能会存在驱动不足或者过驱动的问题。当一个低电压域的信号去驱动高电压域的cell时,欠驱动力的信号不仅增加了输入端的上升时间和下降时间,增加短路电流的持续时间,还会使时序变差;为了解决这个问题,需要在不同电压域之间添加level-shifter(电平转换器),它可以实现将某个电压域的输出电平转换成另一个电压域可以识别的逻辑电平。

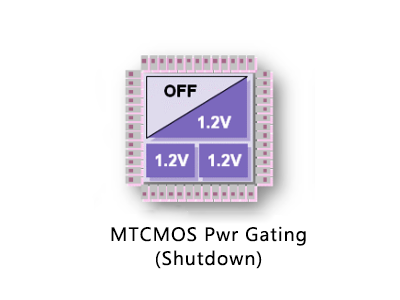

2. 电源门控(MTCOMS Power Gating)

随着工艺技术的发展,由漏电流所产生的功耗所占的总功耗比例越来越大;希望移动设备中的SoC芯片在休眠模式下尽量节省功耗的设计来说,最好的办法是将处于休眠模式状态的模块的供电电源,关断而保持其它模块的正常供电,这种技术叫电源门控技术。

电源门控一般有两种方法:

内部电源门控(on-chip power gating);内部电源门控是指在芯片内部用一些专门的逻辑单元如电源门控单元来控制所选模块的供电情况。

外部电源门控(external power gating);实现电源门控最基本的方法,适于消耗漏电功耗较少但关断时间较长的设计。例如一个SoC系统在板极上有CPU的专用电源,这个电源只提供电压给CPU;外部电源门控技术就是,可以关闭这个电源以使CPU在非活动状态时漏电功耗减小到零。

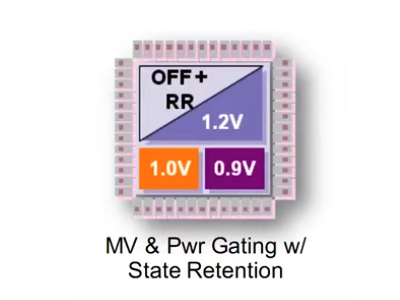

3. 多电压+功耗控制+寄存器Retention技术

多电压域与电源门控的混和应用加在上寄存数据能够提高系统的响应时间。

芯片系统中的各个模块都可以工作在不同的电压下,同时某些模块的供电电源还可以切断,并且在电源切断的情况下还要保持掉电之前的状态;因此这就需要引入Retention寄存器,当掉电后的模块再次上电后,至少经过一个时钟周期,之前掉电的模块就可以恢复到掉电之前的正常状态。

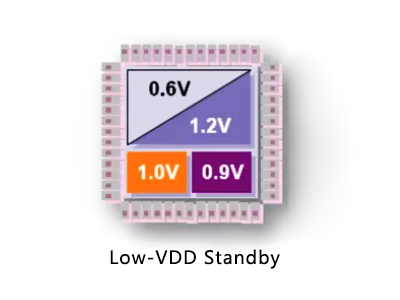

4. 低电压standby(Low-VDD Standby)

在低功耗芯片内核中有一个电压域的供电电压值VDD为0.6V,并且使用该供电电压VDD为0.6V的模块一直都处于Always-On状态。

在某种情况下芯片中的其他模块需要进入sleep状态,这时候可以使用较低的电压来保持芯片可以工作,同时在0.6V电压域中放置一个小的控制单元(假如为一个小的CPU);一旦当系统需要全速工作,这时候我们可以用0.6V电压域中的小的控制单元去唤醒其他模块。

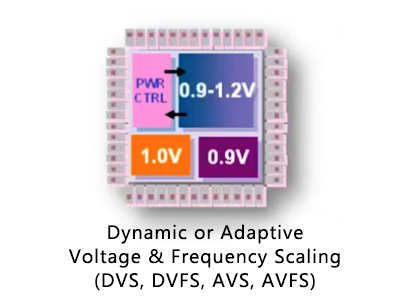

5. 动态电压频率调节(DVFS,DVS,AVS,AVFS)

自适应的电压频率调节技术,根据系统中电压和工作频率之间的关系,可以有效的降低系统功耗。实现最优化性能和功耗之间的平衡,但需要考虑电压和频率变化对时序和稳定性的影响问题。更多详细内容请看《芯片动态电压频率技术原理》。

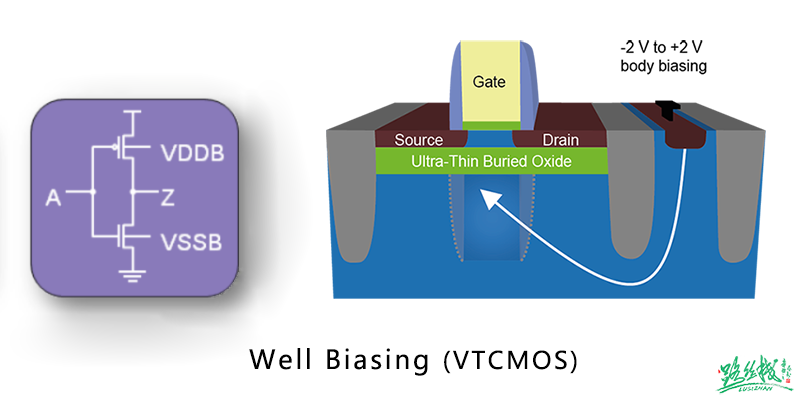

6. 多阈值工艺(Well Biasing)

多阈值电压设计的策略是:对于性能要求高的模块,或者频率比较高的部分,采用阈值电压比较低的cell,以减少单元门的延迟;对于性能要求较低的模块,或者频率较低的部分,多采用阈值电压比较高的cell,让功耗更低。通过这种方法,可以实现在同一块芯片上,根据性能和功耗的不同要求而调整cell的使用,从而避免在不太重要的功能上浪费过多的功耗。

工艺中存在着不同的cell类型,cell 类型的速度、电压和漏电可以用下表表示:低阈值的标准逻辑单元:速度快、漏电流大;高阈值的标准逻辑单元:速度慢、漏电流小。

通过改变器件背栅的电压,体偏置技术可以动态地控制器件的门限电压。过去通过复杂的掺杂技术来控制的门限电压参数,现在可以通过软件来编程从而实现动态的控制。设计者可以利用这种功能来动态地管理产品的漏电状况,有效地补偿制程和环境温度等效应造成的影响。

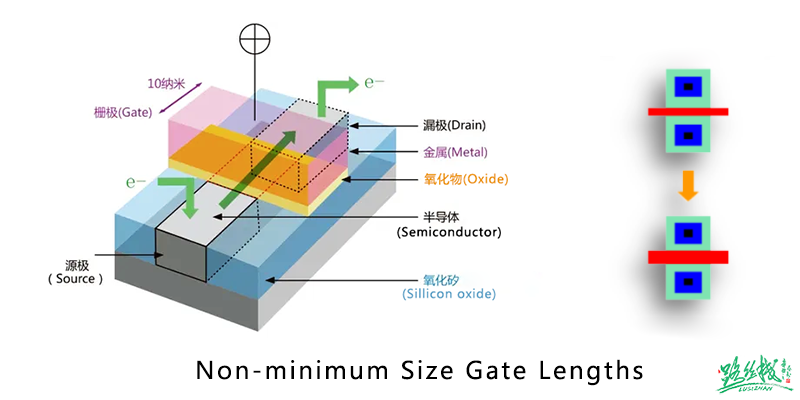

7. 栅极(Gate)

MOSFET结构有三个极,分别是源极(Source),漏极(Drain),栅极(Gate),可以理解成电流从源极进去,从漏极出来,而栅极相当于水龙头的作用,加电压就形成导通,没有电压就关断(这是常关型MOS特性,如果是常通型MOS则是加负电压关断)。形成导通和关断就能代表0和1,这就是计算机的基础工作原理,对,0和1,二进制,德国数学家莱布尼茨发明的,其还发明了微积分。

栅极的开关速度和开启/关断的阈值电压,决定了晶体管工作的频率,速度,栅极大小和功耗密切相关,栅极越小,沟道就越小,但是沟道越小就更容易漏电,因此得到更高频率更好性能的芯片,带来的副作用就是面临更大损耗,同时发热量也越大。

栅极厚度,大小,结构和材料,很大程度上决定了晶体管的极限工作状态下的开关速度,频率以及功耗大小,换栅极材料就能继续提高晶体管的性能和控制功耗。

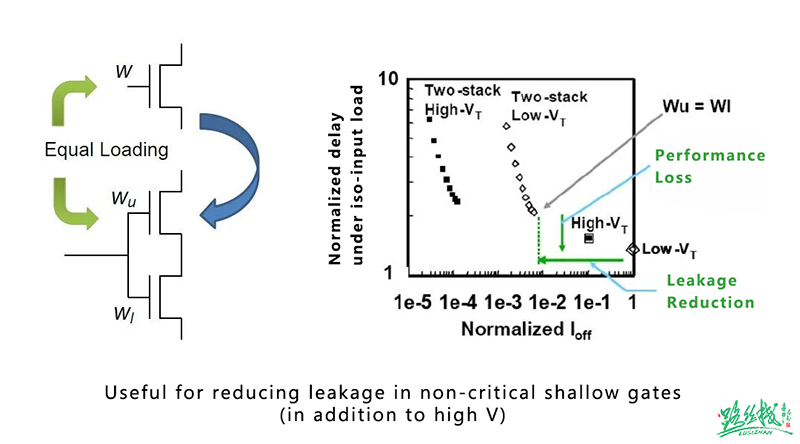

8. 叠加效应(Stack Effect)

叠加效应可以将一个MOS管强制拆分成2个堆叠的MOS管,2个串联的MOS管有相同的输入。

效果:从图中可以看到,在采用Two-stack的MOS管之后,在休眠状态下,Low-Vt的管子leakage power至少降低了2个数量级(从1降低到1e-2以下),而High-Vt的管子leakage power至少降低了3个数量级(从1e-1降低到1e-4以下)。

注意:其实这是在leakage power与速度之间的折衷,最好将这种技术应用到那些有timing slack的单元上,对于timing critial path不能使用。

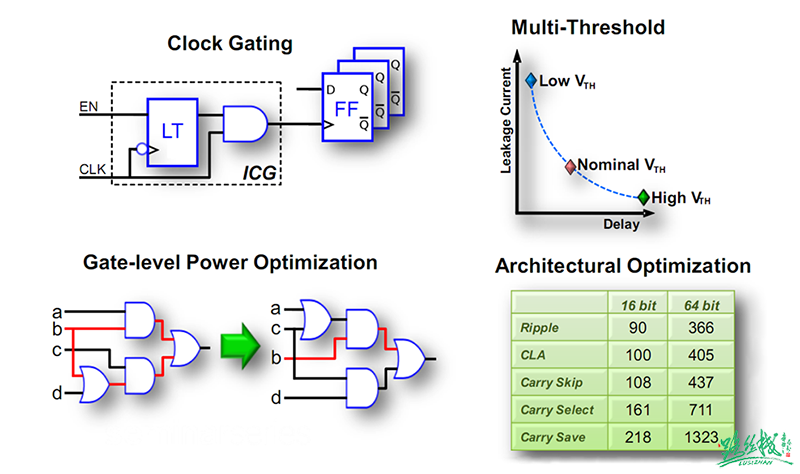

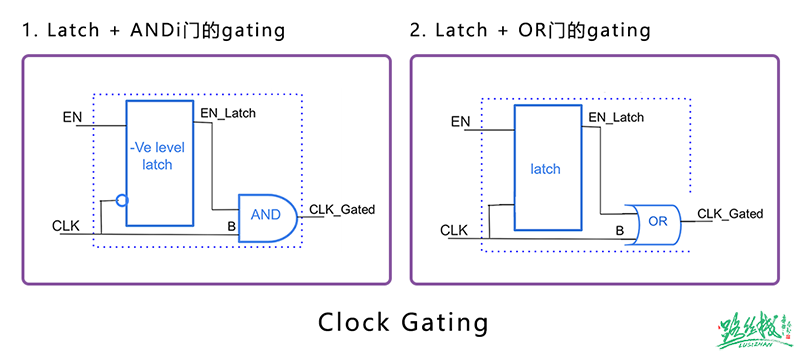

9. 门控时钟(Clock Gating)

芯片中翻转率最高的路径就是clock path,clk path上的功耗消耗会占据到整个芯片功耗比例的40%甚至更多。clock经pll 和预分频器输出后,后面会驱动成千上万寄存器,并且为了增加clock的驱动能力,在clock path上会插入许多buffer,而clock 每个cycle翻转就会带动整条path上所有cell 翻转。如果当某一个subsys 或者module 不工作时clock仍在toggle,那么就会产生很大的功耗浪费。

如果能够根据系统或者任务的需要对clock 做动态的关断就能极大地节省功耗消耗,这种对clock 进行关断的技术就是clock gating(时钟门控)。如上图,clock gating 技术主要就是在原来的clock path上加入enable 信号,使 clock 在满足一定条件后才能往后传输。这种方法可以减少信号翻转和短路电流,但需要考虑时钟网络的设计、时钟分布的平衡和时钟毛刺的消除问题。

五、结语

UPF(Unified Power Format)用来描述芯片设计中的低功耗意图,包括芯片工作的“电特性”、工作电压、电压的开关、低功耗cell插入的策略和芯片的power state等。低功耗设计流程中加入UPF可以保证功耗意图在IC设计中的一致性,使低功耗意图在仿真验证、逻辑综合、物理实现、等价性验证和最终签核更容易实现。

1. 芯片的功能及时序设计与优化已相对成熟,但功耗上的优化还有很多空间可做。

2. 功耗会影响电路性能、芯片散热、芯片可靠性的问题;电池容量的增加相对有限,而且受到安全因素的限制。

3. 降低功耗方法还能提高工艺,使用新型低功耗器件和材料;减少晶体管尺寸,如从40nm、28nm到14nm、7nm等。用先进工艺要做好性能和成本的平衡,详细请看《芯片设计、流片、验证、成本的那些事!》

芯耀

芯耀

5045

5045

下载ECAD模型

下载ECAD模型

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)