Arm Neoverse S3 是 Arm 专门面向基础设施的第三代系统 IP,应用范围涵盖高性能计算 (HPC)、机器学习 (ML)、边缘和显示处理单元,是新一代基础设施系统级芯片 (SoC) 的理想技术根基。Neoverse S3 设计实现了芯粒 (Chiplet) 与机密计算 (Confidential Compute) 等关键创新,为合作伙伴提供了支持 UCIe、DDR5、CXL 3.1 和 PCIe Gen5/Gen6 等行业标准的现成功能。Neoverse S3 提供了一整套系统 IP,能够实现高度可组合性、更高的 IO 吞吐量和增强的安全特性。其主要特性包括:

- 支持设备分配机密计算的 Arm 机密领域管理扩展 (Realm Management Extension, RME) 功能,并且符合行业标准 DPE,进行“使用中”的数据保护。

- 支持 PCIe Gen6、CXL 3.1、DDR5 和 HBM3 的 IO 与内存系统。

- 通过基于 UCIe 的 AMBA CHI C2C 的标准化芯粒接口,搭配定制的芯粒开发工具包,可与 Arm CPU 配合使用。

实现机密计算

安全性是涉及各类 IP 的 SoC 系统级问题。多年来,加密技术广泛应用于数据的安全存储和传输,也就是用来保护“静态”或“传输中”的数据。目前基于硬件的安全性改进着重于保护“使用中”的内存数据。“机密计算”是一个表示加密内存中数据的行业术语。Armv9 架构使用硬件技术 RME 来为 Arm 机密计算架构 (CCA) 提供支持。Neoverse S3 率先支持 RME,使得 Arm Neoverse V3 核心能够支持完全加密的云虚拟机。

通过 PCIe 和 CXL 挂载的网卡或加速器等 IO 外设设备会引入一些潜在的安全威胁。Neoverse S3 系统 IP 可确保外部连接的设备在不影响应用的性能的同时,仅能访问授权的内存。这是通过“设备分配”技术而实现的,该技术允许外设通过直接内存访问 (DMA) 将数据传输到加密内存中。除了安全优势之外,该技术还让连接设备可以绕过庞杂的软件层直接共享数据,大大增强 I/O 性能。

这种将高效通用计算与高性能加速器结合起来的能力,是新推出的 Arm Neoverse 计算子系统 (CSS) —— Neoverse CSS V3 和 Neoverse CSS N3 的核心。CSS 产品旨在帮助 Arm 合作伙伴通过前所未有的方式,以更低的成本,更迅速、高效地向市场提供针对工作负载优化的定制芯片。Microsoft Azure Cobalt 100 便是基于 Neoverse CSS 的软硬件共同开发的成果。这些 CSS 产品展示了基于 Arm Neoverse 解决方案的未来,与 Arm 相关的整个行业和生态系统正致力于打造成本更低、复用性更强的基于 Arm 架构的芯粒。如果没有 Neoverse S3 系统 IP 这个“无名英雄”打下的基础,这一切都将无法实现。

为行业标准和芯粒提供支持

PCIe Gen5/Gen6、CXL 3.1、UCIe 和 DDR5 等行业标准是基础设施级 SoC 的关键。但正确实现这些标准并非易事。为支持这些标准,Arm Neoverse S3 完成了许多复杂的工作,并与请求方和物理层 (PHY) 等关键第三方 IP 进行了互操作性测试。Neoverse 为我们的合作伙伴提供了符合这些行业标准的现成功能,使其能够更专注于打造差异化、定制化的产品。

先进工艺的成本不断飙升,但并不是所有的芯片设计都能一样地进行扩展。换言之,只有特定的系统组件(例如 CPU 核心)可以有效地利用工艺进步的成果。芯粒技术能够将 SoC 分解到系统级封装 (SoaP) 中,以便更经济地采用不同工艺节点来构建系统。SoaP 支持以模块化方式打造解决方案,从而将芯粒开发的成本分摊到不同解决方案中。

不过,这种模块化设计不能增加架构和软件设计的复杂性。Arm Neoverse 解决方案下的芯粒采用标准化接口并带有预定义芯粒配置,这样 Arm Neoverse 生态系统中的每个芯粒供应商都能够构建兼容 Neoverse CSS 的芯粒。这些芯粒标准包括:

- AMBA CHI C2C 涵盖了 SoaP 不同子系统通信的应用层和链路层协议。

- Arm 芯粒系统架构 (Arm Chiplet System Architecture) 涵盖了定义地址转换、中断处理、系统管理和安全的架构合规性标准。

- Arm 基础系统架构 (Arm Base System Architecture) 涵盖了对软件提供标准支持的硬件需求。

为了进一步推广 AMBA CHI C2C 和芯粒的普及,Arm 提供了基于 Neoverse S3 设计的芯粒设计套件。该设计套件为 IO 一致性和完全一致性加速,或分解式芯粒奠定了基础。

Neoverse CSS 和定制芯片的基础

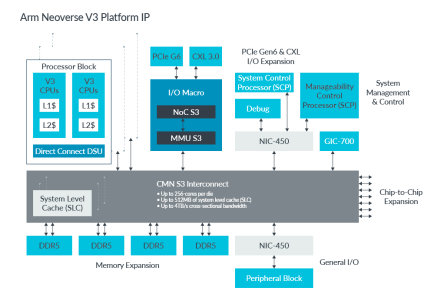

图:Arm Neoverse 系统中 Neoverse S3 设计示意图,其中包括 CMN S3、MMU S3 和 NOC S3

Neoverse S3 系统 IP 由 Neoverse CMN S3、Neoverse MMU S3 和 Neoverse NOC S3 所组成,这三者共同构成了一个成熟可靠的强大平台,帮助合作伙伴构建其 SoC。

CMN S3 建立在 CMN-700 IP 基础之上,为性能更高、数据需求量更大的 Neoverse 核心提供一致性的支持。CMN S3 专为全新的芯粒技术而构建,支持机密计算,同时提高了性能和可扩展性,而这恰巧是实现互连的关键所在。

CMN S3 能够安全且高性能(高带宽、低延迟)地连接核心和加速器芯粒,这对于开发高能效、高性价并针对工作负载优化的 SoC 至关重要。领先的云服务提供商都利用数据处理单元 (DPU) 从主机 CPU 卸载安全、存储和网络功能。它们还会部署和开发 GPU、NPU 和 TPU,以加速现代云软件中的人工智能 (AI) 和 ML 功能。与此同时,电信提供商也在 5G RAN 和边缘基础设施中部署包括 CPU 和加速器的异构 SoC。

内存管理单元 MMU S3 建立在行业标准化的 MMU-700 IP 基础之上,可为片上、芯粒和插入式卡提供高性能,机密计算支持,并支持 PCIeG6 与 CXL3.1的 IO MMU 功能。

片上网络 NOC S3 是基于 NI-700 构建的新型非一致性互连技术,专为 IO 一致性加速器芯粒而打造,能够帮助合作伙伴如之前基于片上 AMBA 的设计一样,轻松简便地构建高性能的分解式 SoC。

Neoverse S3 是我们的第三代 Neoverse 系统 IP,同时也是 Neoverse CSS V3 和 Neoverse CSS N3 的基础,可以为构建从云服务到边缘 DPU 的高水平基础设施 SoC 提供所需的基本功能,该平台不仅符合关键的行业标准,并且成为了行业标杆。Neoverse S3 将提供现成的机密计算和芯粒功能,助力合作伙伴实现新一代创新的定制芯片。

1339

1339

下载ECAD模型

下载ECAD模型