引言:从本文开始,我们陆续介绍下有关7系列FPGA通用PCB设计指导,重点介绍在PCB和接口级别做出设计决策的策略。由于FPGA本身也属于数字集成电路,文章中的大部分设计策略及概念也可为其他数字IC电路设计提供参考。文章内容主要包括以下五个章节内容:

PCB技术基础:讨论当前PCB技术的基础,重点是物理结构和常见假设。

配电系统(PDS):涵盖7系列FPGA的配电系统,包括去耦电容选择、稳压器和PCB几何结构的使用、仿真和测量的所有细节。

SelectIO信号设计:包含SelectIO™ 标准、I/O拓扑图和端接策略以及有关仿真和测量技术的信息。

PCB材料和走线:为获得最佳性能的高频应用,提供一些关于管理信号衰减的设计策略。

高速信号传输设计:阐述了传输线的高速设计。

所提供的分析和实例可以大大加快具体设计的速度。

本文我们介绍第一部分内容,即PCB技术基础。

印刷电路板(PCB)是电气系统,其电气特性与安装在其上的分立元件和器件一样复杂。PCB设计者需要对PCB的许多方面都有完全的控制权;然而,当前的技术对其几何结构和由此产生的电性能施加了限制和限制,本小结介绍以下内容:

- PCB结构

- 输电线路

- 回流

1. PCB结构

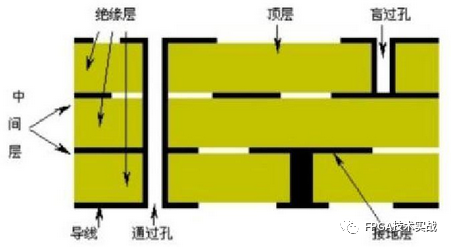

PCB技术在过去几十年中没有发生显著变化。两面镀铜的绝缘体基材(通常是FR4,环氧树脂/玻璃复合材料)的一部分铜被腐蚀掉,形成导电路径。电镀和蚀刻基板的层与蚀刻基板之间的额外绝缘体基板粘合在一起。在层叠上钻孔,将导电镀层应用于这些过孔,在不同层的蚀刻铜之间选择性拓扑成导电连接。

图1、PCB构成

虽然PCB技术有了进步,但PCB的基本结构没有改变,例如材料特性、使用的层叠层数、几何结构和钻孔技术(允许孔只穿透堆叠的一部分)。通过PCB技术形成的结构被抽象为一组物理/电气结构:走线、平面(或电源层)、通孔和焊盘。

1.1 走线

走线是一种物理金属条(通常是铜),在PCB的X-Y坐标上的两个或多个点之间进行电气连接。走线承载了两点之间信号的传输。

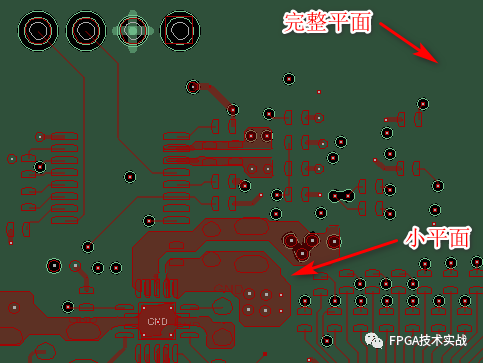

1.2 平面(Planes)

平面是覆盖整个PCB层的不间断金属区域。小平面,一个平面的变体,是一个不间断的金属区域,只覆盖PCB层的一部分。通常,一个PCB层中存在多个小平面。平面和小平面将能量分配给PCB上的许多点。它们在走线传输信号时非常重要,因为它们是信号回流传输介质。图1显示了完整平面(GND)和小平面(局部铺铜)。

图1、Planes举例

1.3 过孔

过孔是一块金属,在PCB的Z轴空间中的两个或多个点之间进行电气连接。过孔在PCB层之间传输信号或电源。在当前的平板穿透孔(PTH)技术中,通孔是通过在PCB上钻孔的内表面电镀而成的。在目前的微孔技术(Microvias,也称为高密度互连或HDI)中,通孔是用激光烧蚀基底材料并使导电镀层变形而形成的。这些微孔不能穿透超过一层或两层,但是,它们可以堆叠或阶梯式形成贯穿整个板厚的通孔。

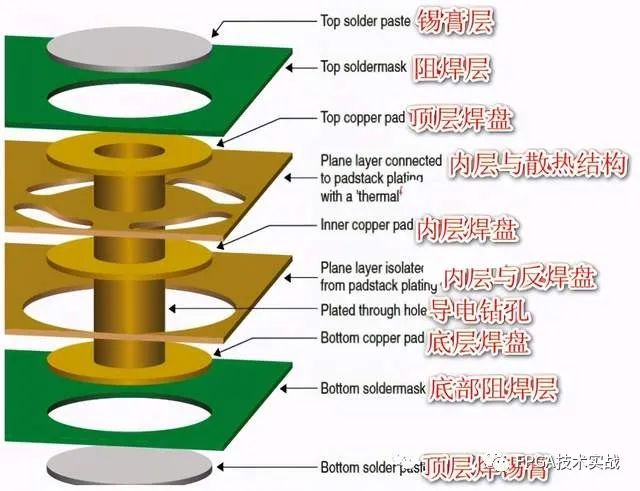

1.4焊盘和反焊盘

因为PTH过孔在过孔的整个长度上都是导电的,所以需要一种方法来选择性地对PCB的各个层的迹线、平面和小平面进行电连接。这是焊盘和反焊盘的作用。

焊盘是规定形状的小面积铜。反焊盘是规定形状的小区域,在那里铜被去除。焊盘既可与通孔一起使用,也可用作安装表面贴装元件的裸露外层铜。反焊盘主要与过孔一起使用。

图3、焊盘结构

对于走线,焊盘用于在通孔和给定层上的走线或平面形状之间进行电气连接。要使通孔与PCB层上的走线形成牢固连接,必须有一个焊盘以保证机械稳定性。焊盘的尺寸必须符合钻孔公差/定位限制。

反焊盘在平面(Planes)层使用。因在为平面和小平面铜是不间断的,所以任何穿过铜的通孔都会与铜形成电气连接。在那里过孔并不是用来与通过的平面或小平面进行电气连接的,反焊盘会去除过孔穿透的层区域中的铜。

1.5 Lands

为了焊接表面贴装元件,外层上的焊盘通常称为焊环(图3中锡膏层)。与这些焊盘进行电气连接通常需要通孔。由于PTH技术的制造限制,很少采用可以在Lands区域内放置通孔。取而代之的是,使用一小段连接到表面焊盘的走线。连接走线的最小长度由PCB制造商的最小尺寸规格确定。微孔技术不受限制,过孔可以直接放置在焊盘。为了有关PCB焊盘和BGA封装的更多信息,请参阅7系列FPGA封装和引脚产品规范用户指南(UG475)附录“BGA封装的推荐PCB设计规则”。

1.6 尺寸

定义PCB尺寸的主要因素是PCB制造限制、FPGA封装几何形状和系统符合性。其他因素,如面向制造的设计(DFM)和可靠性施加了进一步的限制,但由于这些是特定于应用程序的,因此本用户指南中没有记录这些因素。

FPGA封装的尺寸与PCB制造限制相结合,直接和间接地定义了本节中描述的PCB结构(PCB结构)的大部分几何方面。这大大限制了PCB设计者。封装球间距(FF封装为1.0 mm)定义了焊盘布局。当前PCB技术的最小表面特征尺寸定义了器件下区域的通孔排列。最小通孔直径和这些通孔周围的隔离区域由PCB制造商定义,这些直径限制了通孔之间的可用空间量与最大走线宽度。PCB制造限制限制了最小走线宽度和最小间距。

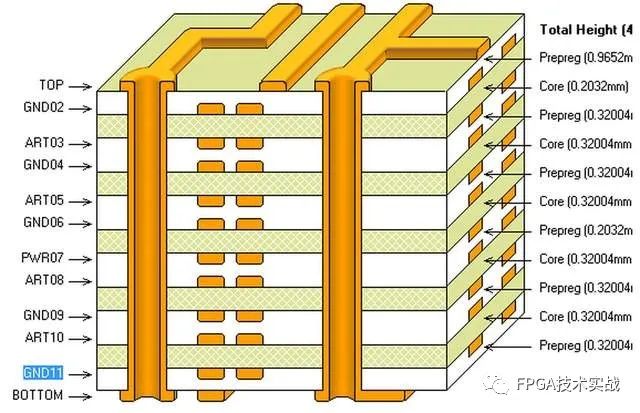

图4、12层PCB层叠设计案例

容纳FPGA所需的PCB层的总数由信号层的数量和平面层的数量定义,大多数用于大型FPGA的PCB从12层到22层不等。

信号层的数量由进出FPGA封装的I/O信号通道的数量定义(通常与封装中的总用户I/O数有关)。

平面层的数量由向FPGA供电并为信号层提供参考和隔离所需的电源和地平面层的数量来定义。

系统总体要求通常定义了电路板的总厚度,因此,随着电路板层数的增加,信号层与平面层(参考层)、以及信号层与信号之间的层间距会变得越来越小,这会引入信号层间的串扰以及影响信号阻抗以及电源系统寄生电感等。

信号走线到参考平面层的Z方向间距(由电路板总厚度和电路板层数定义)是走线中的一个决定性因素,走线宽度(由FPGA封装球间距和PCB通过制造限制定义)是控制阻抗的另一个因素。设计者通常很少控制FPGA下的过孔阵列区域的走线阻抗。当走线穿出BGA阵列时,其宽度可以改变为目标阻抗的宽度(通常为50Ω单端)。

去耦电容器布局和分立终端电阻布局是其他领域的权衡优化。DFM约束通常在FPGA(器件封装)周围定义一个隔离区域,在该区域中不能放置分立的组件。禁区的目的是为装配和返工留出空间必要的。为了因此,在“禁止入内”区域之外的区域是一个组件放置位置的区域。由PCB设计师决定高优先级组件。去偶电容器布置约束在第2部分“配电系统”中进行了描述。

2 传输线

信号走线和参考平面的组合形成传输线。PCB系统中的所有I/O信号都通过传输线传输。

对于单端I/O接口,信号走线和参考平面都是将信号从PCB上的一个位置传输到另一个位置所必需的。对于差分I/O接口,传输线由两根走线和一个参考面组成。虽然在差分信号的情况下,参考面的存在并不是严格必要的,但对于pcb中差分走线的实际实现却是必要的。

在PCB系统中,良好的信号完整性依赖于具有阻抗受控的传输线。阻抗由走线的几何形状和信号走线周围以及信号走线与参考面之间的填充材料的介电常数决定。

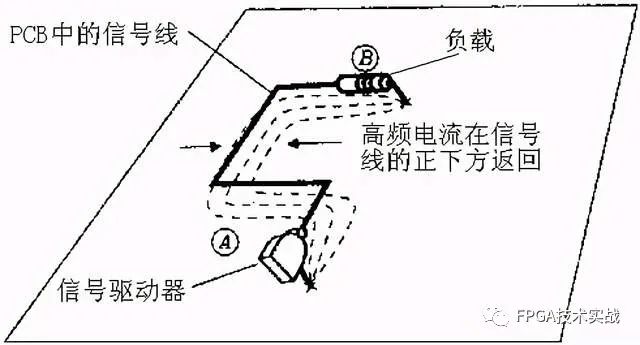

3 回流

传输线及其信号完整性的一个经常被忽视的方面是回流。假设一条信号线本身形成一条传输线是不正确的。在信号走线中流动的电流在其下方的参考平面中具有相等和相反的互补电流。走线电压和走线电流与参考面电压和参考面电流的关系定义了由走线和参考面形成的传输线的特性阻抗。虽然走线下参考平面连续性的中断效果不如切断信号走线那么显著,但传输线和共享参考平面的任何设备的性能都会受到影响。

图5、信号回流路径

重要的是要注意参考平面的连续性和回流路径。打断参考平面的连续性,如孔、槽或隔离缝隙,在信号传输中引起显著的阻抗不连续性。它们也可能是串扰的重要来源,并导致配电系统(PDS)噪声。回流路径的重要性不可小觑。

芯耀

芯耀

1508

1508

下载ECAD模型

下载ECAD模型