今天给大侠带来基于FPGA的 UART 控制器设计(VHDL)(中),由于篇幅较长,分三篇。今天带来第二篇,中篇,RS-232 串口通信简介。话不多说,上货。

导读

串口的出现是在1980年前后,数据传输率是115kbps~230kbps。串口出现的初期是为了实现连接计算机外设的目的,初期串口一般用来连接鼠标和外置Modem以及老式摄像头和写字板等设备。串口也可以应用于两台计算机(或设备)之间的互联及数据传输。由于串口(COM)不支持热插拔及传输速率较低,部分新主板和大部分便携电脑已开始取消该接口。串口多用于工控和测量设备以及部分通信设备中。

串口是串行接口的简称,也称串行通信接口或串行通讯接口(通常指COM接口),是采用串行通信方式的扩展接口。串行接口(Serial Interface)是指数据一位一位地顺序传送。其特点是通信线路简单,只要一对传输线就可以实现双向通信(可以直接利用电话线作为传输线),从而大大降低了成本,特别适用于远距离通信,但传送速度较慢。

通信协议是指通信双方的一种约定。约定包括对数据格式、同步方式、传送速度、传送步骤、检纠错方式以及控制字符定义等问题做出统一规定,通信双方必须共同遵守。串口通信的两种最基本的方式为:同步串行通信方式和异步串行通信方式。

同步串行通信是指SPI(Serial Peripheral interface)的缩写,顾名思义就是串行外围设备接口。SPI是一种高速的全双工通信总线。封装芯片上总共有四根线,PCB布局布线也简单,所以现在很多芯片集成了这个协议。主要用于CPU和各种外围器件进行通信,TRM450是SPI接口。

异步串行通信是指UART(Universal Asynchronous Receiver/Transmitter),通用异步接收/发送。UART是一个并行输入成为串行输出的芯片,通常集成在主板上。UART包含TTL电平的串口和RS232电平的串口。RS232也称标准串口,也是最常用的一种串行通讯接口。RS-232-C 标准对两个方面作了规定,即信号电平标准和控制信号线的定义。RS-232-C 采用负逻辑规定逻辑电平,信号电平与通常的TTL电平也不兼容,RS-232-C 将-5V~-15V 规定为“1”,+5V~+15V 规定为“0”。

一般情况下外设不能直接和主机直接相连,它们之间的信息交换主要存在以下问题:

- 速度不匹配 通常情况下外设的工作速度会比主机慢许多,而且外设之间的速度差异也比较大。

- 数据格式不匹配 不同的外设在进行信息存储和处理时的数据单元可能不同,例如最基本的数据格式可以分为并行数据和串行数据。

- 信息类型不匹配 不同的外设可能采用不同类型的信号,有些是模拟信号,有些是数字信号,因此所采用的处理方式也不同。

为了解决外设和主机之间信息交换的问题,就需要设计一个信息交换的中间环节——接口。本篇将首先对接口技术进行简要的介绍,然后以接口中最常用的 UART 控制器为例,详细介绍用 FPGA 实现 UART 控制器的方法。

第二篇内容摘要:本篇介绍RS-232 串口通信简介 ,包括串口通信概述协议 、RS-232 通信时序和 UART以及串口通信实现方案等相关内容。

二、RS-232 串口通信简介

2.1 串口通信概述

在数据通信、计算机网络以及分布式工业控制系统中,经常采用串行通信来交换数据和信息。1969 年,美国电子工业协会(EIA)将 RS-232C(简称 RS-232)定为串行通信接口的电气标准,该标准定义了数据终端设备(DTE)和数据通信设备(DCE)间按位串行传输的接口信息,合理安排了接口的电气信号和机械要求,适合于数据传输速率在 0~20000bit/s 范围内的通信。RS-232 作为一种标准接口,不仅被内置于每一台计算机中,同时也被内置于各种外设中。

RS-232 具有以下几个优点:

- 使用广泛,几乎每一台 PC 都会有一个或者多个 RS-232 接口;

- 连接距离可达到 15m;

- 实现简单,RS-232 用于双向连接,只需要 3 条导线。

除了 RS-232 标准,美国电子工业协会(EIA)还制定了 RS-422 与 RS-485 标准。RS-422由 RS-232 发展而来,它是为弥补 RS-232 之不足而提出的。RS-422 定义了一种平衡通信接口,将传输速率提高到 10Mbit/s,传输距离延长到 4000 英尺(速率低于 100kbit/s 时),并允许在一条平衡总线上连接最多 10 个接收器。

RS-422 是一种单机发送、多机接收的单向、平衡传输规范,被命名为 TIA/EIA-422-A 标准。为扩展应用范围,EIA 又于 1983 年在 RS-422 基础上制定了 RS-485 标准,增加了多点、双向通信能力,即允许多个发送器连接到同一条总线上,同时增加了发送器的驱动能力和冲突保护特性,扩展了总线共模范围,命名为 TIA/EIA-485-A标准。

由于 EIA 提出的建议标准都是以“RS”作为前缀,所以在通信工业领域,仍然习惯将上述标准以 RS 作前缀称谓。RS-232、RS-422 与 RS-485 的电气参数如表 2 所示。

表 2 RS-232、RS-422 与 RS-485 的电气参数表

虽然 RS-232、RS-422 与 RS-485 标准对接口的电气特性做出了规定,但是没有规定连接插件、电缆或协议,所以在此基础上用户可以建立自己的高层通信协议。RS-232 等协议在视频传输中被广泛应用,许多厂家都建立了一套高层通信协议,或公开或厂家独家使用。如录像机商家中的 Sony 与松下对录像机的 RS-422 控制协议是有差异的,视频服务器上的控制协议则更多了,如 Louth、Odetis 协议是公开的,而 ProLINK 则是基于 Profile 上的。

目前,RS-232 是 PC 机与通信工业中应用最广泛的一种串行接口,本篇后两篇就详细介绍一下 RS-232 协议的内容和使用 FPGA 开发 RS-232 接口的方法。

2.2 RS-232 协议

标准的 RS-232 接口有 25 根信号线,其中有 4 根数据线、11 根控制线、3 根定时线和 7根备用线。通常情况下,使用 25 根信号线中的 9 根就可以实现 RS-232 通信。

1)DSR 信号线

DSR(Data Set Ready)意思为数据装置就绪,当其状态为有效时,表明 Modem 处于可以使用的状态。

注意:Modem 是 Modulator/DEModulator 的缩写,中文名称是调制解调器。Modem 是一种在发送端通过调制将数字信号转换为模拟信号,而在接收端通过解调再将模拟信号转换为数字信号的设备。

2)DTR 信号线

DTR(Data Terminal Ready)意思为数据终端就绪,当其状态为有效时,表明数据终端可以使用。

3)RTS 信号线

RTS(Request To Send)意思为请求发送,即当终端需要发送数据时,使该信号有效,向Modem 请求发送。它用于控制 Modem 是否进入发送状态。

4)CTS 信号线

CTS(Clear To Send)意思为允许发送,这个信号是对 RTS 信号的响应。当 Modem 已经准备好接收终端发送过来的数据时,使该信号有效,通知终端开始发送数据。

5)DCD 信号线

DCD(Data Carrier Detection)意思为数据载波检出,当此信号为有效时表示 Modem 已经接通了通信链路,即本地 Modem 收到了通信链路另一端的远程 Modem 送来的载波信号,终端可以准备接收数据。

6)RI 信号线

RI(Ringing)意思为振铃指示,当本地 Modem 收到交换台发送的振铃呼叫信号时,使该信号有效,通知终端已被呼叫。

7)TxD 信号线

TxD(Transmitted Data)意思是发送数据,终端通过此信号线将数据发送给 Modem。

8)RxD 信号线

RxD(Received Data)意思是接收数据,终端通过此信号线从 Modem 接收数据。

9)地线

地线有两根,分别是信号地 SG(Signal Ground)和保护地 PE(Protection Ground),信号地是所有信号的参考电平,保护地用于连接设备外壳或者地表。

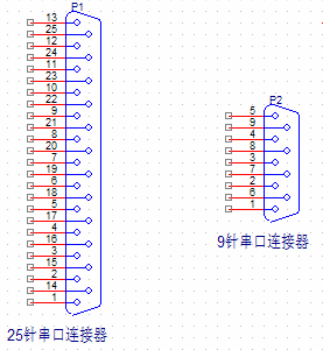

常见的 RS-232 串行口连接器主要有两种,一种是 25 针的 DB-25,另一种是 9 针的 DB-9,其示意图如图 1 所示。

图 1 RS-232 串行口连接器示意图

其中 DB-9 主要用于上述的 9 根信号线连接的方法,DB-25 可以连接所有 RS-232 标准定义的信号线。DB-25 也可用像 DB-9 那样使用,但是它们的针号与信号之间的线连接关系是不一样的,如表 3 所示。

表 3 DB-25、DB-9 针号信号线连接对应表

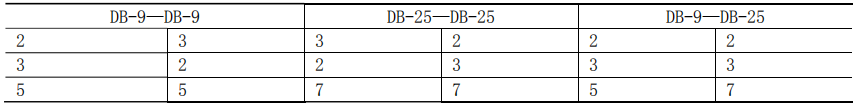

最为简单且常用的 RS-232 连接方法是三线连接法,即地、接收数据和发送数据三脚相连。对于上述的 DB-25 连接器和 DB-9 连接器,三线连接法的原则如表 4 所示。

表 4 DB-25、DB-9 三线连接法

在电气特性方面,标准 RS-232 接口有如下规定:

- 对于数据传输线 RxD 和 TxD,逻辑“1”对应的电平是-15V~-3V,逻辑“0”对应的电平是+3V~+15V。

- 对于 RTS、CTS、DSR、DTR、DCD 等信号线,信号有效时对应信号线上为正电压+3V~+15V,反之则是负电压-15V~-3V。

由于 RS-232 电气特定规定的电平不符合通常电路中所使用的 TTL 或者 CMOS 电平,所以在接入电路之前需要对其进行转换。RS-232 串口电平的转换一般是使用专门的芯片实现的,其中为最常用的就是美信(MAXIM)公司的 MAX232。

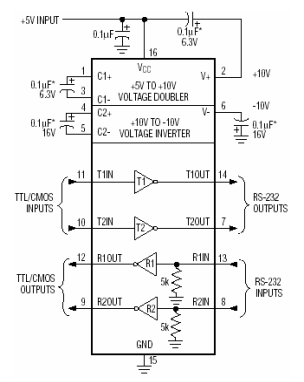

MAX232 可以将串口设备需要发送的 TTL/CMOS逻辑电平转换为 RS-232 逻辑电平,同时也可以将要接收的 RS-232 逻辑电平转换为 TTL/CMOS电平,图 2 所示就是 MAX232 芯片的顶层图。MAX232 可提供 DIP/SO/TSSOP 3 种封装,可以满足不同的设计需求。

图 2 MAX232 芯片的顶层图

MAX232 的典型连接方法如图 3 所示,其中有 5 个 0.1μ 的去耦电容;11 管脚和 10 管脚是 TTL/CMOS 电平输入,对应 14 管脚和 7 管脚的 RS-232 电平输出,它们一般接到 RS-232 的RxD 上;12 管脚和 9 管脚是 TTL/CMOS 电平输出,对应 13 管脚和 8 管脚的 RS-232 电平输入,它们一般接到 RS-232 的 TxD 上。

图 3 MAX232 典型连接示意图

2.3 RS-232 通信时序和 UART

在串行通信中,用“波特率”来描述数据的传输速率。所谓波特率,即每秒钟传送的二进制位数,其单位为 bit/s(bits per second),它是衡量传输串行数据速度快慢的重要指标。有时也用“位周期”来表示传输速率,位周期是波特率的倒数。国际上规定了一个标准波特率系列:110bit/s、300bit/s、600bit/s、1200bit/s、1800bit/s、2400bit/s、4800bit/s、9600bit/s、14.4kbit/s、19.2kbit/s、28.8kbit/s、33.6kbit/s、56kbit/s。如 9600bit/s,其意义是每秒传送 9600 位数据,包含字符位和其他必须的位,如奇偶校验位、起始位、停止位。

大多数串行接口电路的接收波特率和发送波特率都可以设置,但接收方的接收波特率必须与发送方的发送波特率相同。通信线上所传输的字符数据(代码)是逐位传送的,1 个字符由若干位组成,因此每秒钟所传输的字符数(字符速率)和波特率是两种概念。在串行通信中所说的传输速率是指波特率,而不是指字符速率,假如在异步串行通信中,传送一个字符,包括12 位(其中有一个起始位,8 个数据位,2 个停止位),其传输速率是 1200bit/s,每秒所能传送的字符数是 1200/(1+8+1+2)=100 个。

在串行通信中,除了可以设置波特率外,其他的如字符数据的位数、奇偶校验位、停止位也可以被设置。其中,字符数据的位数可以被设置为 5~8 位;奇偶校验位可以去除,也可以设置为奇校验或者偶校验;停止位可以设置为 1 位、1.5 位或者 2 位。

下面介绍一下串行通信的时序。串行总线在空闲时候保持逻辑“1”状态(即串行连接线上的电平为-3V~-15V),当需要传送一个字符时,首先会发送一个逻辑为“0”的起始位,表示开始发送数据;之后,就逐个发送数据位、奇偶校验位和停止位(逻辑为“1”)。例如,通过RS-232 串行通信发送一个字符“1”(二进制为 01100001),设置为 8 位数据位,1 位奇偶校验位,1 位停止位,则发送时序图如图 4 所示。

图 4 RS-232 串行口通信时序图

对于一个设备的处理器来说,要接收和发送串行通信的数据,还需要一个器件将串行的数据转换为并行数据以便于处理器进行处理,这个器件就是 UART。UART(Universal AsynchronousReceiver/Transmitter)全称是通用异步收发器,其功能是辅助处理器与串行设备之间的通信。

作为 RS-232 通信接口的一个重要部分,UART 具有以下功能:

- 将由计算机内部传送过来的并行数据转换为用于输出的串行数据流;

- 将计算机外部传递来的串行数据转换为字节,供计算机内部使用并行数据的器件使用;• 在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验;

- 在输出数据流中加入启停标记,并从接收数据流中删除启停标记;

- 提供和处理器之间的通信信号,可以处理处理器和串行通信设备之间的同步管理问题。

随着处理器功能越来越强,目前大部分处理器中都集成了 UART,用户的工作仅仅是根据需要对其进行配置即可。

2.4 串口通信实现方案

实现串口通信主要需要完成两部分工作:

(1)将串口电平转换为设备电路板的工作电平,即实现 RS-232 电平和 TTL/CMOS 电平的转换;

(2)接收并且校验串行的数据,将数据变成并行的并提供给处理器处理。

前面已经介绍了实现 RS-232 电平和 TTL/CMOS 电平转换可以用接口芯片实现,实现数据的串行到并行转化用的是 UART,它们是实现串行通信必不可少的两个部分。虽然目前大部分处理器芯片中都集成了 UART,但是一般 FPGA 芯片却没有这个特点,所以使用 FPGA 作为处理器可以有两个选择,第一个选择是使用 UART 芯片进行串并转换,第二个选择是在 FPGA 内部实现 UART 功能。

使用 UART 芯片进行串并转换的优点是设计简单,但是却会使设计的成本增加并且增加电路板的面积。选择在 FPGA 片上实现 UART 能够节省成本,但是会占用一部分 FPGA的资源,如果有一定富余的 FPGA 资源,这是一个不错的选择。本篇下面的内容将详细介绍使用 FPGA 实现 UART 的思路和步骤。

本篇到此结束,下一篇带来基于FPGA的 UART 控制器设计(VHDL)(下),使用 FPGA 实现 UART,包括UART 实现原理、UART 工作流程、信号监测器模块的实现、波特率发生器模块的实现、移位寄存器模块的实现、奇偶校验器模块的实现、总线选择器模块的实现、计数器模块的实现、UART 内核模块的实现、UART 顶层模块的实现 、测试平台的编写和仿真等相关内容。

芯耀

芯耀

1688

1688

下载ECAD模型

下载ECAD模型