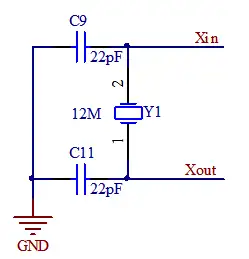

一般来说,单片机的时钟电路是使用外部的无源晶振和负载电容组合实现连接到单片机的Xin和Xout引脚上,无源晶振自身无法振荡,因此需要匹配外部谐振电路才可以输出振动信号。

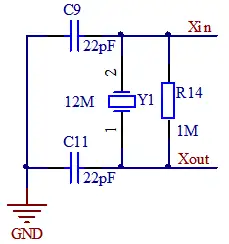

但是在实际电路设计中,也会在晶振两端并联一个电阻。这个电阻叫做反馈电阻。

那么并联的这个反馈电阻有什么作用呢?

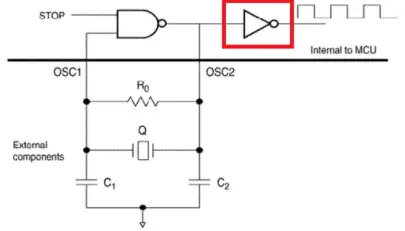

首先来看下时钟电路的基本原理。一般来说,时钟电路又称作皮尔斯振荡器电路,因为它电路简单,工作有效而稳定,优于其它型态的石英晶体振荡电路。皮尔斯振荡器所需零件很少: 一个反相器、一个电阻、一个石英晶体、两个小电容。

在晶振电路中,并联电阻是一个重要的元件,它与石英晶体谐振器并联连接。并联电阻的作用主要有以下几点:

- 频率调节

并联电阻可以调节晶振电路的频率。当并联电阻的值发生变化时,会影响电路的阻抗,从而改变石英晶体谐振器的振动频率。通过调整并联电阻的值,可以对晶振电路的频率进行微调,使其精确地稳定在所需的频率上。

- 改善电路性能

并联电阻可以改善晶振电路的性能。在晶振电路中,由于石英晶体谐振器的Q值较高,电路的阻抗会受到频率、温度等因素的影响。并联电阻可以提供额外的阻抗,以抵消这些因素的影响,从而改善电路的性能。

- 增加电路稳定性

并联电阻可以提高晶振电路的稳定性。当电路受到外界干扰时,并联电阻可以抑制干扰信号对电路的影响,从而减小频率偏差和相位噪声。这有助于提高晶振电路的稳定性和精度。

- 保护石英晶体谐振器

并联电阻可以保护石英晶体谐振器免受电流冲击。在晶振电路启动或关闭时,可能会产生较大的瞬态电流,这些电流可能会对石英晶体谐振器造成损坏。并联电阻可以限制电流的大小,从而保护石英晶体谐振器免受损坏。

并联电阻的选择

在选择并联电阻时,需要考虑以下几个因素:

- 阻值范围:根据电路设计和频率调整的需要,选择合适的阻值范围。

- 稳定性:选择稳定性好的电阻,以确保其阻值不会随温度、时间等因素变化。

- 功率容量:选择功率容量足够的电阻,以承受可能的瞬态电流和电压。

- 温度系数:选择温度系数小的电阻,以减小温度对阻值的影响。

总之,并联电阻在晶振电路中起着重要的作用,它可以调节频率、改善电路性能、增加稳定性以及保护石英晶体谐振器。在设计和选择并联电阻时,需要考虑电路的需求和环境因素,以确保晶振电路的稳定性和精度。

晶发电子是一家专业石英晶体谐振器、晶体振荡器以及从事晶体配套设备研发、生产、销售的高新技术企业。晶发JF产品涉及直插晶体谐振器、贴片石英谐振器、陶瓷谐振器、无源晶振、SMD晶体谐振、蓝牙天线等。

芯耀

芯耀

1765

1765

下载ECAD模型

下载ECAD模型