作者:Adam Taylor,贸泽电子专稿

现场可编程门阵列(FPGA)是实现图像处理系统的绝佳选择。它具有高度并行的逻辑架构,可实现高分辨率、高帧率的图像处理算法,因而非常适合用于从自动驾驶到机器人等诸多应用。通常,图像处理解决方案是在异构片上系统(SoC)中实现的,这样的系统能够结合可编程逻辑与Arm®硬处理器内核。然而,在某些应用中,这些处理器并不能得到充分利用,上电后也只能进行进行初步的IP核配置。在这种情况下,使用传统FPGA搭配IP核配置状态机或使用软处理器内核会是更好的选择。

本项目中,我们将使用AMD AC701评估板,在AMD Artix™ 7 FPGA上创建图像处理管道。该电路板将使用FMC互连来连接MIPI摄像头,并通过HDMI显示输出视频。

本项目的材料清单包括以下内容:

- Vivado™ 2022.1

- Vitis™ 2022.1(分步安装教程:《How to Install Vitis》)

- Matlab和Simulink – R2021b

基本硬件设计

首先,我们要建立一个能够实现标准图像透传的系统,其间需要在FPGA中正确配置摄像头和IP模块,以便接收图像并通过HDMI传输到处理链。这些设备的用途非常广泛,因而可以配置为所需的输出格式。Pcam 5C摄像头模块和HDMI芯片均通过相同的I²C链路进行配置。

为了配置摄像头、HDMI芯片和内部IP核,我们需要实现AMD MicroBlaze™软处理器内核。

以下是透传功能所需的IP块:

- MicroBlaze,配置为同时提供指令AXI接口和数据AXI接口

- MicroBlaze调试模块

- AMD AXI中断控制器,连接至MicroBlaze中断端口

- AXI IIC,与外部I²C总线连接,用于摄像头和HDMI配置,并与AXI中断控制器连接,以实现中断驱动方法

- AMD MIPI CSI2 RX子系统,配置为接收来自摄像头的MIPI数据流

- AMD LogiCORE™ IP传感器去马赛克内核,可将摄像头捕获的原始图像转换为RGB像素表示形式

- 视频帧缓冲写入,将图像帧存储到DDR3内存中

- 视频帧缓冲读取,从DDR3内存中读出图像帧

- 视频时序控制器,生成所需输出时序的时序波形(本例中为1080p、60FPs)。

- 视频处理子系统,执行从RGB到YUV色彩空间的转换

- AXI Stream转视频输出,可将AXI Stream内部视频转换为并行视频,并为HDMI芯片提供适当的同步信号

- 时钟向导,用于生成FPGA内部时钟(MIPI和MIG基准时钟为200MHz,视频管道为150MHz。MicroBlaze在内部使用较慢的MIG生成时钟)

- UART Lite,用于与用户进行处理通信

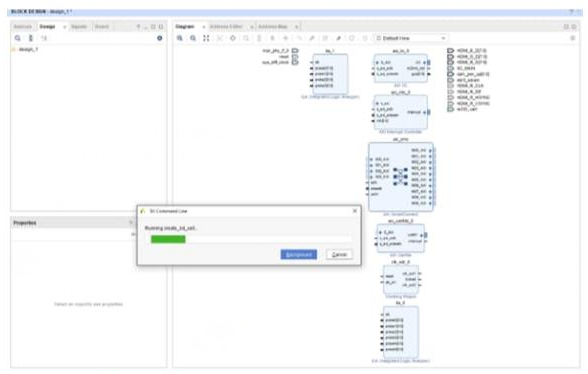

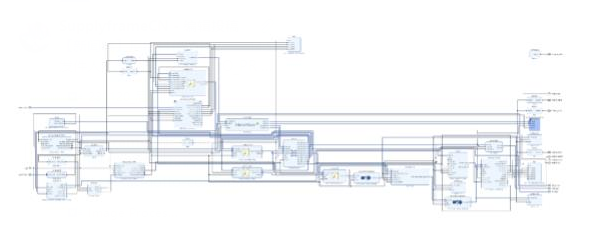

这些模块通过AXI Stream和AXI4接口连接。通过AMD Vivado™ ML版Tcl窗口(图1)中的框图脚本,可以重建最终的模块设计。

图1:Tcl命令窗口(图源:作者)

通过该窗口,可开始在Vivado中重建项目,如图2所示。此过程可能需要几分钟才能完成。

图2:重建项目(图源:作者)

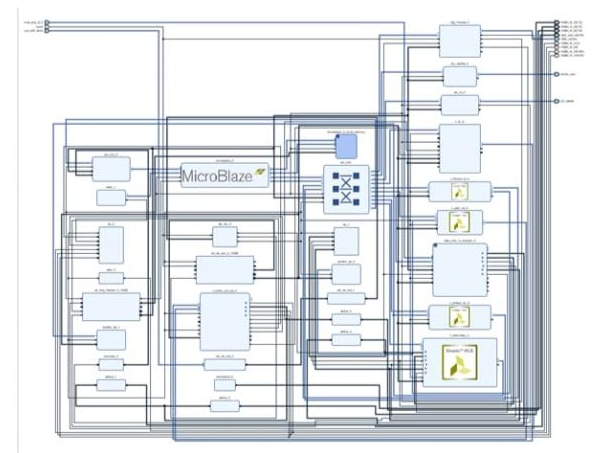

重建完成后,就可以探索项目设计了(图3)。

图3:完整的设计(图源:作者)

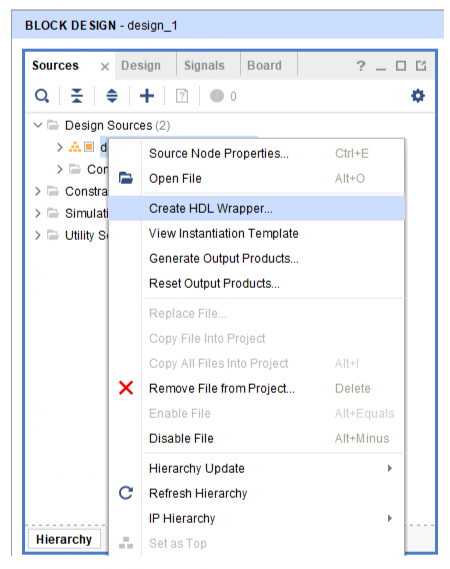

新建一个顶层HDL包装器,如图4所示。

图4:新建HDL包装器(图源:作者)

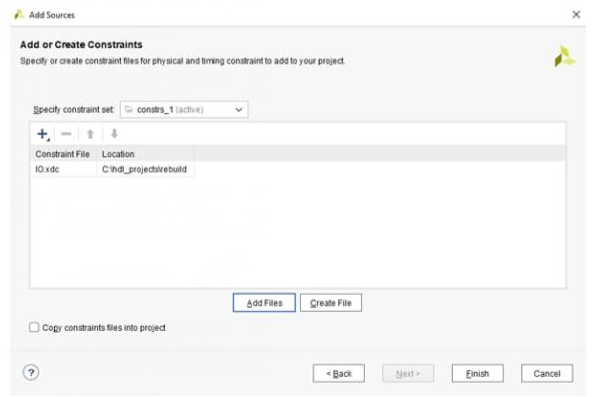

添加定义引脚的XDC约束。选择“添加源”并选择约束(图5)。

图5:添加约束条件(图源:作者)

选择IO.xdc文件(图6)。

图6:选择IO.xdc文件作为约束条件(图源:作者)

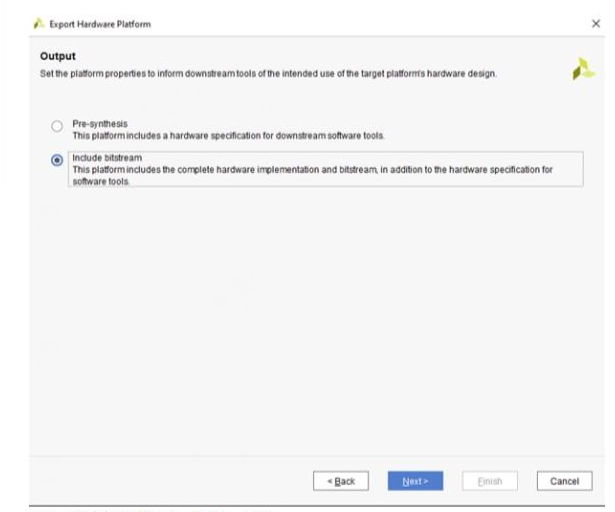

现在,我们就可以构建项目并生成位流。获取到位流后,就可以将其导出为Xilinx支持存档(XSA)文件,以便在Vitis中开发软件(图7)。

图7:将硬件导出到Vitis(图源:作者)

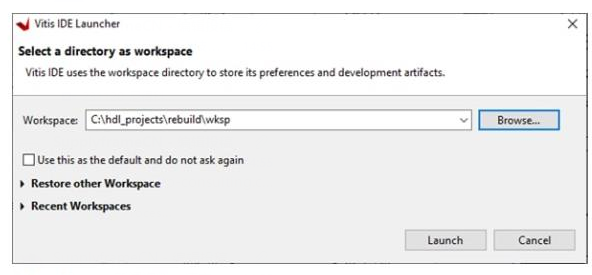

打开Vitis,并为工作区选择工作目录(图8)。所有文件和应用程序都将存储在这个位置。

图8:选择工作区(图源:作者)

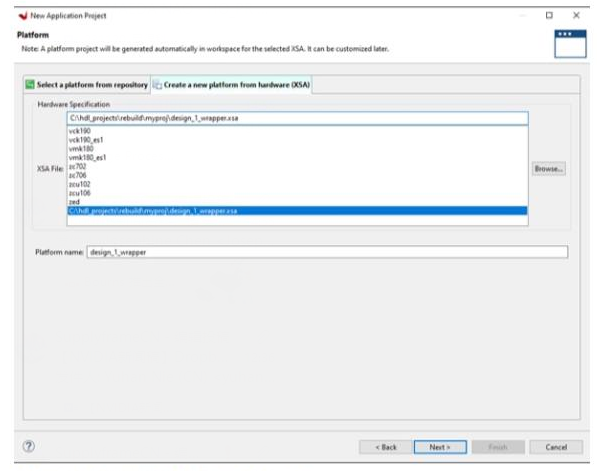

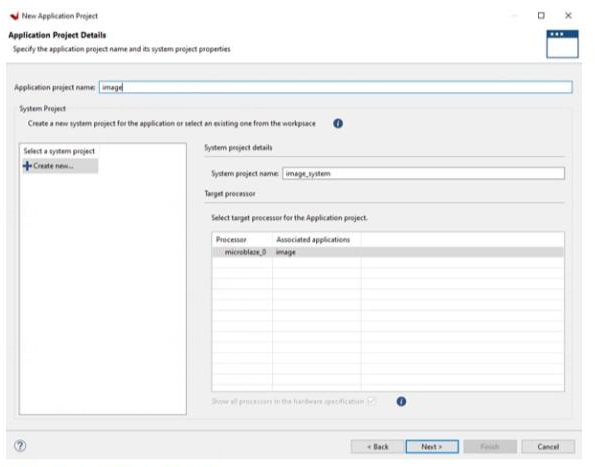

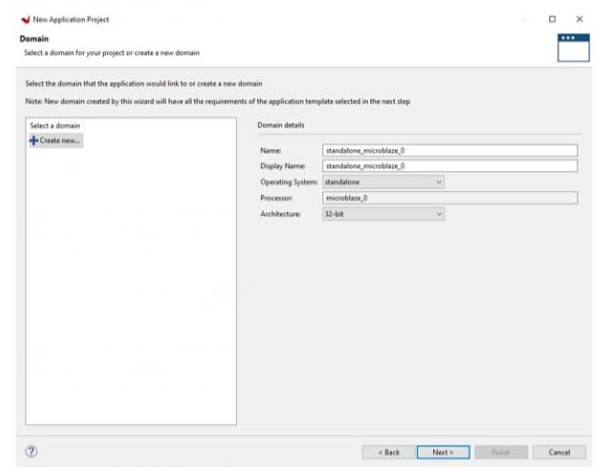

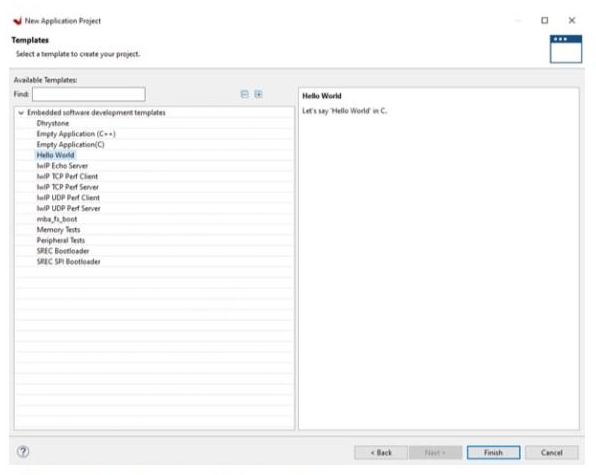

在Vitis中新建应用程序项目,将刚才导出的XSA作为目标,然后选择“Hello World”应用程序(图9 – 13)。

图9:选择应用程序项目(图源:作者)

图10:选择刚才导出的XSA文件(图源:作者)

图11:选择目标处理器(图源:作者)

图12:选择域(图源:作者)

图13:选择“Hello World”应用程序(图源:作者)

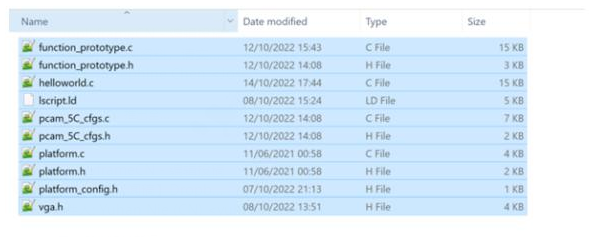

打开图8中新建的工作区src文件夹,将其中的文件替换为图14所示的文件。

图14:将文件复制到工作区(图源:作者)

这些文件将出现在项目源文件下(图15)。

图15:确保文件已导入(图源:作者)

构建应用程序(图16)。

图16:构建应用程序(图源:作者)

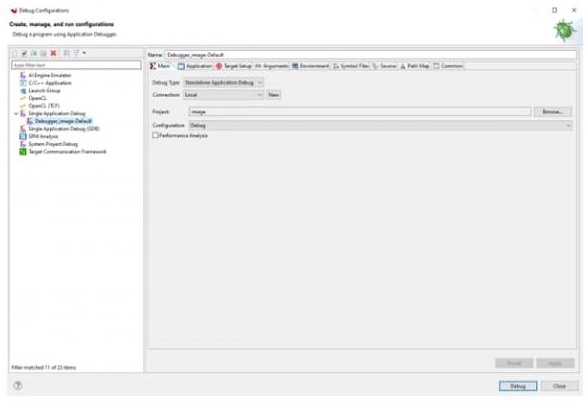

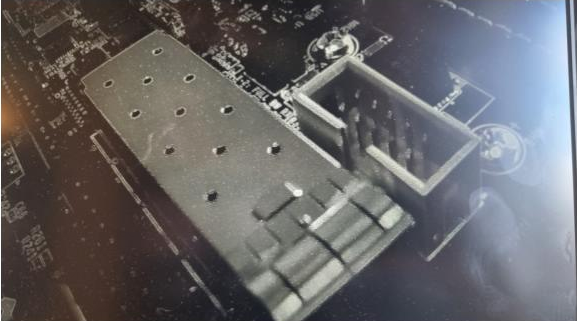

新建调试应用程序,并通过JTAG下载到AC701评估板。将FMC Pcam适配器和Pcam模块组装到电路板上(图17 – 19)。

图17:设置硬件(图源:作者)

图18:配置调试应用程序(图源:作者)

图19:查看调试应用程序设置(图源:作者)

连接到HDMI目标机后,该目标机将下载调试应用程序并运行,实现图像显示和透传。如果您想了解软件设计,请查看AMD Vitis™统一软件平台中的软件应用程序。请注意,必须配置多个I²C开关,才能同时与摄像头和HDMI芯片通信(图20)。

图20:简单的RGB图像透传(图源:作者)

为了创建执行边缘检测的IP核,我们将使用Matlab和Simulink建立能够放入图像处理链中的IP块。

边缘检测算法

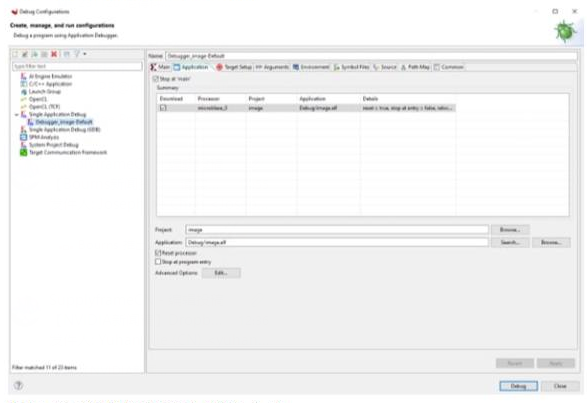

在Matlab中新建一个Simulink图表,并添加以下元素:

- 从多媒体文件:允许使用测试工作台中的AVI文件或MPEG文件

- 从帧到像素:将输出视频转换为像素流

- 从像素到帧:将像素流转换为帧

- 两个视频查看器

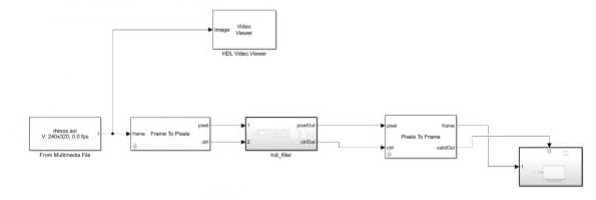

新建一个子模块,并添加以下内容:

- 索贝尔滤波器:其输出为1或0,取决于是否存在边缘

- 常量blocjs:设置为0和255

- 开关

- 像素流校准器

- 新建另一个子模块

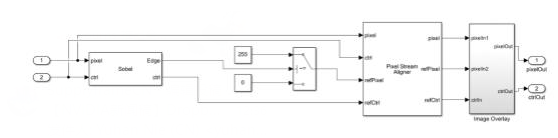

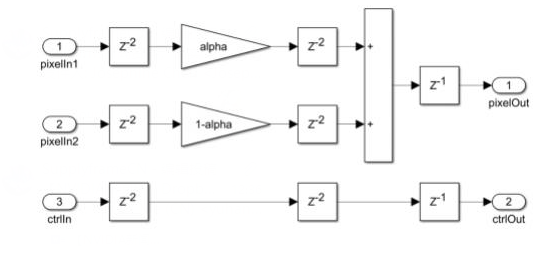

图像合并子模块

- 两个增益块:一个用于1-Alpha,另一个用于Alpha

- 延迟元件

- 求和

最终的图表应与图21 – 23一致。

图21:上层设计(图源:作者)

图22:HDL过滤器模块(图源:作者)

图23:图像叠加(图源:作者)

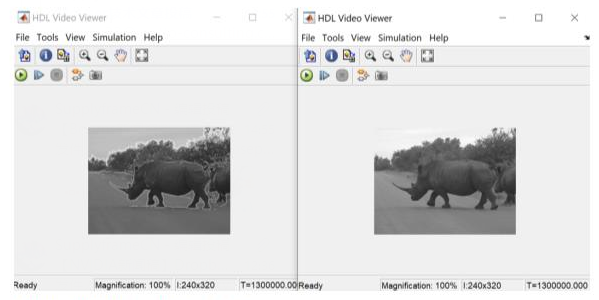

有了这些模块,我们就可以运行仿真,并将输入图像的结果与输出图像进行比较。

在输出视频中,请注意Sobel的结果叠加到输入视频上时边缘是如何增强的(图24)。

图24:Simulink仿真(图源:作者)

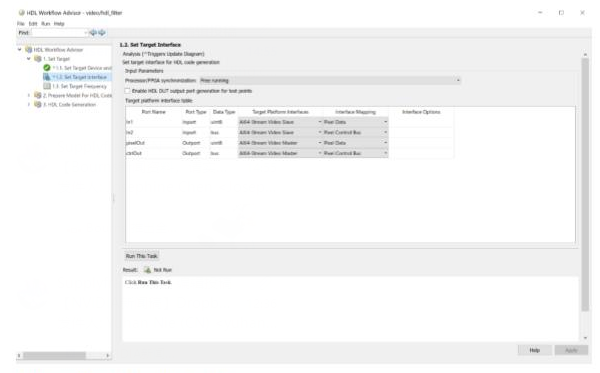

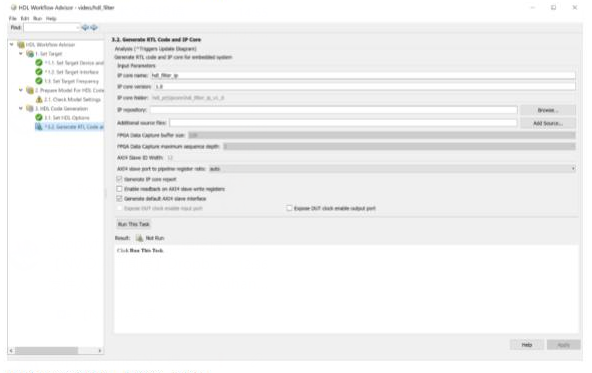

要生成HDL,我们可以使用HDL工作流程助手和SoC Blockset来生成具有AXI Stream接口和AXI4 Lite配置寄存器的IP模块。

IP创建的关键要素是将像素流和控制端口映射到生成的IP块上的AXI Stream接口,这样就可以轻松地将IP块集成到我们的Vivado设计中(图25和26)。

图25:选择AXI接口(图源:作者)

图26:生成HDL(图源:作者)

生成后,我们可以将此IP核添加回Vivado项目。在Vivado中新建一个IP资源库,并添加我们刚刚创建的IP(图27)。

图27:更新后的Vivado图表(图源:作者)

将IP块添加到Vivado设计中。我们可以将其添加到VPSS和AXIS-to-Video Out块之间。该IP块处理的是灰度图像,而在VPSS的YUV444输出中,Y通道是亮度通道,因而我们在两个块之间添加一个AXI子集转换器,并且只提取TData数据流的低8位,因为这就是我们需要的信息。在IP块的输出端,添加另一个AXIS子集转换器(将8位TData转换为24位),将UV元素设置为0x80,将Y元素设置为IP块的输出。

然后,我们就可以重建该设计并生成位流。获取到位流后,就可以导出XSA文件并在Vitis中更新XSA文件,从而为FPGA设计提供新的位文件,其中就包括IP块。默认情况下,您无需自行更改或启用软件中的任何功能,因此应用程序应该能够立即开始运行。请注意,HDMI显示屏上的输出显示的是灰度图像(图28)。

图28:生成的输出图像(图源:作者)

总结

该项目表明,创建运行在AMD FPGA上的图像处理系统并不是一件难事。

AMD、AMD箭头标识、Artix、MicroBlaze、LogiCORE、Vivado和Vitis以及上述标识的组合均为Advanced Micro Devices, Inc.的商标。本文中使用的其他产品名称仅用于识别目的,它们可能是其各自所有者的商标。

作者简介

Adam Taylor是嵌入式系统教授、工程负责人,也是FPGA/片上系统和电子设计领域的知名专家。

芯耀

芯耀

1963

1963