双脉冲测试中一个重要目标是,准确测量能量损耗。在示波器中进行准确的功率、能量测试,关键的一步是在电压探头和电流探头之间进行校准,消除时序偏差。

双脉冲测试软件(WBG-DPT)在4系、5系和6系示波器上均可使用,该软件包括一种新的专为双脉冲测试设计的消除时序偏差(deskew)的校准技术。这种新的方法与传统方法大有不同,测试速度显著加快,缩短了测试时间。

该技术适用于使用场效应晶体管或 IGBT 的功率转换器。在本篇文章中,我们将使用 FET 术语,来使得描述简单明了。

为什么要消除时序偏差(deskew)?

在设计任意一种功率变换器时,都必须尽量减少开关过程中的能量损耗。这种能量损耗可以使用示波器进行测量。一般方法是将同一时刻的电压和电流采样相乘,生成功率波形。

p(t) = v(t)*i(t)

由于功率波形表示随时间变化的能量消耗,因此可以通过对功率波形进行积分来确定能量:

E = ∫p(t)dt

要准确测量能量损耗,电流和电压波形的转换应在时间上保持一致。因此,为了准确进行能量损耗测量,设计者必须矫正测试夹具和探头造成的延迟。

一般来讲,在测试装置上开始任何测量之前都要计算探头之间的偏差。对于低电压应用,可以使用函数发生器和时序偏差校准夹具(deskew 夹具)(Tektronix P/N 067-1686-03)进行校准。但是,这种方法对于高电压和大电流应用而言,并非最佳选择。

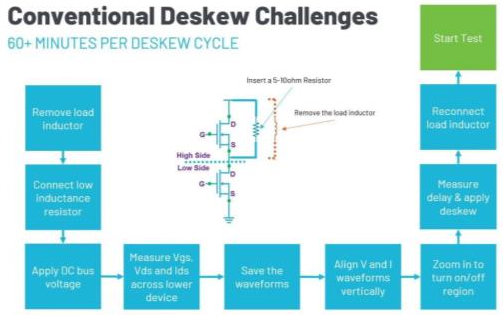

为了匹配更高功率下低压漏-源极电压(VDS)和漏极电流(ID)的测量,传统技术需要重新布线测试装置。这要求移除负载电感,并用电阻取而代之。接下来进行测量,需要匹配 VDS 和 ID 测量值。这个过程可能需要一个小时或更长时间。

一种新的时序偏差校准(deskew)方法

泰克 WBG-DPT 解决方案是业内首创的基于软件的时序偏差校准(deskew)技术,无需重新布线,只需在进行双脉冲测量后即可执行。在新方法中,采集漏极电流 (ID) 用作参考波形。在导通期间,利用测试电路的参数模型计算出低压侧 VDS 对齐波形,其计算后的波形参考 ID 波形,相对于 ID 没有时序偏移。消除时序偏差的算法确定计算出的 VDS 波形与测量出的 VDS 波形之间的时序偏差。然后将deskew校准的数据修正到 VDS 测量通道。

时序偏差校准过程

如上所述,时序偏差校准可在测量后进行。在开始双脉冲测试时,无需担心 VDS 和 ID 之间的偏差,随后选择deskew设置并提供以下参数:

图 3. 用于建立 VDS_low 对齐波形的等效电路。该电路假定使用一个电流观察电阻来测量 ID。

在deskew菜单中输入的参数用于构建 VDS 对应波形。波形使用基尔霍夫电压定律建立:

![]()

其中

VDD - VDS_high 表示电源轨电压和高压端场效应晶体管FET上的压降。需要注意,在开启期间,由于 VDD 是固定的,而 VDS_high是高压端场效应晶体管FET本体二极管上的电压,所以这个量是恒定的。

- Rshunt是分流电阻。

- ID 是根据 Rshunt 上的压降测得的漏极电流。

- dID /dt 是测得的漏极电流变化率。

- Leff 是整个电源回路的有效电感。

如上所述,在开启期间,VDD - VDS_high 实际上是恒定的。Rshunt和Leff 也是恒定的。 这意味着模拟的 VDS_low 走线波形是 ID的函数。

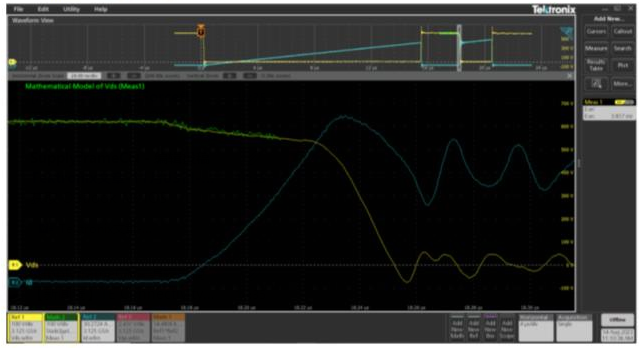

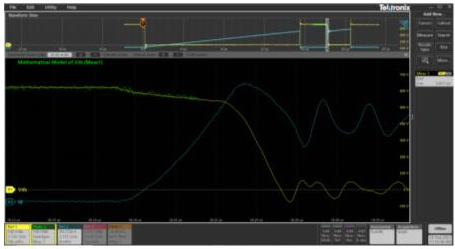

配置完参数后,用户按下 WBG 的deskew按钮。系统将根据指定的参数和漏极电流生成 VDS 的数学模型。 该波形将显示在屏幕上。

图 4. 根据 ID 计算出的 VDS 对齐波形与测量的 VDS波形进行比较。偏移是对齐波形和测量波形之间的时间差。计算出偏斜后,就可以从ID 波形中去除偏斜。

如上图所示,有效电感Leff考虑到了整个环路的 "叠加 "。因此,Leff 通常是未知的,而这个参数需要反复调整。简单地将纠偏过程反复运行,并对 Leff 进行调整,直到计算出的对齐波形和测量出的 VDS波形具有相同的形状。如果计算出的 VDS对齐波形与测量的 VDS波形在形状上存在差异,可以调整参数并再次运行校准时间偏差。

一旦参数设置准确,对齐波形和测量波形将具有相同的形状,系统就能确定并纠正偏斜。偏斜值显示在Deskew设置中,并自动应用于连接 VDS信号的通道。

这一新流程可以准确地计算偏斜值,并将时序偏差校准时间从一小时或更长时间缩短到 5 至 10 分钟。

芯耀

芯耀

923

923

下载ECAD模型

下载ECAD模型