在2023年的FPGA领域顶级会议FPL (International Conference on Field Programmable Logic and Applications) 上,由中科驭数团队、中国科学院计算技术研究所处理器芯片全国重点实验室团队共同完成的论文《Co-ViSu: a Video Super-Resolution Accelerator Exploiting Codec Information Reuse》获得FPL2023最佳论文奖。该项工作由鄢贵海指导完成,作者包括樊海爽、吴婧雅、卢文岩、李晓维。论文第一作者樊海爽受邀在会上做口头报告。

▲ 《Co-ViSu: a Video Super-Resolution Accelerator Exploiting Codec Information Reuse》获得FPL2023最佳论文奖

▲ 论文第一作者樊海爽受邀在会上做口头报告

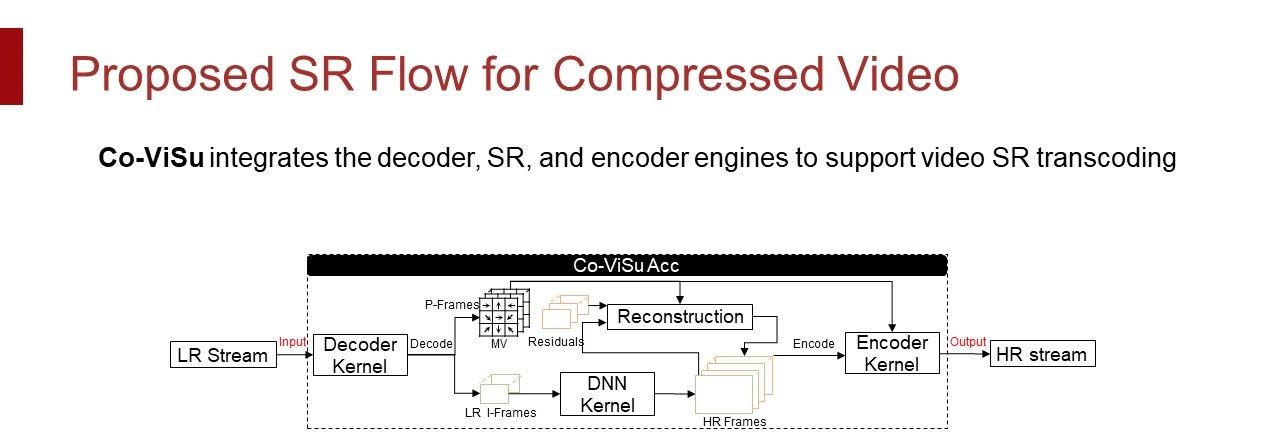

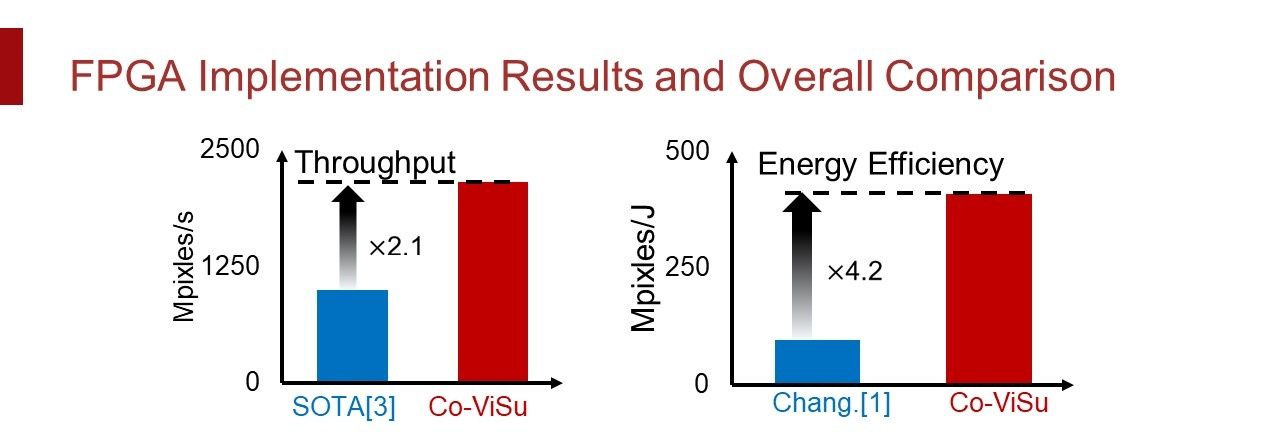

Co-ViSu是一个针对压缩域视频超分辨率任务的FPGA加速引擎。视频分辨率是将低分辨率视频转化成高分辨率的任务,其在视频流服务、AV/VR、医学等领域都有重要的应用,与CNN相比其面临着计算复杂度和内存带宽需求更高的特点。本文提出的Co-ViSu首次在FPGA上协同设计实现视频编解码器和DNN加速器,通过复用视频压缩域编码信息,Co-ViSu极大地提高了视频超分系统的吞吐和能效,可支持280FPS的1080P到4K超分计算,相比于现有最高的SOTA方案吞吐量高2.1倍,能效比提升4.2倍。Co-ViSu协同设计方案可以很好地扩展到诸如视频分割、物体跟踪以及视频检测等视觉任务中。

FPL是可编程逻辑和可重构计算领域历史最悠久、最大的国际会议,也是该领域的顶级会议之一,主要收录可重构架构设计、应用、嵌入式处理、设计自动化等方向的研究工作。第33届FPL会议由瑞典查尔姆斯理工大学主办,Full-paper录用率为23.7%。

处理器芯片全国重点实验室是中国科学院批准正式启动建设的首批重点实验室之一。中科驭数和处理器芯片全国重点实验室为战略合作伙伴关系,双方积极推进产学研紧密合作,助推国产DPU技术创新高地建设。

2223

2223

下载ECAD模型

下载ECAD模型