如要在整个蜂窝移动网络中实现具有成本效益、可靠性和安全性的授时,所需的基础设施需要适当的架构、设计和管理。5G网络设备的时间精度要求更高,需要可靠且稳健的授时架构来保证网络性能。

随着网络从使用基于频分双工(FDD)的通信链路发展到使用时分双工(TDD),不仅出现了频率方面的需求,同时还产生了对精确相位和时间同步的需求。运营商在TDD网络中部署的设备依赖于GNSS、同步以太网(SyncE)和IEEE-1588精确时间协议(PTP)的组合,以在整个网络中提供准确的频率、相位和时间。

第三代合作伙伴计划(3GPP)第15版中引入了全新的5G RAN架构,此架构将基带单元(BBU)和远程无线电头端(RRH)拆分为集中式单元(CU)、分布式单元(DU)和无线电单元(RU)。这种全新的RAN架构形成了分散式的虚拟化网络,使运营商能够在整个网络中提升效率并降低成本。

这种分散产生了增强型通用公共无线电接口(eCPRI),可用于连接DU和RU。相比于以前用于将BBU连接到远程无线电头端(RRH)的CPRI链路,此接口具有明显的优势。由于eCPRI采用基于数据包的传输方式,因此现在通过使用PTP和SyncE实现与RU的同步。

此外,开放式RAN运动还基于3GPP的建议实现了硬件和接口标准化。O-RAN联盟定义了四个用于通过前传网络分配时序的方案。在全部四种配置中,RU要么从DU接收时序,要么从附近的主参考时钟(PRTC)接收时序。尽管存在各种时序流,但要通过O-RAN网络支持时序分配,所需的关键功能仍然基于SyncE、IEEE-1588和GNSS。

授时标准

我们采取了各种授时建议措施,以便使每个网络元素都能满足特定的频率、相位和时间要求,确保端到端网络正常运行。对于TDD蜂窝移动网络,3GPP的定义将不同基站之间时间同步的基本同步服务要求设定为3 µs。国际电信联盟电信标准化部门(ITU-T)提出了一系列建议,这些建议基于3GPP的要求定义了公共点和终端应用之间的最大绝对时间误差(最大|TE|),即±1.5 µs。

GNSS成为通过PRTC在TDD网络中获取时间的主要方式。一种方法是将GNSS接收器置于无线电基站,但这需要良好的天空视距才能可靠运行。如果无线电位于室内或遮挡清晰视线的位置,则无法利用本地GNSS源。由于天气事件等造成的视线遮挡,或者欺骗或干扰产生的针对性攻击,GNSS还可能发生中断。规划的5G NR基站数量非常多,这使运营商难以承担安装和维护GNSS源的成本。

除了可靠性和部署成本方面的问题之外,GNSS还需要更加精确的PRTC,增强型主参考时钟(ePRTC)的定义由此应运而生。ePRTC可通过GNSS或可追溯到UTC的其他网络标准时间源发起授时。获取时间后,ePRTC使用铯原子钟或更出色的原子参考振荡器为网络维持可靠、高度精确和稳定的时间参考。使用自主原子时间参考可提供一定程度的抗干扰能力,并在最长14天内提供稳定的保持功能。ePRTC的时间精度为UTC ± 30 ns,与以前的PRTC规定的± 100 ns精度相比,改进十分明显。这种精度提升充分满足了5G NR的严苛网络要求。

电信边界时钟(T-BC)和目标时钟(T-TSC)是确保网络精确传输时间的其他重要元素。T-BC通常位于交换机或路由器中,负责从上游链路恢复时间并将其传递给下游链路。T-BC/T-TSC内的以太网设备时钟(EEC)(又称为SyncE)能够提供稳定且精确的频率参考,可追溯到主参考时钟(PRC/PRS),频率精度为0.01 pbb。如果将SyncE与PTP结合使用,可带来多项精度和成本优化方面的优势。SyncE参考的精度高于本地振荡器,能够驱动PTP引擎。这样,PTP引擎便可滤除大量的数据包延时变化(PDV),从而提高整体相位精度。

基本时间精度要求

对于TDD网络部署,端到端网络的时间精度限值为±1.5 µs,详见G.8271。根据该值,可以得出定义每个网络元素所需性能的时序预算,从而满足端到端限制。G.8273.2中定义的时钟设备规范将时间误差细分为恒定时间误差和动态时间误差。恒定时间误差(cTE)表示因网络固有延时而出现的误差。这些误差无法滤除;它们会随着时间在网络中的传输而累积。动态时间误差(dTE)是因高频或低频噪声而产生的误差。对网络参考时钟进行正确的滤波可以减少这些误差。

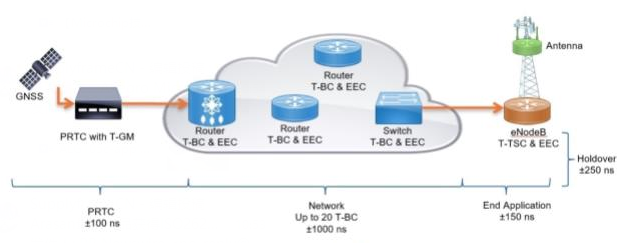

图1.为满足延迟时间规范,网络的时序限值必须保持在±1.5 µs,其中总的时序限值分布在各个网络元素中。

±1.5 µs的基本网络限制在各个网络元素之间分配。对于4G网络,每个网络元素的允许时间误差预算如图1所示。带T-GM的PRTC的误差限值为±100 ns,将基于分类级别为每个T-BC分配一个最大|TE|。表1详细说明了分配给每个时钟类的最大|TE|。

表1.G.8372.2 T-BC和T-TSC时钟设备时间误差限值。

此外,根据分类级别为每个T-BC分配一个cTE限值。非对称网络链路和终端应用各自也会收到分配的最大TE值。支持最多10跃程A类T-BC或20跃程B类T-BC的网络足以满足基本网络限制。

高级时间精度要求

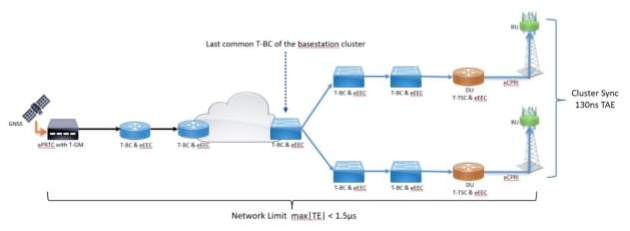

4G和5G网络的基本端到端要求都是1.5 µs。但是,某些无线电技术(例如协作多点、载波聚合或大规模多输入多输出(MIMO))具有更严格的时间误差限制。图2显示了相对时间误差的概念,其中描述了终端应用的时间误差,该应用可追溯到无线电集群的最后一个公共点。NR部署所需的高级时间精度要求将集群内允许的相对时间对齐误差(TAE)降低至130 ns或±65 ns的最大TE。

图2. 5G网络中的T-BC的最大|TE|基于分类级别。

除了前文介绍的全新ePRTC之外,表1还列出了新的T-BC和T-TSC时钟类,ITU-T已确定其支持这些更严格的限制。G.8372.2 C类和新出现的D类要求进一步限制了每个元素可以引入的允许TE。每个C类和D类元素都需要支持G.8262.1中定义的增强型以太网设备时钟(eEEC)标准。

时序设计

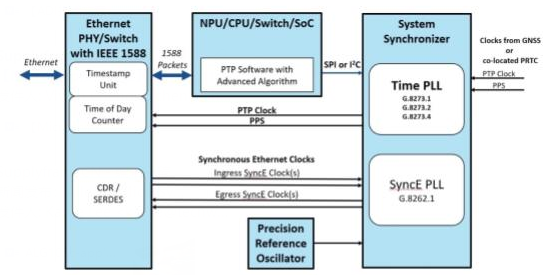

图3显示了用于在设备设计中维护、管理和分配时序的关键组件的典型框图。在设计CU、DU或RU应用时,可将其用作指南。时序设计的主要功能是创建一个系统同步器,其包含一个或多个复杂的锁相环(PLL),可提供实现精确频率和时间同步所需的功能。这些同步器负责时钟监视、参考切换、滤波和同步准确时钟,使设备与网络时间保持同步。同一同步器中的多个PLL允许为SyncE、PTP和其他时间要求提供支持。支持多个输入和输出的同步器可以监视和同步各种接口的时钟。

对于SyncE支持,有一个或多个恢复时钟连接到对各种输入参考进行认证和管理的系统同步器。同步器将选择一个恢复时钟作为主时钟,SyncE PLL会在将时钟重新分配到出口节点之前对其进行滤波。如果需要支持增强型以太网电子时钟(eEEC),如G.8262.1中的定义,则务必确保在信号丢失(LOS)条件下可以快速抑制SyncE恢复时钟。这确保可以满足G.8262.1的短期和长期相位瞬态限制。

图3. 5G网络时序依赖于交换芯片和同步器。

PTP的正确实现需要准确的时间戳功能和专用软件,以正常保持精确的时间同步。为了尽量减少延时,时间戳单元应尽可能靠近盒子的边缘。对于B类设备,具有10 ns精度的时间戳单元足以满足要求。要满足C类时钟要求,时间戳单元的精度应达到4 ns或更高。需要一个PTP软件协议栈,最重要的是需要一种稳健的时间算法来处理PTP数据包通信和时间戳,并对系统同步器内部的时间PLL进行频率和相位调整。时间PLL也可以锁定到来自本地PRTC或提供每秒脉冲(PPS)参考的其他设备的PPS输入。

最后,精密振荡器可在启动时提供基础频率,并确保在网络中断的情况下稳定运行。并非所有用例都需要强大的保持功能,但设备的位置越靠近网络核心,振荡器就需要越稳定。

C类和D类设计注意事项

设计需满足C类和D类要求的系统中的时序架构时应十分小心。除了提高时间戳的精度和需要在LOS条件下为入口eEEC提供抑制功能外,还可以应用校准技术来正确管理给定设计中的cTE和dTE。随着工程师努力尽可能降低设备引入的时间误差,提供片上或系统内校准功能正变得愈加普遍且十分必要。在选择元件时,需要考虑识别由于工艺、温度和电压产生的潜在cTE来源。

需要尽可能减少由缓冲器、FPGA、时间戳单元或授时路径中的其他器件引入的延时,并且如果可能,在电路板和/或系统级使用校准技术来纠正这些延时。对于通过缓冲器和其他器件的输入到输出传输延时,可以通过提供返回系统同步器的反馈路径进行分配,以实现动态延时校准。由于高级时间精度限制引入的相对时间误差要求,仅关注盒子的输入到输出延时已无法再满足需求。应当注意系统内每个PPS输出的输出到输出对齐。此外,对于机架设备,每个输出的线路卡PLL带宽应该相同或设置得尽可能高,以确保设备尽可能对所有输出的任何相位变化进行相同的处理。

同步器、时间戳PHY和交换机可以补偿电路板设计中已知的固有延时。从电路板级别来看,静态校准技术可以按输出或按端口补偿板间延时和传输延时。同步器可为GNSS或G.703 1PPS接口提供按输入的板间延时和缓冲器补偿、皮秒相位调整分辨率、按输出的板间延时补偿以及按输入或按输出的线缆延时补偿。此外,高级时间戳器件可按端口提供具有皮秒分辨率的时间戳校准。这些功能有助于灵活地测量和校正系统内的相位误差,以确保最大限度地降低TE。

结论

同步要求和功能不断发展,催生了适用于5G及以后网络的超低延迟、高带宽和先进的全新无线电应用。若要满足网络设备的全新更高时间精度标准,必须仔细规划时序架构。

芯耀

芯耀

1831

1831

下载ECAD模型

下载ECAD模型