你知道吗?你手上的芯片,被扎过针,被电击,可能还被高低温烘烤冷冻;

每一颗交付到您手上,经过了严格的测试筛选,尤其车规芯片,整体的测试覆盖项和卡控指标更加严格

今天,和大家介绍下最常见,最核心的CP测试和FT测试

本文目录:

- 为什么要测试,为什么分开测试?

- CP测试和FT测试的具体不同

- 主要测试项

- CP和FT测试,对芯片设计有什么要求

为什么要测试,为什么要分开测试

为什么要测试?

芯片设计好,晶圆厂进行生产的过程,是化学反应和物理操作的过程(晶圆工艺),不同晶圆厂的工艺成熟度,性能不一样,可能导致芯片的功能,性能差别,不一定能够满足客户需求(比如功耗需求,电气特性需求等),因此要设计测试方案,把不符合要求的剔除出来;

为什么分开测试?

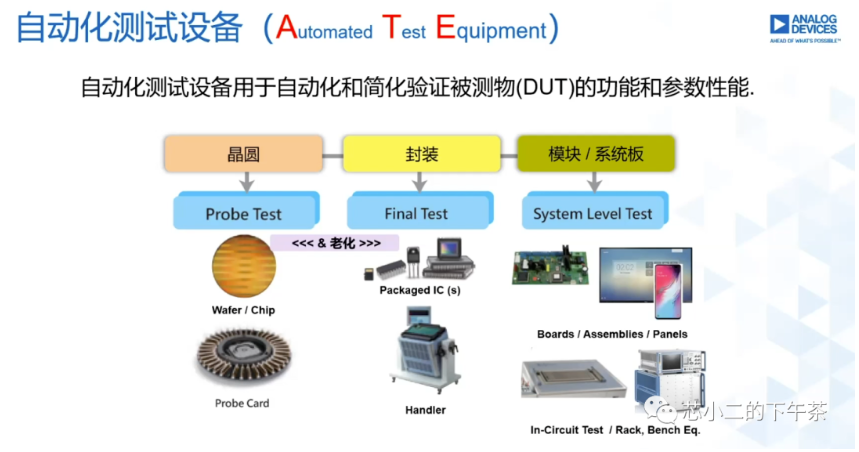

芯片测试一般会分2大步骤,一个叫CP(Chip Probing),一个叫FT(Final Test)

CP是针对晶圆的测试,FT是针对封装好的芯片的测试,流程如下

分两个步骤,主要是如何最高的性价比,把合格芯片挑选出来;

FT因为是针对封装好芯片的测试,因此芯片的引线,基板,封装材料这些已完成,成本都在,如果晶圆DIE是坏的,那就浪费了

CP测试的目的,就是在封装前就把坏的芯片DIE筛选出来;

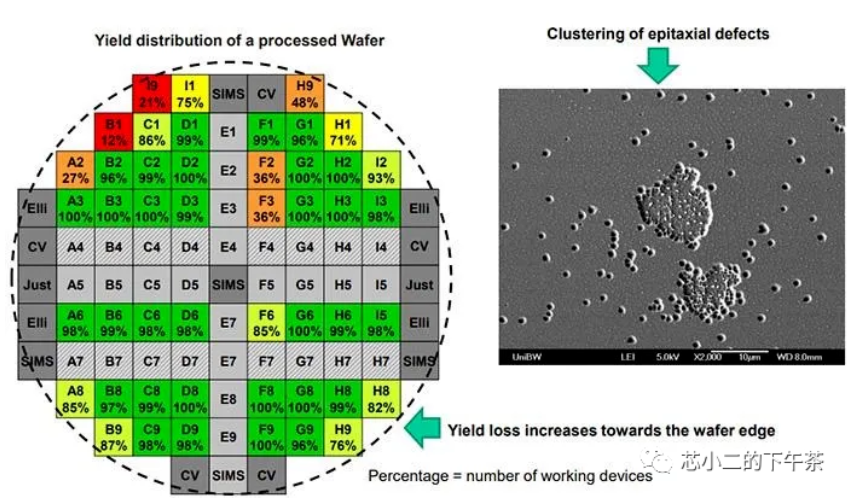

如下是晶圆的不同区域对应的Yield Rate(良率),可以看到越靠晶圆旁边的位置,良率越低

转自 知乎温戈

图片转自 网络不知名

CP测试和FT测试的不同

逆因为一个测试对象载体在晶圆(一个晶圆一般有上千颗芯片),一个测试对象是封装好的芯片,因此其测试最大的不同是测试用的设备

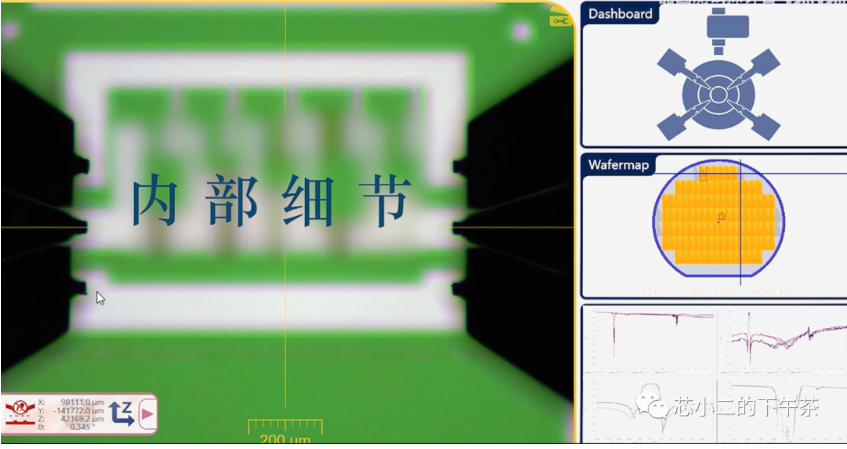

如下是CP测试示意图,测试用探针卡,从ATE测试设备上显微镜看到的具体操作图片,以及正在操作的ATE设备

ATE设备基于编写好的程序(测试用例),对晶圆上的每一颗芯片进行测试,这里探针的移动距离在0.Xum级别一般

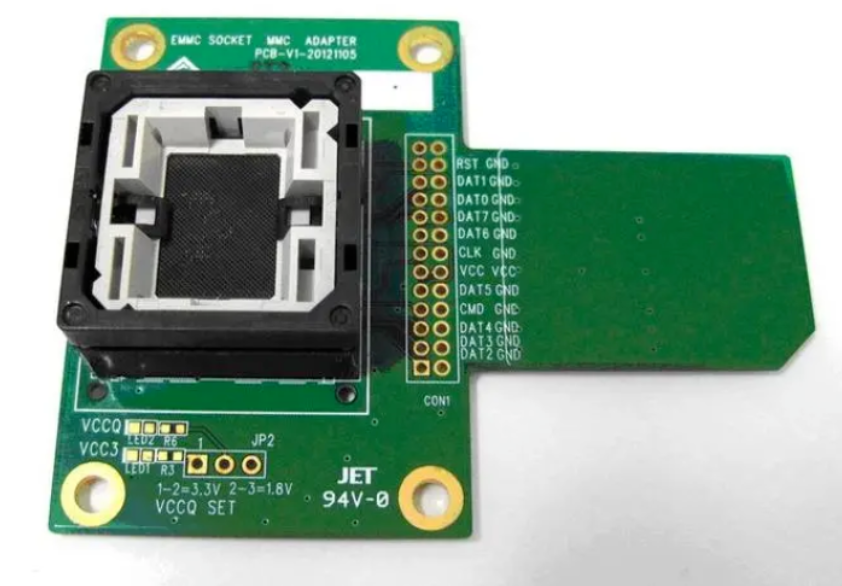

而FT部分,大家可能会更加好理解,因为平时大家做测试板的类似,主要区别可能就是FT测试用Socket座子(因为测试完成要取出来)

为了提高效率,一个测试板上可以放很多这样的Socket座子;

因为CP和FT在不同阶段,其测试对象,测试工具的差异带来的限制,测试侧重点会不一样

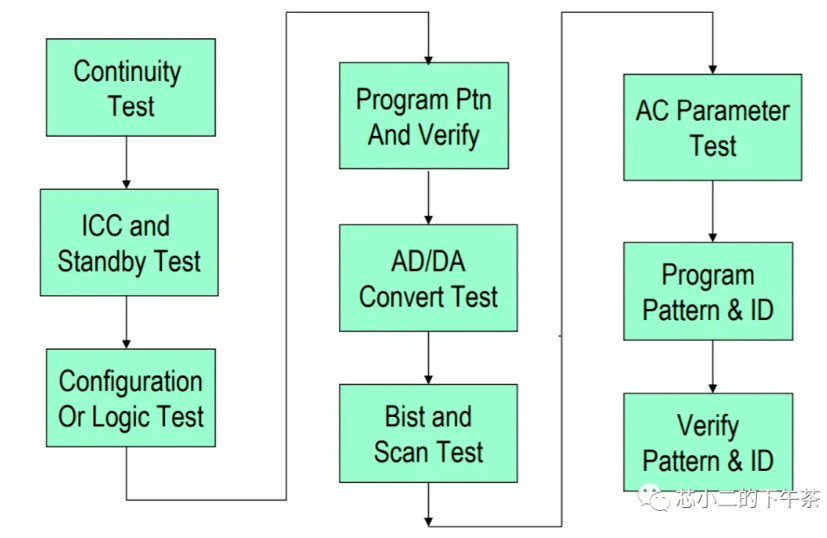

CP测试阶段会尽可能覆盖对良率影响大的用例,比如短路,逻辑功能,内部存储;

CP因为采用了探针,对于高速信号,小信号,大电流方面的测试,一般不合适,会放到FT去测试;

主要测试项

本章节主要参考资料:知乎温戈

DC性能测试

- Continuity Test

- Continuity Test

- Leakage Test (IIL/IIH)

- Power Supply

- Current Test (IDDQ)

- Other Current/Voltage Test (IOZL/IOZH, IOS, VOL/IOL, VOH/IOH)

- LDO,DCDC 电源测试

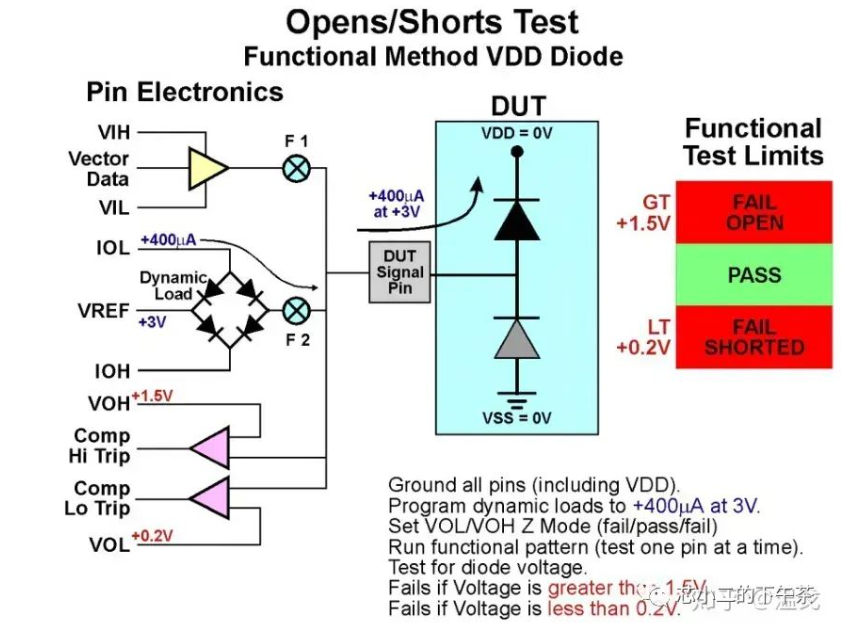

以Continuity测试举例,主要是检查芯片的引脚以及和机台的连接是否完好

测试中,DUT(Device Under Test)的引脚都挂有上下两个保护二极管,根据二极管单向导通以及截至电压的特性,对其拉/灌电流,然后测试电压,看起是否在设定的limit范围内

转自 知乎温戈

整个过程是由ATE里的instruments PE(Pin Electronics)完成

AC参数测试

主要是AC Timing Tests,包含Setup Time, Hold Time, Propagation Delay等时序的检查

特别外设功能测试(ADC/DAC)

主要是数模/模数混合测试,检查ADC/DAC性能是否符合预期,主要包括静态测试和动态测试:

Static Test – Histogram method (INL, DNL)

Dynamic Test – SNR, THD, SINAD

数字功能测试

这部分的测试主要是跑测试向量(Pattern),Pattern则是设计公司的DFT工程师用ATPG(auto test pattern generation)工具生成的

Pattern测试基本就是加激励,然后捕捉输出,再和期望值进行比较。

与Functional Test相对应的的是Structure Test,包括Scan,Boundary Scan等

SCAN是检测芯片逻辑功能是否正确

Boundary SCAN则是检测芯片管脚功能是否正确

BIST(Build In Self Test),检查内部存储的读写功能是否正确

对芯片设计的要求

在设计阶段,就需要考虑如何支撑芯片的测试要求,这在芯片设计里面有一个专门的岗位,DFT工程师 (Design For Test)

DFT逻辑通常包含SCAN、Boundary SCAN、各类BIST、各类Function Test Mode以及一些Debug Mode

测试人员需要在芯片设计之初就准备好TestPlan,根据各自芯片的规格参数规划好测试内容和测试方法,并和DFT工程师及其他设计人员讨论;

芯耀

芯耀

1884

1884