300亿新台币(67亿人民币),放到中国互联网公司历史融资排名中能挤入前十位置。然而这些钱,仅是ASML为中国台湾企业台积电发展2nm工艺制程的第一期投资金额。

据中国台湾媒体报道,半导体设备制造商ASML在中国台湾投入巨资,向中国台湾“经济部”申请A+企业创新研发淬炼计划,研发制造2nm晶圆光量测设备(前道量/检测设备的一种)。经济部表示,将以多个方面进行审查,包括如何协助供应链技术升级以及国产自制率,最快5月拍板定案。按照此前规划,台积电最早将于2025年2025年开始量产其2nm制程技术。

ASML如此大手笔的投资,就是要保持公司与台积电的技术联盟在2nm时代继续保持全球领先。事实上就在几天后的4月10日,日本媒体就报道经济产业省正在敲定计划,将额外向日本新成立的晶圆制造商Rapidus提供3,000亿日元(约22.7亿美元)补贴,用以在日本北海道兴建半导体厂。而此前Rapidus已宣布将在日本北部岛屿北海道的千岁市建造一座2nm晶圆代工厂。

在2nm制程的争夺战上,肯定也少不了韩国的身影。日本宣布加码2nm制程的同一天(4月10日),韩国国际广播电台报道,韩国政府决定在半导体等11个核心投资领域选定40个项目,每年投入70%的研发预算进行支援,计划到2030年总共投资13.5万亿韩元(约合102亿美元)。4月6日韩国科学和信息通信技术部已经宣布,到2027年私营和公共部门将至少投资160万亿韩元(1210亿美元)用于电池、半导体和显示器研发。该部门解释半导体行业的创新理念包括忆阻器器件优于DRAM和NAND、人工智能相关芯片设计、6G通信和自动驾驶、3纳米及更先进的工艺技术等。

各国大力争抢的2nm工艺是什么意思?要烧这么多钱,工艺进步究竟有多难?本文将带你梳理芯片工艺制程的变化,来了解不同工艺难度的差别。

等比例缩小时代

集成电路本质上是由一个个微小的晶体管、电阻、电容与电感组成的大规模复杂电路,通过金属线连接在一起,晶体管的性能水平也几乎就代表了芯片的性能水平。早期的集成电路就是将常见的电路板各个元器件的尺寸等比例缩小,最后进行封装。

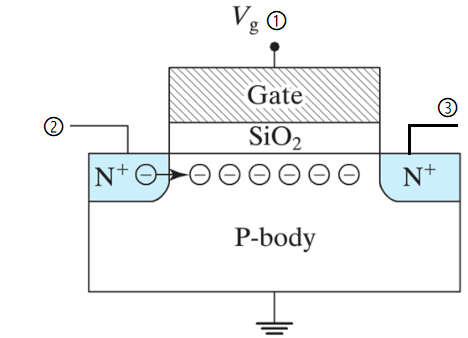

这里稍微讲一下模拟电路相关知识。集成电路的最底层结构是MOS管,MOS管的工作原理基于PN结。在硅材料的正负两极参杂P(磷)与N(氮)元素,N区自由电子多,而P区空穴多,两端在一开始均不带电。由于离子的扩散作用,N端的自由电子会自发的向P端移动来填补空穴,这样就会让P、N两端分别带正负电荷,当两端电场强度使得自由电子进出速度(电子的扩散与漂移)维持动态平衡的时候,就会在中央形成空间电荷区(耗尽区)。这也就是PN结的结构。

而MOS管的结构则是由金属栅极(Gate)、源极(Source)与漏极(Drain)组成。源极和漏极分别是两种不同参杂半导体组成,分别形成两个PN结。当向源极与漏极加电压时,在栅极无外加电场的情况下,电子由于PN结阻隔无法穿过中间的沟道,我们可以将这种状态定义为“0”。向栅极施加电场,衬底中的自由电子会被拉进沟道内,此时再向源极与漏极间加电压就能导通,我们MOS管的这种状态定义为“1”。有了0与1的信号,就可以构建更复杂的电路。而栅极通常用金属与氧化物组成,该结构也被称为金属氧化物半导体场效应管(metal-oxide semiconductor Field Effect Transistor,FET)。目前半导体主要使用MOS场效应管,即通常所称的MOS管,一般也能用晶体管指代它。

P型MOSFET 图源:维基百科

同样面积下塞入更多的晶体管,通常意味着集成电路的计算能力越强,因此持续降低晶体管大小就能增大晶体管密度,进而提升芯片性能。此前每一代工艺制程升级,制造商都能够将晶体管规格微缩0.7倍,从而实现15%的性能提升,50%的面积减小,40%的功耗降低以及35%的成本降低。这种等比例缩放持续进步的方式,被称为登纳德缩放定律(Dennard Scaling)。

这个时代的工艺难点在于如何设计出如何让布线让芯片更加稳定,尽量规避因工艺问题导致的断线、短路等问题,以及减少天线效应,合理设置屏蔽线等问题。不过在今天这些问题已经有了十分成熟的解决方法,这一类工艺目前也被称为成熟工艺。如果不出意外的话,晶体管与的大小可以一直减小,直到它的它的大小逼近硅原子的大小(0.22nm)。

不过既然有了这篇文章,那么意外一定会出现。这里举一个经典的例子,晶体管的源极与漏极相当于两个地铁站,我们缩小两站之间的距离就相当于降低沟道宽度,也就是降低晶体管的大小。但当地铁站之间的距离足够近时,两个站点就能直接连通,乘客就可以不乘坐地铁也能行走于两个站点之间。这里的乘客就是自由电子,乘客的自由移动就相当于晶体管漏电。当自由电子越来越多,晶体管就难以输出有辨识度的高低波形,从而失去作用。

因此,在晶体管缩小到22nm左右后,传统工艺就很难再进一步了。这时,如何增强对电子的控制能力就成为半导体技术再进一步的关键。

FinFET的诞生与工艺命名

1999年,美籍华人科学家胡正明(Chenming Hu)教授就提出了FinFET(Fin Field-Effect Transistor,鳍式场效应晶体管)概念。当时胡教授在加州大学领导一个研发小组,目标是研究如何将CMOS技术拓展到25nm领域,彼时提出了两种解决方案,一种是基于SOI的超薄绝缘层上硅体技术,适用于MEMS与功率器件,另一种就是立体结构的FinFET。

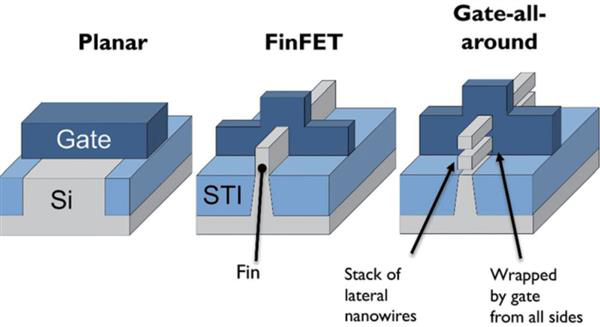

传统的MOSFET结构是平面的,只能在栅门的一侧控制电路的接通与断开。但是在FinFET架构中,栅门(Gate)被设计成类似鱼鳍的叉状3D架构,可以在电路的两侧控制电路的接通与断开。这种叉状3D架构不仅能改善电路控制和减少漏电流(leakage),同时让晶体管的栅极长度大幅度缩减。单个FinFET晶体管通常包含多个鳍片,这些鳍片并排排列并由同一栅极覆盖,可提高晶体管驱动强度和性能。

MOSFET与FinFET对比 图源:三星

从图片中我们能看到,FinFET拥有更“窄”的沟道,但由于增大了鳍片与栅极的接触面积,使得晶体管对电子的控制能力增强,自然就减少了漏电的概率。

这里需要提到一点,在FinFET商业化应用之前,芯片工艺大多还是按照晶体管真实体积大小来区分的。1992年,IEEE发布集成电路工艺命名规则,根据晶体管的Gate Length和Half-pitch Size来命名制程。Gate Length表示二极管Gate极的宽度,而Half-pitch Size代表的是芯片内部互联线间距离的一半,即光刻间距的一半。

FinFET突破了晶体管的平面维度,有效沟道变成了3维结构,难以用一个数据简单显示其准确含义。因此,台积电、英特尔、三星等厂商逐渐推出了适合自身的命名方式(主要是为了营销)。因此22nm之后的数字,纯粹是指采用特定技术制造的某一代芯片,不对应任何栅极的长度或间距。台积电的Philip Wong在Hot Chips 31主旨演讲中说:“它过去是技术节点,节点编号,意味着一些东西,晶圆上的一些功能。”“今天,这些数字只是数字。它们就像汽车模型——就像宝马5系或马自达6。数字是什么并不重要,它只是下一项技术的目的地,它的名称。我们不要把节点的名称与技术实际提供的相混淆。”因此在FinFET时代后,主要使用鳍片的宽度来命名工艺制程。

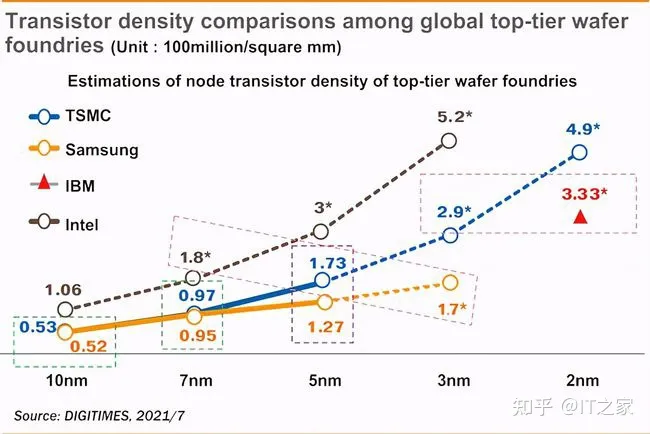

目前,英特尔芯片专家Mark Bohr提出的单位面积晶体管密度参数成为共识,它认为每个芯片制造商在提及工艺节点时,都应披露其逻辑晶体管密度,单位为MTr/mm2(每平方毫米数百万个晶体管)。因此,我们对比台积电7nm工艺与英特尔10nm工艺时,会发现它们的晶体管密度基本相同。

图源:知乎

FinFET的推出为摩尔定律成功“续命”了10年左右。不过随着芯片制造工艺进一步降低,FinFET也迎来了它的极限。在工艺达到5nm之后,晶体管间距离过近导致的漏电问题再次萦绕在芯片制造商头顶。

晶体管对电子的控制能力还能进一步增强吗?

GAAFET,无情的吞金兽

FinFET应用后,栅极与沟道的接触从单一平面变成了三个面,极大的提升了对电子的控制能力。那么当这项技术面对极限,再增加一个接触面不就好了吗?

芯片工程师就是这么想的,于是GAAFET(Gate-all-around FET,环绕栅极场效应晶体管)诞生了。GAAFET的栅极在垂直方向被分成多个条带鳍片,根据鳍片形状分为纳米管(Nanowire)结构与纳米片(Nanosheet)结构。GAAFET在沟道区域大幅增强对载流子控制,从而实现更好的性能,同时也更容易优化工艺。我们可以简单的理解为将FinFET的鳍片转90°,再向上堆高,来增加栅极和沟道的接触面积。

PlanarFET、FinFET与GAAFET对比 图源:互联网

然而,GAAFET的制造工艺十分复杂,有相当多的因素影响芯片良率。业内专家对GAAFET的制造难度作出解释:“晶圆的生产过程中,蚀刻垂直侧壁上的器件最是困难,需要引入更新的半导体材料。”“结构还需要使用EUV进行多次蚀刻,还需要解决可能出现的隐藏缺陷,比如鳍片之间的残留物、Nanosheet损坏或本身相邻的源-漏极区的选择性损坏、沟道释放需要单独控制片材高度、拐角侵蚀和沟道弯曲等。”

为了解决这些问题,芯片制造工艺需要从源头进行改善。例如设计并制造更精密的光刻机,解决光刻功率不够以及光子噪音等问题;更换配套的刻蚀机、离子注入机等相关设备甚至重建厂房;调整产线来适应更多次的刻蚀流程;设计芯片的EDA软件也要相应更新,重新调试仿真技术。

就以 GAA 技术来说,三星曾透露自家3nm GAA的研发成本比5nm FinFET更高,有可能超过5亿美元。2022年1月,英特尔宣布以高达3.4亿美元的价格向ASML预定了仍在设计阶段的High-NA量产型EUV光刻机EXE:5200,用来制造3nm工艺及更先进技术的芯片。台积电也透露3纳米一片12寸晶圆大约2万美元,用的还是FinFET,GAAFET晶圆或将达到3万美元一片。

2nm,意味着什么?

就目前来说,GAAFET由于制造困难极高,成本高昂,各大芯片厂商都没能给出确定量产时间。在未来相当长的一段时间内,应用3nm工艺GAAFET技术将是各大厂商竞争的主要目标。抢占2nm,需要这么着急吗?

过去几年,三星连续为高通代工骁龙888与骁龙8gen1两代芯片,但遭到口诛笔伐,后高通决定放弃三星,将下一代芯片交由台积电代工。几乎是同一时间,英特尔也将GPU 芯片订单交给台积电,理由是三星的良率不佳,产量较低。而三星之所以会失去两大客户的根本原因就在于工艺制程落后。

上文提到,在进入FinFET后,14nm、10nm等数字已经不能代表工艺制程,晶体管密度才能更直观的展示技术先进程度。彼时三星、台积电同为5nm工艺,但两家代工厂的晶体管密度仍有所不同。台积电5nm工艺为1.73亿颗晶体管/平方毫米,而三星的工艺仅达到1.27亿,低了近27%。工艺落后成为三星代工的骁龙变“火龙”的直接原因。

图源:IT之家

对于世界上最先进的代工厂来说,技术落后一代就意味着将失去大部分客户。因此,三星为了改善外界对三星代工的印象,在2022年就开始在3nmGAA领域发力。根据三星公布的数据,与5nm制程相比,3nm制程可以降低45%的功耗、提升23%的性能和缩小16%的芯片面积。对于2nm芯片来说,这些差距还将更明显。所以,全球几乎所有先进代工厂都在全力奋战2nm。

写在最后

相较于过去的工艺制程,2nm芯片的制造需要更加高精度的加工设备和更为复杂的制程工艺,同时,这也意味着芯片制造商需要投入更多的研发成本和生产成本。尽管如此,2nm芯片的研发和生产仍然具有巨大的商业价值。

2nm芯片的研制标志着芯片工艺制程的一次重大突破,同时也意味着摩尔定律逐渐趋于极限。然而,这并不意味着芯片技术的发展将止步不前。相反,技术的发展将会转向更为多元化和综合化的方向,从而进一步推动科技产业的发展和创新。我们有理由相信,在全球技术人员的共同努力下,芯片技术将继续保持高速发展,并为未来的科技进步奠定坚实的基础。

来源: 与非网,作者: 刘浩然,原文链接: https://www.eefocus.com/article/1479057.html

芯耀

芯耀

1908

1908

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)