Drive level 驱动电平

Applying excessive drive level to the crystal units may cause deterioration of characteristics or damage. Circuit design must be such as to maintain a proper drive level.

若对晶体谐振器施加过大的驱动电平,可能会导致其物理特性恶化或损坏。电路设计必须确保为晶体谐振器提供合适范围内的驱动电平。针对每一款晶体谐振器Drive level (驱动电平)的大小,晶科鑫的晶体谐振器规格书都有清晰注明。

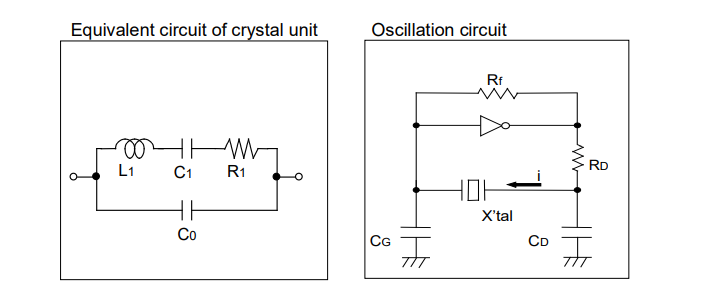

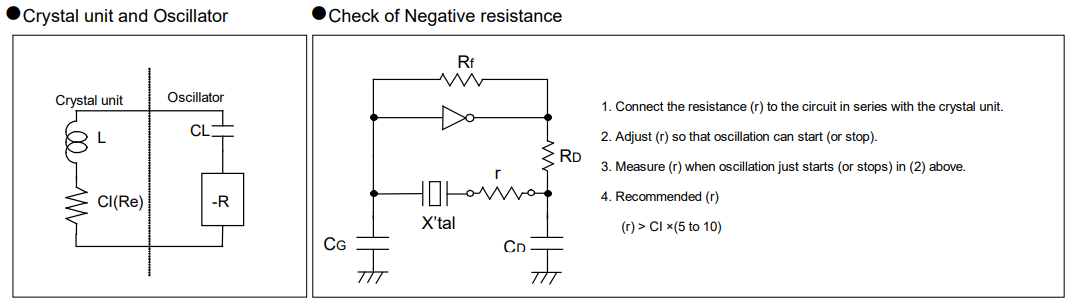

Negative resistance 负性阻抗

Unless adequate negative resistance is allocated in the oscillation circuit, oscillation start up time may increase or no oscillation may occur. In order to avoid this, provide enough negative resistance in the circuitry design.

在振荡电路中如果分配的负性阻抗不够,晶体谐振器振荡的启动时间可能会延长或无振荡频率产生。请在电路设计时,提供足够负性阻抗,以确保晶体谐振器正常起振。

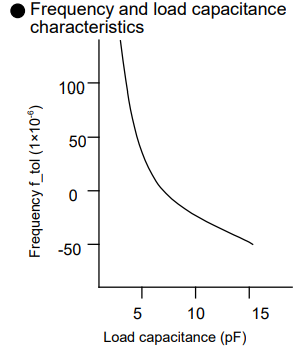

Load capacitance 负载电容

Differences in the load capacitance in the oscillation circuit may result in deviations in the oscillation frequency from the desired frequency. Attempting to tune by force may merely cause abnormal oscillation. Before use, please specify the load capacitance of the oscillation circuit.

振荡电路中负载电容的差异可能导致振荡频率与期望频率产生偏差。若通过强制调谐,可能会导致晶体振荡器振荡异常。在晶体谐振器使用之前,请务必确认振荡电路的负载电容。

芯耀

芯耀

425

425