回顾即将过去的三月,尽管本月是许多股票上市的半导体公司发布2022年年报的月份,也是很多全球重要半导体行业活动开始登场的月份,但是半导体领域内最值得关注的既不是某家公司的年报,也不是某家公司发起的大型收购。业界谈论最多的还是诸如ChatGPT这样的多模态大模型人工智能技术对半导体行业带来的机会,以及摩尔定律的提出者戈登·摩尔先生辞世引发的对行业发展规律的进一步探索。

2023年3月24日,摩尔定律的提出者、仙童半导体公司(Fairchild Semiconductor)和英特尔(Intel)的联合创始人、戈登和贝蒂·摩尔基金会的联合发起人戈登·摩尔(Gordon Moore)去世,享年94岁。摩尔先生对半导体产业的贡献给我们的工作和生活带来了巨大的影响,仙童半导体点燃了硅谷之火,英特尔则是今天数字世界的一个重要推动者;摩尔先生也致力于慈善事业,特别关注环境保护、科学探索和患者护理改善,他与妻子一起成立的戈登和贝蒂·摩尔基金会共向慈善事业捐赠了超过51亿美元。

戈登·摩尔(图片来源于英特尔官网)

摩尔在1965年提出的摩尔定律(Moore’s Law)准确地预测了半导体行业的发展,他在最初提出时预测集成电路中的晶体管数量将每年增加一倍,在1975年他又将其修正为每两年增加一倍。尽管对摩尔定律会在什么时候失效的讨论从未停止过,但是这项预测不断被半导体行业中的创新印证。摩尔定律在成为半导体行业发展的“集体路线图”的同时,也在过去数十年中启发和激励了半导体行业的从业人员充满激情并不断地去创新,用更多更先进的半导体技术为人类带来福祉。

摩尔定律的扩展与更多的争论

戈登·摩尔的产业洞察力还激发了更多行业人士对科技产业发展规律的探索,针对半导体产业的发展趋势,不仅提出了“More Moore”和”More than Moore”这样的趋势,而且还有更多新的定律在不断被提出。全球领先的RISC-V处理器IP和定制处理器EDA工具提供商Codasip的首席营销官Rupert Baines曾经撰文:除了摩尔定律,登纳德缩减定律(Dennard Scaling)和阿姆达尔定律(Amdahl’s Law)也很好地描述产业发展路径。

Codasip首席营销官Rupert Baines

这些定律揭示了晶体管的大小不断按比例缩减给半导体行业带来的机遇:登纳德缩减定律指出,随着硅芯片上晶体管几何尺寸的缩减,电源电压也会降低,这将使得从一代硅芯片到下一代硅芯片的单位面积功耗保持不变并带来两个好处,其一是新一代芯片的功耗与上一代芯片大致相同,其二是可以通过增加时钟频率来提高性能。此外,阿姆达尔定律指出可以通过使用并行处理器来处理潜在的执行加速问题,即在给定的硅芯片尺寸下,添加额外的并行处理器将增加更多的性能。

Codasip的Rupert认为摩尔定律、登纳德缩减定律和阿姆达尔定律正面临诸多挑战,这是因为半导体产业也要符合技术经济学规律。比如,对于90nm及以下的工艺,漏电流(leakage current)在芯片设计中就变得非常重要,这种硅材料的特质使晶体管几何尺寸的继续缩减并不能继续降低功率密度。这时如果时钟频率太高,就会存在芯片热失控的风险;这意味着时钟频率有一个实际的上限,很少有设计能达到2 GHz以上。

ChatGPT也需要越来越丰富的终末端场景

另外一个促使行业偏离这些定律的驱动力是芯片应用场景的多元化,物联网、嵌入式计算、边缘计算、智能汽车和其他各种智能化应用中的处理器不仅无法像PC/服务器的CPU和手机/平板电脑里的AP一样靠巨大的批量来摊销先进工艺制程的成本,同时还需要针对应用来进行定制化、实现异构计算和多种工艺集成。这些终末端计算和智能在未来极为重要,ChatGPT最终也要通过这些端侧设备来走入我们的工作和生活。

所以,嵌入式计算带来了更加灵活的Arm架构的兴起,以及比Arm架构更加透明、从而更便于定制的RISC-V架构的更快速成长。在去年,采用RISC-V架构的芯片的出货量超过了100亿颗,其中一直走定制处理器路线的Codasip就支持其客户贡献了20亿颗。Codasip的客户开发的RISC-V处理器被成功地应用在存储、工业和医疗等垂直市场。

还有一个非常显著的案例就是5G NR小基站芯片,PC802是比科奇(Picocom)在全球开发的第一颗小基站基带处理(PHY)系统级芯片(SoC),它与采用先进工艺的处理器+FPGA的基站架构相比,大幅降低了功耗(运营商可以大幅度节省电费),并在主芯片上具有更高的经济性,还给下游小基站开发商带来更大的灵活性。目前,全球已有数十家企业采用比科奇的PC802来开发5G/4G小基站,其中中科微、东方国信、几维通信和易科奇等企业的小基站产品已经通过了运营商的测试。

比科奇PC802小基站基带SoC

所以,尽管物联网和嵌入式计算也在不断采用新的工艺节点,但并不再过度追求最先进的工艺,而且也无法充分利用最先进节点的工艺,因为例如无线SoC中的射频部分或者MCU中越来越多的混合信号部分并不能用先进工艺来缩小芯片面积。基于合适架构的算力+应用相关的特性成为了行业发展的模式,这些应用相关的特性,如安全性、功能安全性、可靠性、新的加速器和通信技术等正在成为市场竞争的关键。

来自嵌入式世界一线的观感

今年三月,在德国纽伦堡市举办的“嵌入式世界(Embedded World)”展览上,许多行业领先公司的新产品发布正在印证这样的趋势,即针对应用和生态进行创新。例如:

全球领先的芯片、软件和解决方案提供商Silicon Labs展示了其业界最全面的无线产品组合和参考设计,包括蓝牙高精度距离测量(HADM)、带有加速器的机器学习(ML)、Matter以及亚马逊Sidewalk等,用智能无线技术满足物联网未来应用需求。同时还发布了超小型的xG27系列蓝牙SoC和BB50微控制器,它们可以支持微型、电池优化设备,例如互联医疗设备、可穿戴设备、资产监控标签、智能传感器,以及牙刷和玩具等简便的消费电子产品等。

Codasip和全球领先的嵌入式开发工具提供商IAR在Embedded World展会上,共同宣布了将强强联手为低功耗嵌入式汽车应用提供全新的创新支持,双方将联手为客户提供屡获殊荣的Codasip L31内核和获得安全性认证的最新版本IAR Embedded Workbench for RISC-V开发工具链。

此次合作推出的Codasip的双内核锁步参考设计可为汽车应用开发人员提供一条便捷之道,以帮助他们推出基于多功能的Codasip L31内核且符合ISO 26262认证标准的嵌入式应用;IAR Embedded Workbench for RISC-V的功能安全版本已通过了TÜV SÜD的认证,符合10个不同标准的要求,其中也包括ISO 26262功能安全标准。

越来越强大的嵌入式计算和边缘计算世界

尽管嵌入式计算、边缘计算乃至部分采用先进工艺的异构计算并没有按照摩尔定律来做芯片的集成,但是目前也不妨碍它们在特定的应用市场和生态中变得更加强大。如我们前面所分析,根据其各自应用的要求,这些芯片通过引入安全性、功能安全性、硬件加速器以及其他措施来提高可靠性和性能。国内中国芯企业在相关领域内也已取得了巨大的进展,例如泰斗微电子推出的北斗/GPS双模卫星导航SoC芯片通过了极为严格的AEC-Q100 Grade 2车规认证,兆易创新采用IAR合规开发工具的MCU产品获得车规认证等等。

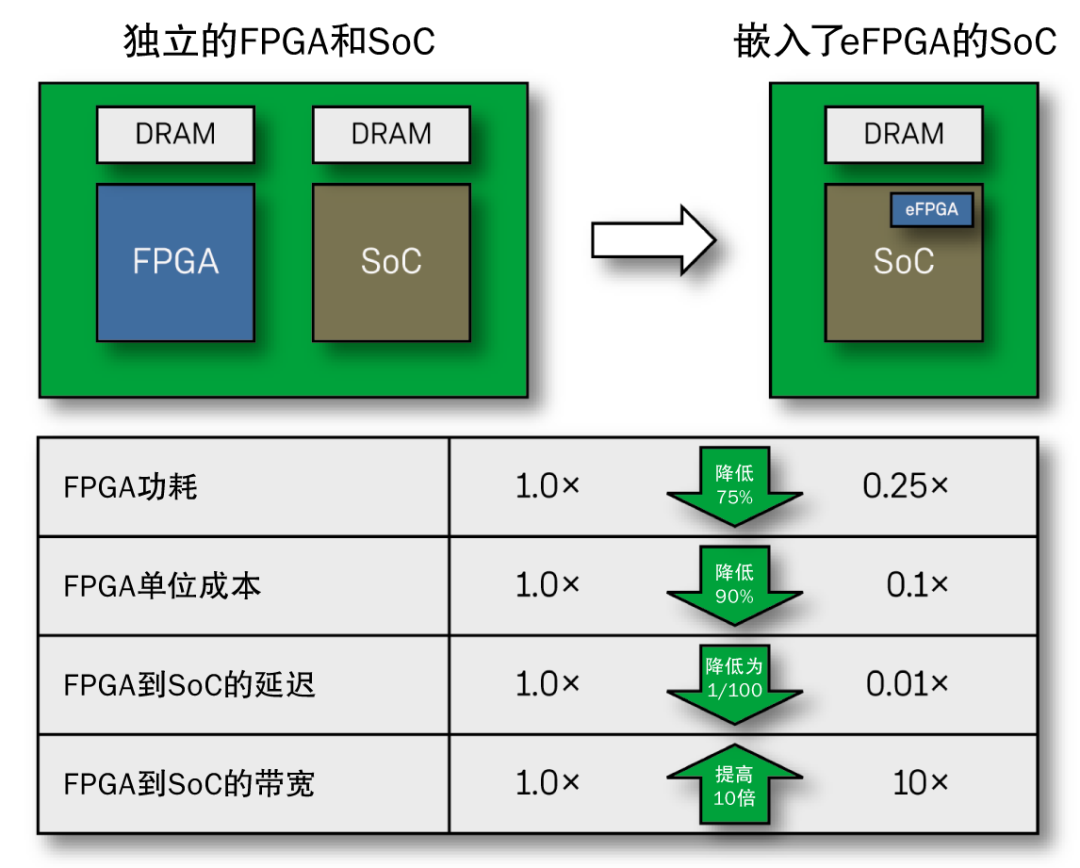

在计算性能方面,越来越多的嵌入式和边缘计算芯片平台通过引入诸如嵌入式FPGA(eFPGA) IP等产品,可以提供人工智能推理等更高的性能。根据全球最大的独立FPGA芯片和eFPGA IP提供商Achronix提供的数据,该公司Speedcore eFPGA IP在去年年中出货量超过了1500万。全球数十家顶级科技企业正在应用这种eFPGA来打造自己的芯片,用于网络加速、智能汽车、通信基础设施和金融科技等应用。

Speedcore eFPGA可以最小化芯片面积,提高性能,降低功耗,减少成本并且令SoC设计历久弥新

安全也是另一个非常重要的话题,也是一个具有广阔前景的市场。根据在香港上市的中国电子华大科技有限公司(00085.HK)发布的2022年业绩报告,该公司旗下的国内首家自主集成电路设计企业北京中电华大电子的安全芯片得到广泛的应用,该公司的净利润比2021年增长了325%达5.31亿港元。该公司表示:随着5G网络应用的推广对信息安全需求有所增加,使本集团在智能网联车及物联网安全芯片应用市场的推广上取得较好效果。年内eSIM芯片、智能网联车安全芯片及高端SIM芯片市场需求大幅增加,销售量较去年大幅增长。

结语

作者单位北京华兴万邦管理咨询有限公司十几年来为国内外很多处理器芯片设计公司提供了中国市场服务,包括全球第一家Arm Server Chip开发商、全球最高集成度的DSP cluster开发商,CPU、GPU、RISC-V芯片和IP,FPGA芯片和IP,各种无线SoC、各种AI加速器...... 但是并不是每一家企业都取得了巨大的成功,原因是一些企业都把技术开发放在比生态建设更优先的位置上。其实这两个方面都同样重要,对嵌入式计算、边缘计算和异构计算尤其如此。

芯耀

芯耀

1062

1062

-1-%E5%89%AF%E6%9C%AC.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍