在芯片的研发中,风险主要来自芯片的正确性代价成本。如何在流片前及时、彻底地发现设计中潜藏的逻辑错误,保证芯片的可用性、高效性、始终是业内着力解决的问题。因此验证在芯片设计与实现中是非常重要的一环,这些复杂芯片的开发都需要进行更全面的测试验证。在数字电路设计的早期,设计和验证团队往往会选择软件仿真、硬件仿真及原型验证作为常规验证工具。

业内人士通常将硬件仿真作为调试的大杀器,尤其在面对SoC中硬件和软件的交互。硬件仿真有着比软仿更高的运算能力再加上全可视的特点, 能够更有效地发现缺陷并提供调试和修正手段,解决嵌入式硬件和软件底层边界之间的疑难杂症。

因为硬件仿真往往具有以下特点:

- 设计容量大,可扩展性好

- 仿真速度快

- 调试能力强,调试模式多样

- 适合大型设计从模块级、芯片级到系统级的仿真验证

由于大数据处理及AI芯片设计规模的持续扩大,以及市场激烈竞争下的快速迭代需求,越来越多的芯片设计公司考虑选择硬件仿真系统,来提高芯片验证效率,缩短芯片开发周期。而硬件仿真成为平台化中心的特点也越来越明显。

企业级硬件仿真系统新突破

伴随各种设计验证方法学的不断推陈出新,各种硬件仿真系统也层出不穷。在硬件仿真的选择中,通常会考核很多功能,硬件仿真系统的执行速度,硬件可靠性,是否有更大的设计容量,及多用户资源等,都是芯片设计公司选择时会考虑的多重因素。另外,还会考虑是否有其他新特性,来不断提高这种验证技术的投资回报率。 例如:

- 如何快速搭建验证环境,在极短时间内完成用户设计的移植和部署

- 如何快速发现和定位深层次的隐藏问题

- 如何快速设计足够验证case,满足不同应用场景的验证需求

- 如何在短时间完成对大规模设计的充分验证

针对复杂芯片规模的验证痛点,业界普遍认为先进的企业级硬件仿真系统还应有更大的突破,例如:

- 需要操作便捷,系统自动化程度高,支持用户设计的全自动编译,无需对设计过多干预,Gigabyte级别的设计网表能快速编译并快速完成后端工作

- 需要具有强大的调试能力,支持足够灵活的调试手段,可以捕捉源代码的深度错误和性能瓶颈。在实现高速运转速度的同时保证信号全部可探测(信号全可视),支持灵活的实时触发、海量的波形数据存储和分析

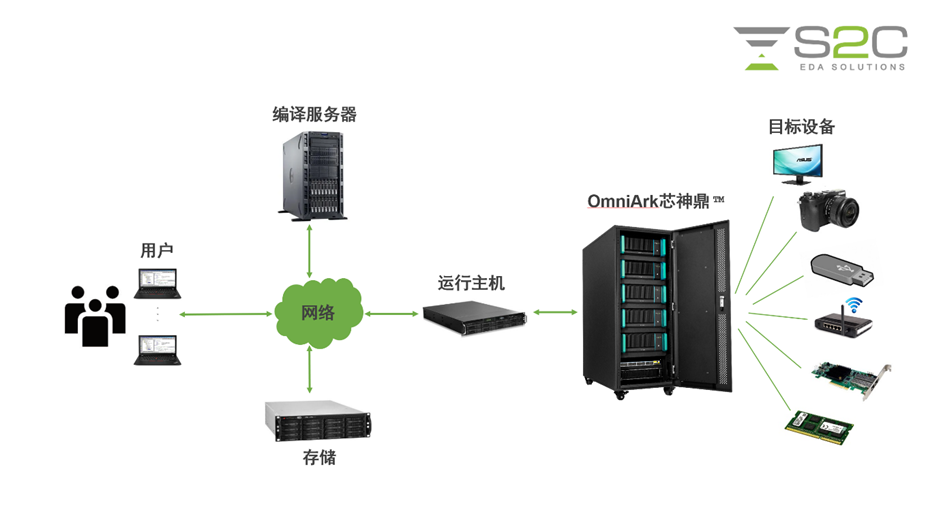

为了满足日益复杂的芯片设计,以及日益旺盛的国产化需求,思尔芯全新推出 「OmniArk 芯神鼎」企业级硬件仿真系统。该产品为思尔芯自主研发,拥有多项自主知识产权的核心技术,实现了对超大规模设计的全自动编译。目前已在多个芯片设计企业推广使用。帮助汽车电子、CPU、AI、5G、云计算等SoC设计所需的复杂验证。

产品采用超大规模商用可扩展阵列架构设计,机箱模块结构,方便维护和扩展。产品形态从桌面型到机柜型,设计容量可扩展至20亿门。包含一套便捷易用的软件系统,支持GUI图形界面和TCL脚本命令,集成编译、运行、调试的完整流程。

OmniArk 芯神鼎重要特性

“工欲善其事,必先利其器”, OmniArk 芯神鼎在提供硬件加速平台的同时也提供各种功能的创新配套软件:用户设计语法自动纠错、Smart P&R技术,ABS(Auto-Block Select)技术, 多样化信号采集手段等等,让用户实现MHz级仿真加速、全自动智能编译流程、强大调试能力,以及多种仿真验证模式。更拥有丰富的VIP库,适合超大规模高端通用芯片设计的系统级验证,可以满足不同验证场景需求。

重要特性:

1、设计快速移植和部署

- 支持Verilog,SystemVerilog等常用开发语言

- 用户设计语法自动纠错

- 自动化的门控时钟、三态、多驱等处理

2、全自动智能编译流程

- 多线程(进程)并行综合;

- 超大规模的用户内存自动建模映射

- 多时钟域时序分析,运行频率估算

- Smart P&R技术,帮助参数智能优化

- 增量编译,减少编译时间

选择高性能的软件开发工具往往能够大大提高硬件仿真的验证效率。OmniArk芯神鼎整个编译流程皆为全自动,较少需要用户干预,通过多种核心技术,就能实现快速编译与自由设计。

3、MHz级仿真加速

- 时序驱动的分割和路由算法:兼顾最小切割和关键路径延时

- 时序驱动的TDM和引脚分配:关键路径采用更小的Ratio比

- 系统级时序建模及时序分析:准确估算最大运行频率、为时序驱动算法提供反馈

- ABS(Auto-Block Select)技术:解决超大规模设计的性能挑战

对硬件仿真工具的性能影响最大的是基本元件之间的连接延迟,因此分割(Partitioning)对仿真速度的影响最大。以一个10亿门的超大规模电路设计为例,如果将其在专用的硬件仿真平台上,就会涉及到的芯片间切割、布线、时序分析等一系列复杂问题。传统的分割器只优化切割数(Sum of External Degrees),所以不能有效的优化时序(Timing),因此应用时序驱动的分割器来提高硬件仿真性能。OmniArk芯神鼎采用4大技术创新,其中通过时序驱动的分割和路由算法,兼顾最小切割和关键路径延时,可实现高达数MHz的仿真速度,从而提高硬件仿真性能。

4、强大的调试纠错能力

芯神鼎有着多样化信号采集手段,比如:静态探针,动态探针,信号全可视(IO/Register/Logic/Memory),更有灵活设置信号触发方式,支持对任意信号的波形实时抓取。此外还支持存储器后门读写,可以为固件的装载和调试提供便利;支持Force/Release/Deposit,方便进行故障注入测试;并且内置了波形查看工具,并支持波形与RTL代码反标,方便在RTL源码级调试,使得整个调试纠错能力更高效。

5、多种仿真验证模式

芯神鼎拥有多种的仿真验证模式,如TBA、ICE、QEMU等模式,满足多种验证场景的需求。

6、丰富的VIP库

芯神鼎拥有丰富的VIP库,支持常见高性能接口的速度适配,如AHB、AXI、PCIe、DDR、Ethernet、USB等,可以满足不同验证场景需求。

OmniArk 芯神鼎应用案例

电子科技大学(成电)和西安电子科技大学在使用了 OmniArk 芯神鼎后,表达了对产品的高度认可。

西安电子科技大学微电子学院教授游海龙表示:“西电在采购建设世界先进 EDA 工具的同时,支持国产最新 EDA 研发成果。2022 年,我们采购了国产自主研发的 OmniArk 芯神鼎,并在我校集成电路设计教学与科研中发挥了重要作用。在面向先进集成电路设计研发验证中,基于 OmniArk 芯神鼎上实现了快速移植和部署,提前计划完成了工程搭建,无需对硬件环境进行手工连线。整个全自动的智能编译流程能够大大提高我们的验证效率,调试能力强大且灵活,用户界面操作友好且易用,帮助我们在超大规模 SoC 设计中系统级功能验证的实现。同时 OmniArk 芯神鼎的高性能和易操作也支持着我们的课堂教学,实践教学,课程设计等教学活动, 使教学效果出现了非常大的改观。”

OmniArk 芯神鼎是西电首台购买并应用于教学的硬件仿真工具,也是基于国产自主的突破性 EDA 工具,使得相关成果能在国内高校得到应用,为西电集成电路设计方面人才培养提供了有利条件。

游教授进一步表示:“依托西电产教融合创新平台,我们将为 OmniArk 芯神鼎在国内开展实训。并与思尔芯围绕集成电路验证领域,进一步紧密合作,依托硬件平台合作共建教材、课程,为我国建设培养更多掌握先进设计方法学以及国产自主工具的高层次人才。”

结合其他产品线打造全流程

OmniArk 芯神鼎是真正的国产企业级硬件仿真系统,对标三巨头,实现信号全可视的产品。

思尔芯自 2004 年成立以来一直专注于 EDA 领域的深耕发展。近 20 年雄厚的技术积累,使得产品成熟、稳定,表现也更为出色,多年来深受市场的肯定。尤其是在中国 IC 设计公司数量越来越多的大环境下,还能够做到充分贴近本地客户服务,最终获得越来越多的客户认可和信任。

基于思尔芯能够深入挖掘客户痛点,不断快速响应的服务特点,得到了600+的海内外客户背书。此次新产品的开发就是为了响应庞大而丰富的客户群体需求,打造了国产化、自动化、高性能、真正全可视的调试环境,帮助客户完成验证场景,提高整个芯片开发效率,加速产品上市周期。

思尔芯目前已完善了整个芯片设计的功能验证布局,提供了成熟商用的架构设计软件、高性能多语言混合的数字软件仿真工具、企业级国产硬件仿真系统、多组合方案的原型验证解决方案等。

未来,思尔芯还将结合其他产品线,通过独立的硬件仿真配上帮助与软件仿真、原型验证协同仿真的软件,一样可以实现软硬件协同仿真的完美运行。以先进的异构验证方法学进行 SoC 设计,打造出真正的国产数字 EDA 全流程。

关于思尔芯S2C

思尔芯(S2C)自2004年设立上海总部以来始终专注于集成电路EDA领域。作为业内知名的 EDA 解决方案专家,公司业务聚焦于数字芯片的前端验证,已覆盖验证云服务、架构设计、软件仿真、硬件仿真、原型验证等工具。已与超过600家国内外企业建立了良好的合作关系,服务于人工智能、超级计算、图像处理、数据存储、信号处理等数字电路设计功能的实现,广泛应用于物联网、云计算、5G通信、智慧医疗、汽车电子等终端领域。

公司总部位于上海,并建立了全球化的技术研发与市场服务网络,在北京、深圳、西安、香港、东京、首尔及圣何塞等地均设有分支机构或办事处。

思尔芯在EDA领域的技术实力受到了业界的广泛认可,通过多年耕耘,已在原型验证领域构筑了技术与市场的双优势地位。并参与了我国EDA团体标准的制定,承担了多项国家及地方重大科研项目。

2674

2674