现在英特尔和 AMD 都推出了新的服务器平台,业界坚定地走上了向 DDR5 过渡的道路。我们已经稍微讨论了速度的提高,但这一代发生了更多变化。例如,现在芯片上有两个内存通道。此外,即使您拥有 ECC DDR5 UDIMM,它也不再与支持 RDIMM 的平台兼容。是时候深入探讨一下 DDR5 内存为何与众不同。

为什么 DDR5 在现代服务器中绝对必要:核心数量增长

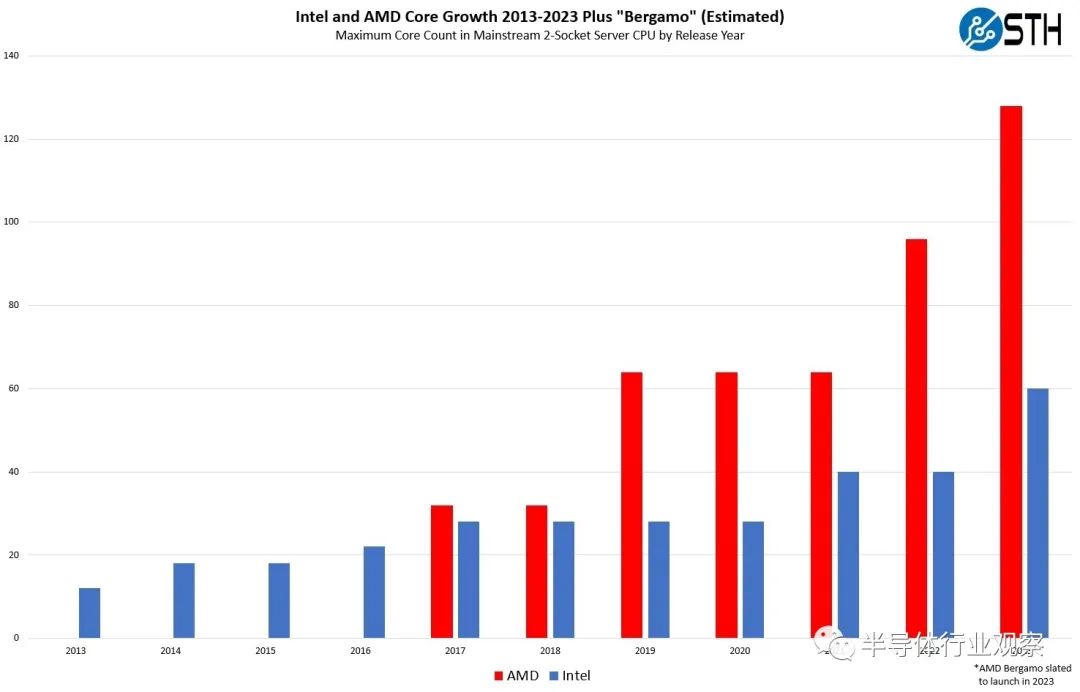

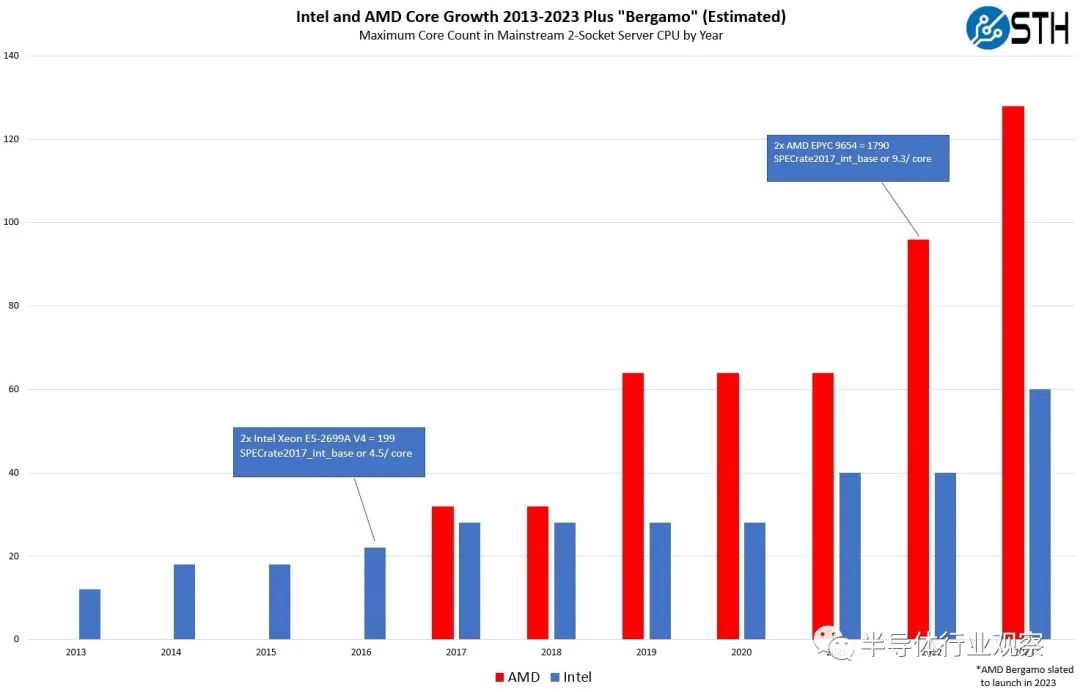

这在过去的十年中,服务器市场已经从 12 核/插槽发展到目前的 96 核/插槽,在我们市场上已有的相同平台上,128 核/插槽的速度相对较快。

过去十年,英特尔和 AMD 主流服务器核心数量增长

显而易见的是,服务器正在将过去位于机架中的内容整合到单个节点中。随着小芯片和 CXL 的出现,这种趋势在未来将会加速。系统扩展的最大挑战之一是内存带宽。拥有更多内核和更多 PCIe 设备固然很好,但如果系统的某些部分闲置等待数据,那么它们就被浪费了。

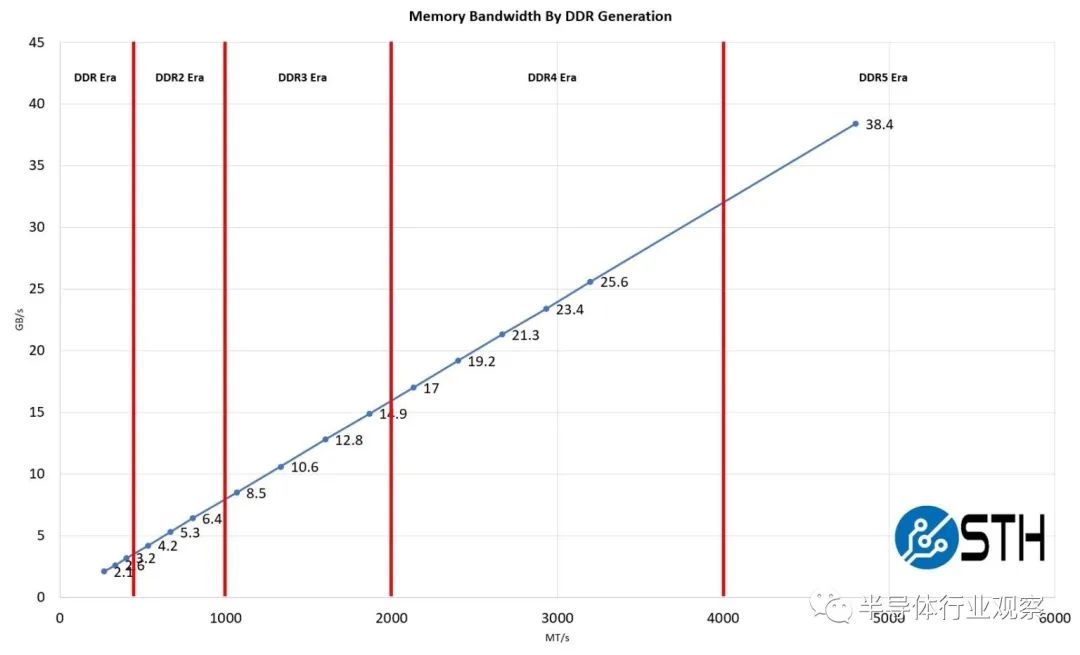

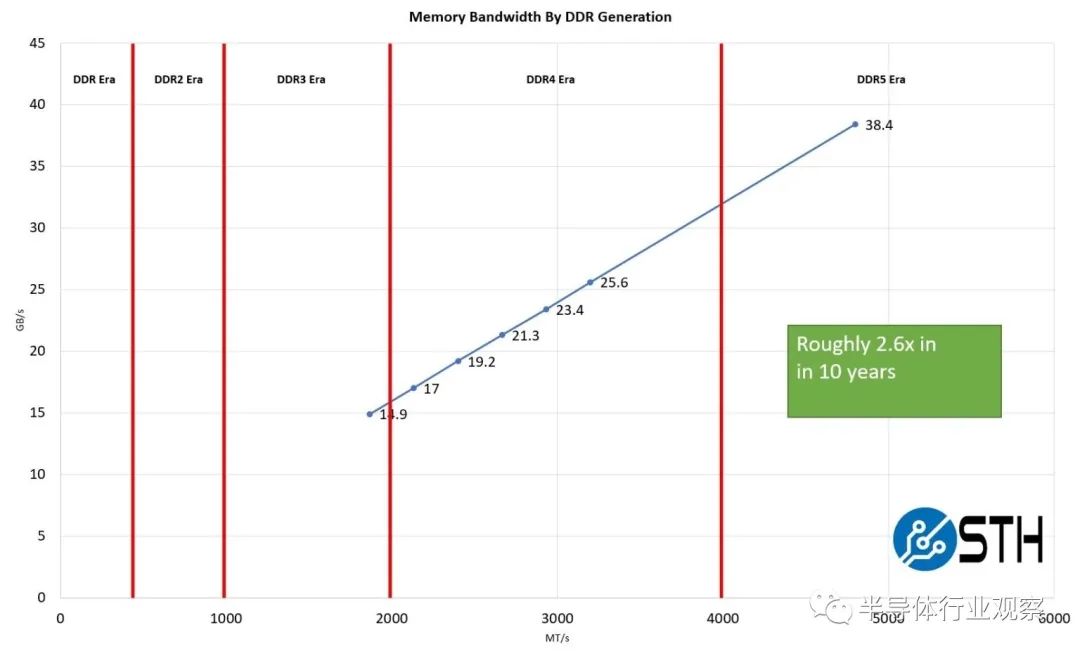

第 1 代 DDR DDR2 DDR3 DDR4 和 DDR5 内存带宽

从 DDR4-3200 到 DDR5-4800 的跳跃是巨大的。

由于内存扩展速度慢于核心增长速度,服务器供应商设计了一个简单的解决方案,扩展内存通道数量并使用更快的内存。

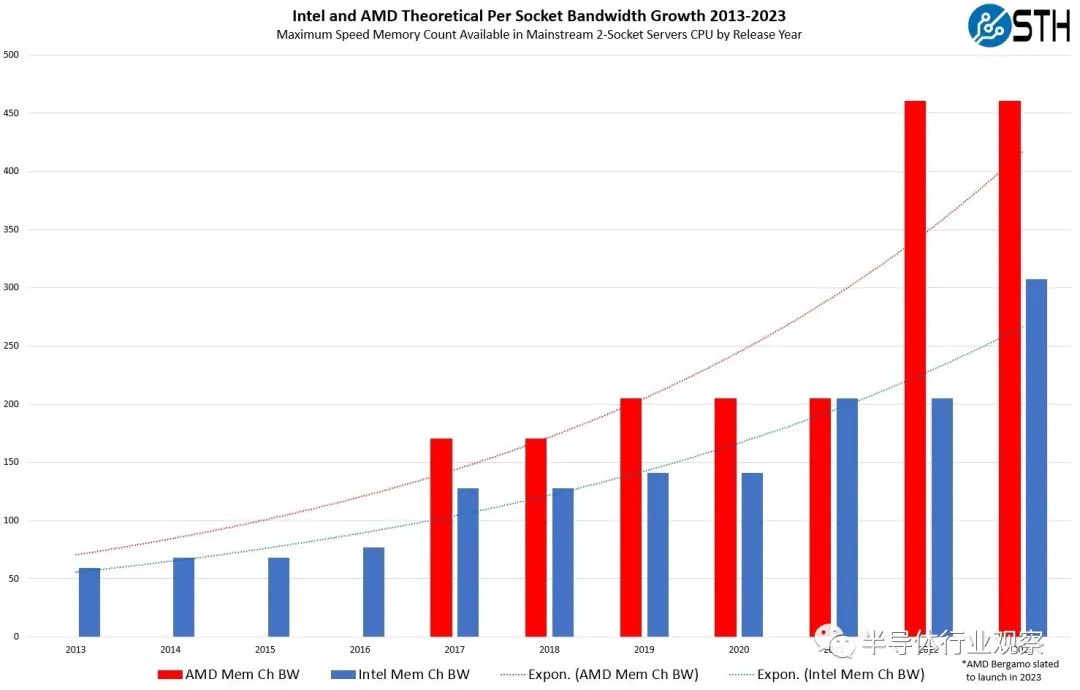

Intel 和 AMD 主流服务器过去十年的理论带宽增长

增加内存通道,同时提高内存速度意味着随着时间的推移,该行业至少能够为内核提供类似数量的带宽。请注意,我们在这里使用的是最大内核数,但如果保持内核数竞争,例如 32 个内核,则每个内核的内存带宽会增加。

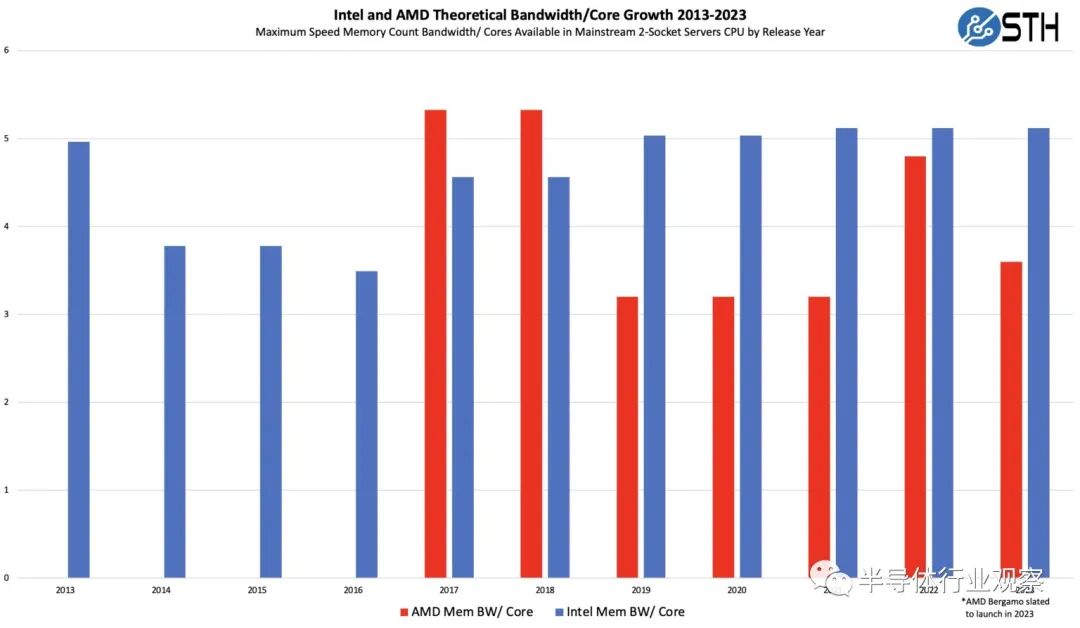

Intel 和 AMD 过去十年每核 2P 服务器每核最大内存带宽

有了这个,很多人想知道为什么人们谈论系统内存带宽受限。等式还有另一面:每个内核的性能。在过去十年中,高核心数 SKU 的每核心性能大约提高了 2-3 倍。AMD EPYC Bergamo,我们预计在 Zen 3 Milan 内核的性能比完整的 Zen 4 Genoa 内核更好,但话又说回来,Bergamo 的内核多了 33%。

英特尔和 AMD 主流服务器过去十年的核心数量增长与 SPEC 标注

在这种背景下,内存带宽方面在过去 10 年中仅扩展了 2.6 倍,现在我们有了 DDR5。如果不是 DDR5,那将不到一倍。

从DDR3 1866 到 DDR5 4800的内存带宽增长

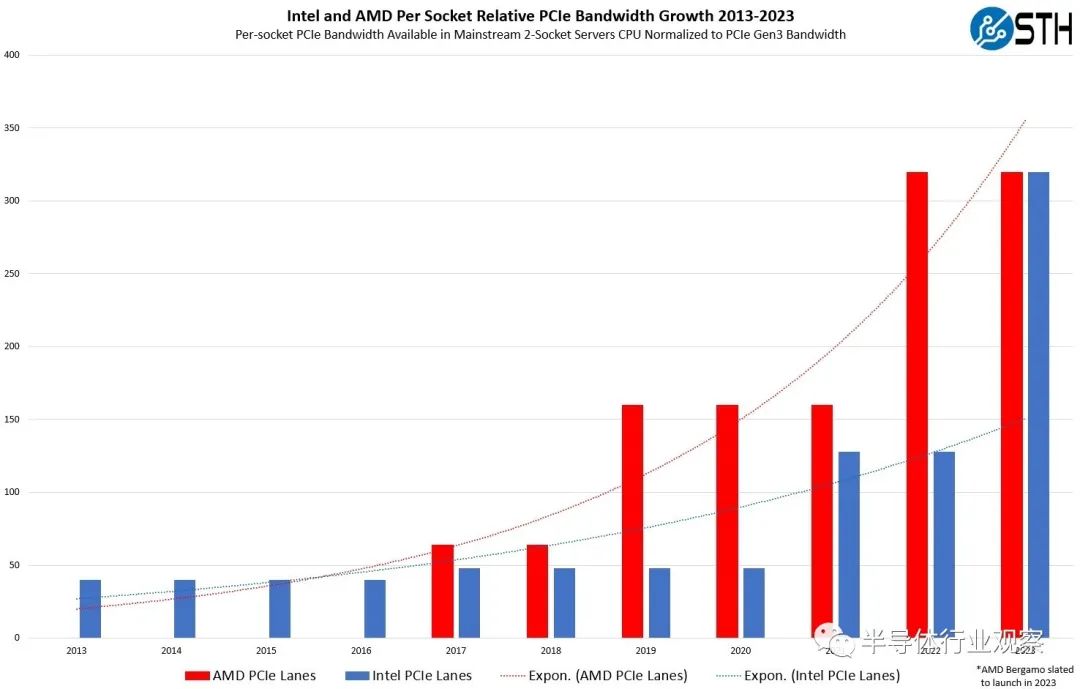

在系统层面,我们还展示了Intel Xeon 和 AMD EPYC 十年来的 PCIe 通道和带宽增长。

英特尔和 AMD PCIe 通道每插槽吞吐量增长过去十年的增长

高速 RDMA NIC 等 PCIe 设备对内存子系统施加的压力超出了内核单独执行的范围。同样,英特尔的 Sapphire Rapdis Xeon 板载 QAT 加速器以及其他加速器,速度高达 800Gbps。这些加速器可以访问内存,因此可以对内存子系统施加压力。我们甚至看到像 DPU 这样的加速器使用多个 DDR5 通道。

Marvell 的Octeon 10

因此,虽然每个内核的内存带宽作为一个指标似乎已经通过增加内存通道和迁移到 DDR5 来满足,但每个内核的性能提高正在对内存子系统造成压力。

可以肯定的是,具有八个 DDR4-3200 通道的现代 CPU 将非常具有挑战性。因此,这似乎是一个很好的机会来解释更多关于 DDR5 过渡以及 DDR5 内存的不同之处。

接下来,让我们在查看 DDR5 UDIMM 和 DDR5 RDIMM 之间的模块差异时,了解为什么服务器不再支持无缓冲 ECC 内存。

1.1V、5V、12V 以及为什么服务器不再支持无缓冲 ECC 内存?

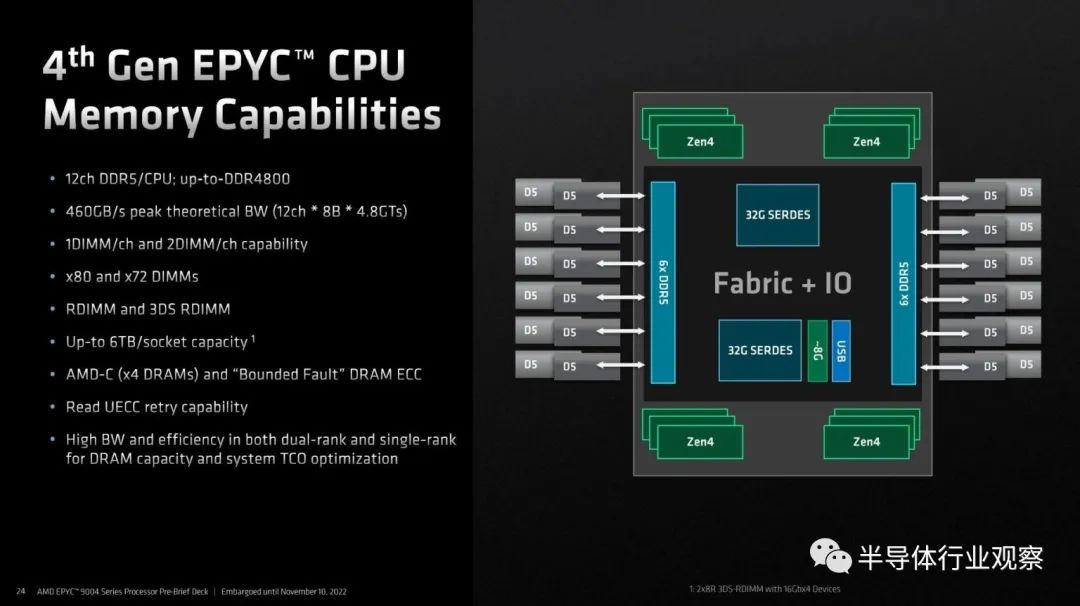

这是许多人仍然不知道的。在 DDR3 和 DDR4 代中,通常可以在服务器中使用无缓冲 ECC(通常是非 ECC)内存或 RDIMM。到现在已不再是这样了。为此,让我们看一下 AMD EPYC 9004 Genoa 内存功能幻灯片:

AMD EPYC 9004 Genoa DDR5 内存功能

在这里我们会注意到,仅列出支持的两种类型的内存是 RDIMM 和 3DS RDIMM。不支持 UDIMM。快速说明一下,这张幻灯片中提到了 x72 DIMM。这些将用于一些非常具体的客户,而不是我们大多数读者会放入系统中的通用模块,因此我们不打算在本文中介绍它们。

就英特尔而言,它在仅支持 RDIMM 而非 UDIMM 方面与 AMD 持相同观点。

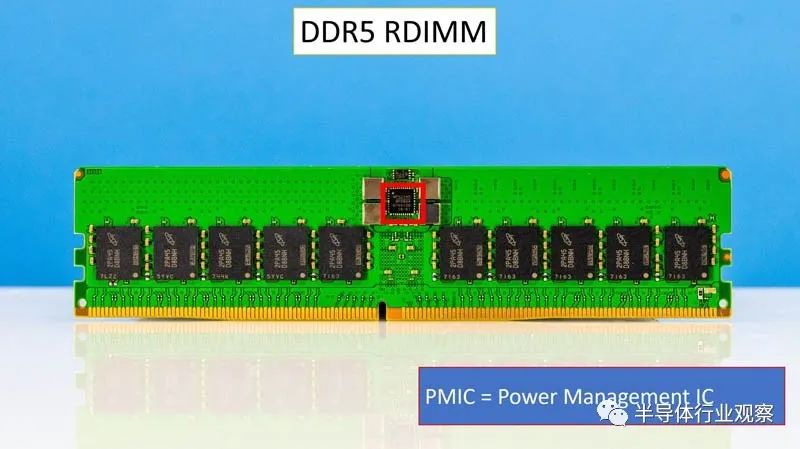

这样做的关键原因是供电组件现在位于 DIMM 本身上。在服务器中,提供 12V 电源。在客户端系统中,只有 5V。这被转换为 1.1V 用于 DIMM 并由板载电源管理 IC 或 PMIC 管理。PMIC 将主板功能移至 DIMM,但这意味着我们在模块上增加了一个组件。

必须对电源子系统进行许多更改才能处理 DDR5 旨在实现的更高时钟速度。人们可以看到模块的物理键控现在有所不同,以防止将错误的模块插入系统。在 DDR4 一代中,可以在支持 RDIMM 的服务器中使用 UDIMM,但DDR5 不再如此。

一个 DIMM 两个通道

也许 DDR5 一代最大的变化之一是通道架构。DDR4 DIMM 具有 72 位总线。该总线可能被称为 64+8,这意味着有 64 个数据位加上 8 个 ECC 位。

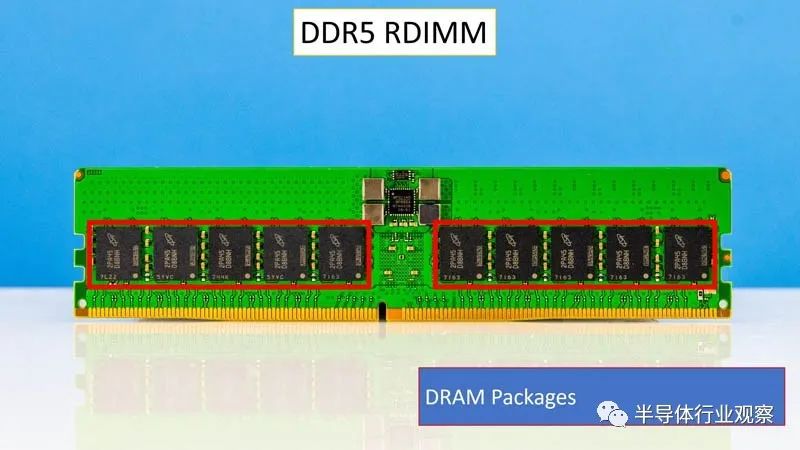

使用 DDR5,现在有两个通道,总共 80 位。每个通道是该通道的一半或 40 位,其中 32 位用于数据,8 位用于 ECC。通道在 DDR5 DIMM 上是分开的,一左一右。

为了更好地利用这一点,新的 DDR5 DIMM 具有更长的突发长度 16。这允许每个通道访问 CPU 缓存行的 64 字节信息,并且独立执行。反过来,这增加了内存子系统的并行性,每个 DIMM 在两个通道上运行,而不是一个。

接下来,我们将看看 DDR5 RDIMM 上的芯片,以及这一代的不同之处。

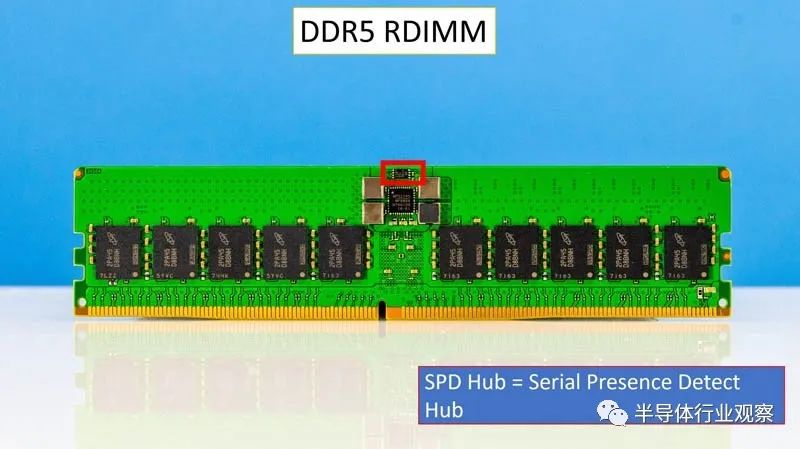

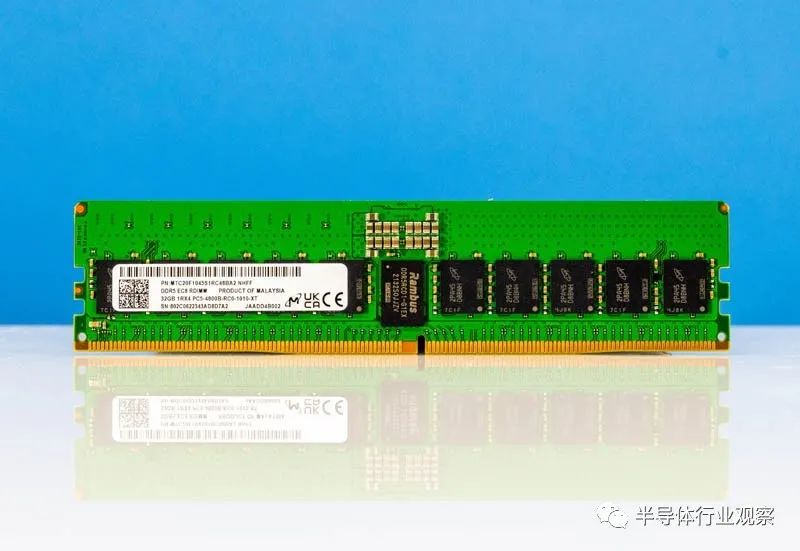

DDR5 DIMM 上的大芯片是什么?

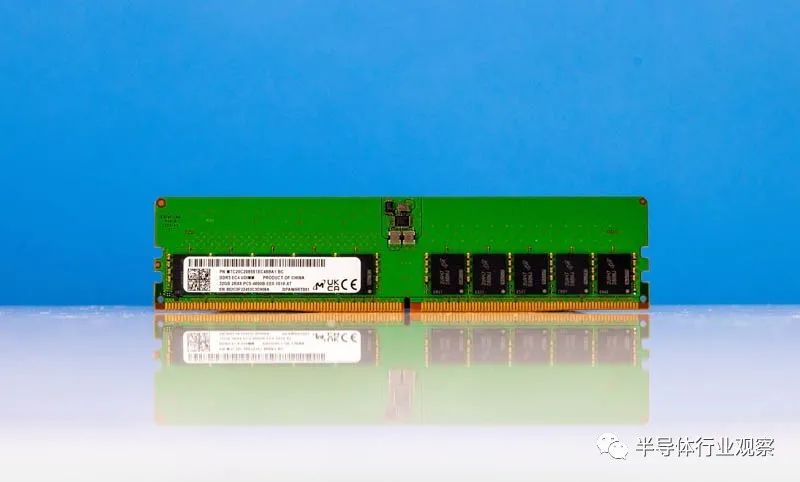

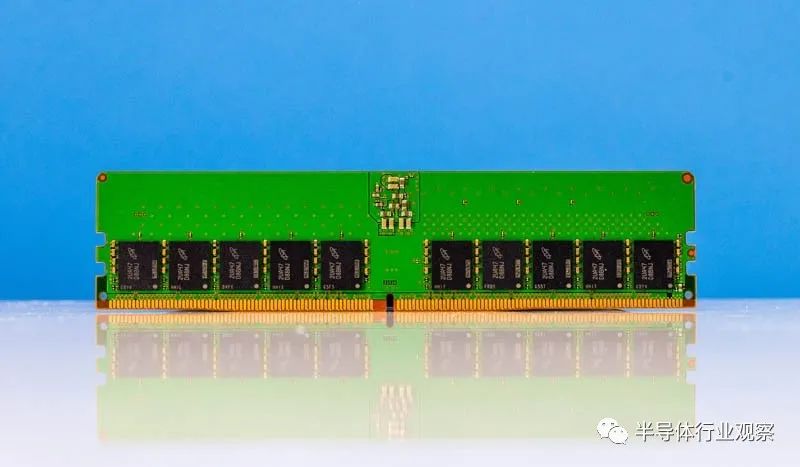

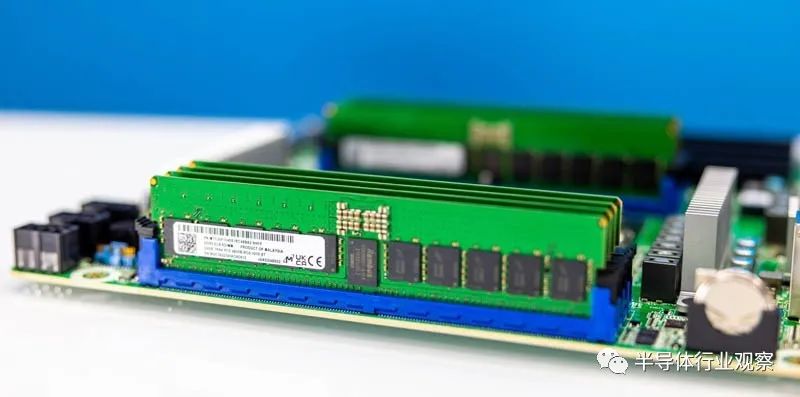

也许最重要的特性是 DRAM 本身。在 ECC DIMM 上,我们展示了 RDIMM 和 ECC UDIMM,两侧各有五个芯片:

在类似的消费类非 ECC UDIMM 上,这里可能只看到四个而不是五个。这些 DRAM 封装为模块提供内存容量,但它们并不是唯一的组件。

在两侧的新 DDR5 DIMM 中间。在一侧,您会找到 RCD 或寄存器时钟驱动程序。它负责为内存模块上的不同芯片提供时钟分配。

这在 DDR5 DIMM 的 UDIMM 版本上不存在:

常见的 ECC 和非 ECC SODIMM 外形规格也没有 RCD。

另一方面,您可能会看到 PMIC 或电源管理 IC。它负责管理设备上的电源。

DDR5 RDIMM 上还将有一个 SPD 集线器,以支持组件之间的带外通信。

它与 DIMM 两侧的两个温度传感器一起使用,以提供更多传感器信息。

我们已经看到性能显着提高的底板管理控制器,例如 ASPEED AST2500 到 AST2600 系列。造成这种情况的部分原因是,有了更多的传感器,BMC 可以更加了解服务器中正在发生的事情,从而对风扇速度做出更明智的调整。

我们的读者可能听说 DDR5 RDIMM 现在有更多组件。希望这有助于解释这些组件是什么。

接下来,让我们看看 DDR5 和新的 On-Chip ECC 功能,然后进入性能部分分析。

DDR5的片上ECC

DDR5 具有片上 ECC。这是一个经常被误解的。毫无疑问,这是一个很好的步骤,但这并不意味着所有 DIMM 都具有与服务器 RDIMM 传统上所具有的相同的 ECC 和 RAS 功能。

人们可以将此 ECC 视为防止 DDR5 芯片翻转的一项标准功能。确保端到端数据保护的边带功能是服务器 RDIMM 的优势所在。

虽然许多人一开始将此作为一项功能吹捧,但它也有实际用途。随着 DRAM 密度的增加和时钟速度的增加,设计 DDR5 规范的人们意识到这种组合有可能导致更多的片上错误。对于那些更熟悉闪存技术的人来说,NAND 已经经历了很多年,现在我们拥有更高的位密度,而且在整个 SSD 中也有更多的纠错。不过,固有的片上 ECC 优势在于,以前可能未在消费类 UDIMM 上发现的问题可能会被发现。

除此之外,实际上在 DIMM 和主机 DDR5 控制器之间发生了更多的 ECC。这是因为对于大多数 DDR5,我们从 72 位(64+8)到 80 位(两个 32+8)通道架构。有一些专业应用仍将使用 72 位以节省一些成本,但这可能是例外情况而不是常态。总而言之,我们将约 11% 到 20% 的通道位用于 ECC。

为什么这很重要的实际例子

STH 的部分测试服务器需要确定我们将使用哪些工作负载。最大的挑战之一是分析工作负载以确定它们将如何扩展。例如,我们经常在 CPU 基准测试中使用工作负载,这些工作负载主要根据每个时钟、频率和核心数的 CPU 指令进行扩展。渲染工作负载通常就是一个很好的例子。其他时候,我们发现工作负载受内存容量的限制很大。

在大量服务器中,内存容量是另一大挑战。DDR5 允许更大的 DIMM 尺寸,包括 128GB UDIMM。这是一个虚拟化工作负载,我们可以在其中改变核心数量,并看到当我们用完内存时性能提升停止。

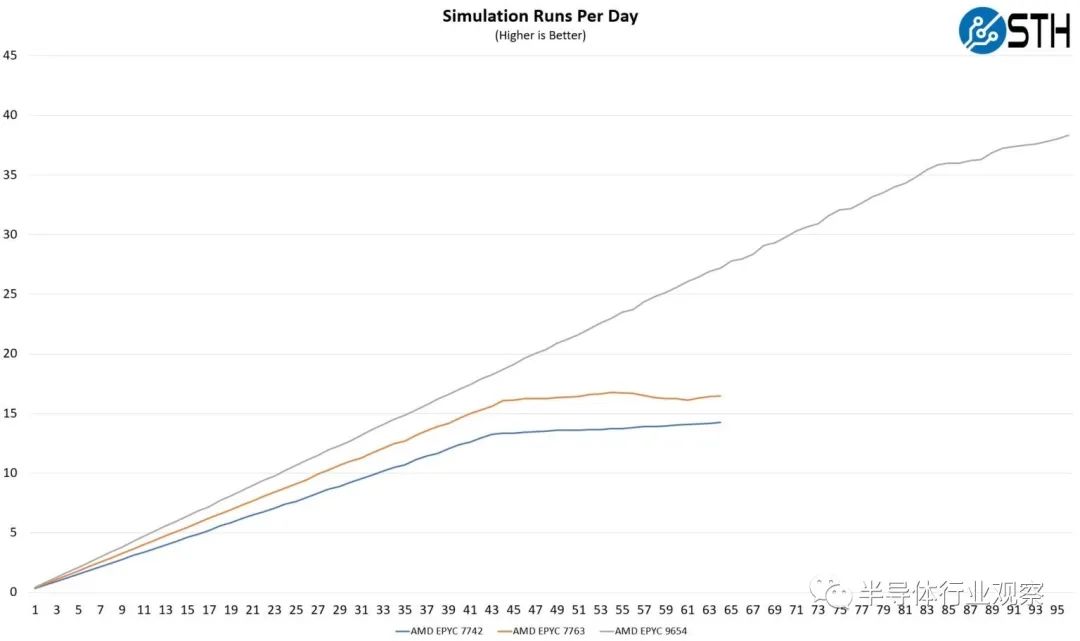

内存带宽是我们发现的另一个限制。

这是一个很好的工作负载示例,我们在系统中以如此快的速度推送数据,以至于在内存带宽受限后,添加内核或什至在相同数量的内核中增加频率都无济于事:

Top Bin AMD EPYC SKU 的模拟

切换到更新的平台,我们可以立即看到 DDR5 的影响。对增加的频率或核心数量没有反应的工作负载,在过渡到更新的 DDR5 平台后突然能够利用更多的计算资源。

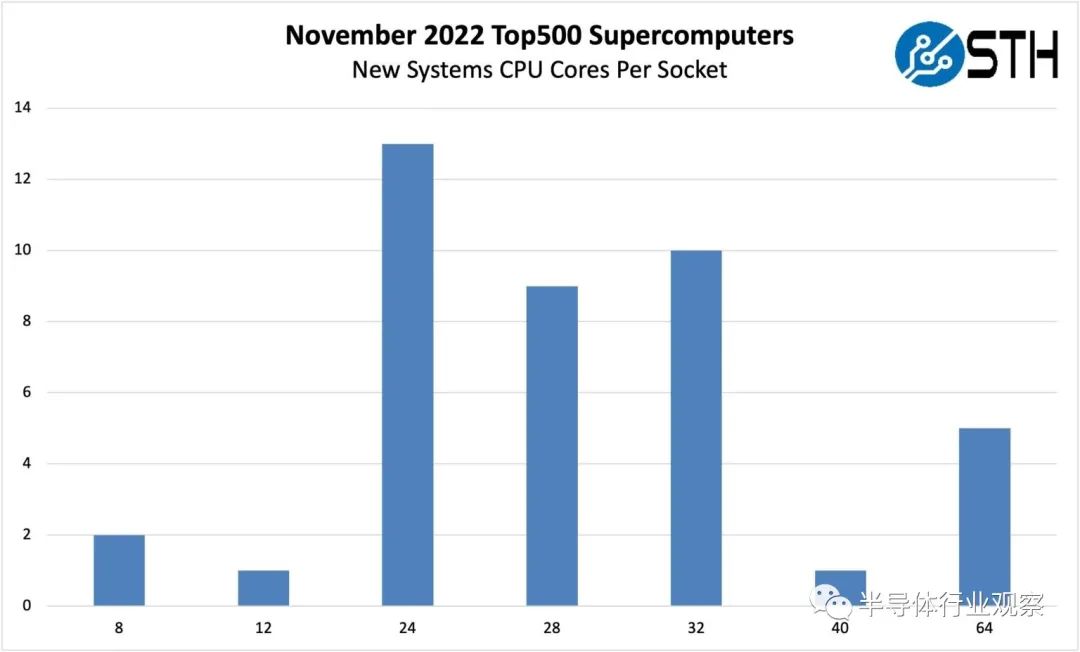

这是向 DDR5 过渡为何重要的主要示例。为了以另一种方式说明这一点,以下是 2022 年 11 月添加到 500 强名单的新系统:

2022 年 11 月 Top500 新系统 CPU 内核(按插槽)

人们很快就会注意到,部署的系统并未全部使用最大核心数部件。这是因为内存带宽通常是 HPC 应用程序的限制因素。我们已经看到了许多新颖的方法,例如 Milan-X 的更大缓存到 GDDR 内存和 HBM 内存的共同封装来应对这一挑战。对于通用市场,过渡到 DDR5 是朝着正确方向迈出的一大步。

CXL Type-3 设备和 DDR5

让我们暂时讨论一下 CXL 或 Compute Express Link。CXL 允许使用替代 CXL 协议在 PCIe Gen5 物理链路上进行加载/存储操作。新一代服务器支持 CXL 1.1,这是我们第一次在服务器中获得该功能。Type-3 设备是有效的内存扩展设备。这是 Astera Labs Leo CXL 内存扩展设备。

Astera Labs Leo CXL 内存扩展卡在 STH Studio 封面中带有 DIMM

可以看到,板上有四个 DDR5 DIMM 插槽,板底部有一个 PCIe Gen5 x16 连接器。在服务器中使用此设备产生的带宽大致相当于通过 x16 插槽的两个 DDR5 内存通道。延迟与通过一致的处理器到处理器链接访问内存大致相同(例如,CPU1 访问连接到 CPU2 的内存。)在系统中,这显示为另一个没有连接 CPU 内核但连接有内存的 NUMA 节点。我们将对此进行更深入的研究。

在这一代,AMD EPYC 9004 “Genoa” 正式支持 CXL 1.1 Type-3 设备。Intel 的 Sapphire Rapids Xeons 支持所有底层协议,上面显示的卡在 Sapphire Rapids 服务器上运行,我们已经看到了一段时间的演示。英特尔只是在发布时不支持 Type-3 设备。

尽管如此,最大的收获应该是 DDR5 不仅仅局限于 CPU 插槽旁边的 DIMM。相反,随着我们进入 2023 年及以后,许多 CXL Type-3 设备都被设计为支持 DDR5 内存。

最后的话

许多内存供应商提供了详尽的营销材料,解释 DDR5 的优势以及您应该转换的原因。我们则有一个简单的答案:在某些时候,您别无选择。

AMD EPYC 9004 Genoa 和第 4 代 Intel Xeon Scalable Sapphire Rapids 部件仅支持 DDR5。如果您购买服务器并想要新一代 x86 服务器,DDR5 是您唯一的选择(除了仅使用板载 HBM2e 的 Xeon Max 安装。)

总体而言,在提高每核心性能和增加核心数量之间,需要 DDR5 内存来推动服务器行业向前发展。

芯耀

芯耀

2840

2840

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍