比利时微电子研究中心(imec)于近日举行的2022年IEEE国际电子会议(IEDM)上,展示了一款掺杂镧(La)元素的氧化铪锆(HZO)电容器,不仅将循环操作次数提高到1011次,同时具备更佳的电滞曲线,唤醒效应亦有所改善。此次能够实现铁电电容的多项性能升级,关键在于介面氧化工程技术。这项铁电电容技术具备高性能、微缩能力与CMOS相容性,将是实现新一代嵌入式与独立式铁电随机存取记忆体(FeRAM)应用的关键。

FeRAM是一种备受瞩目的次世代非挥发性记忆体,不仅可以嵌入在SoC设计中,亦可作为独立的记忆体元件使用。FeRAM能填补高速DRAM(读取时间小于10奈秒)与高密度NAND记忆体之间的应用需求。其结构与DRAM相似,也是由1个电晶体与1个电容组成,但为了实现非挥发性,FeRAM是以铁电材料取代介电材料作为电容。铁电材料包含两种极化状态(+P与-P),藉由施加外部电场就能转换。过去几年,氧化铪锆(HZO)因为可用于CMOS製程,并具备10奈米以下的微缩潜能,成为备受瞩目的铁电材料。

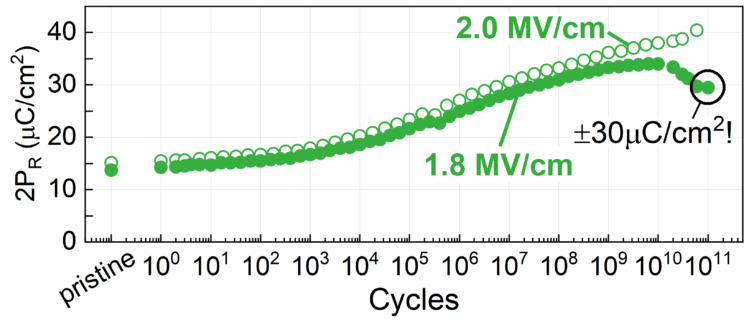

为了製成嵌入式记忆体或独立的记忆体元件,必须具备几项元件特性。理想情况下,铁电记忆体的电容须具备1012次循环以上的超高耐久性,同时,在生命週期内残留极化量(2PR)也需要达到30~40µC/cm2。但到目前为止,业界仍未能同时达成这两个目标,因为铁电材料的电容面临了延迟唤醒(最初的残留极化量低)与快速疲劳(残留极化量快速下降)的问题。

不同铁电电容与氮化钛(TiN)电极的元件耐久性测量(残留极化值与循环次数的比较)。绿色曲线是重点,该元件採用三层(TriLayer)堆叠,包含一层二氧化钛(TiO2)种子层与五氧化二铌(Nb2O5)覆盖层。在沉积氧化层后,立即将三层堆叠进行电浆处理,就能获得最佳性能。外部电场(单位为MV/cm)另外标记在括号内。

比利时微电子研究中心铁电元件研究计画主持人Jan Van Houdt说明,利用介面氧化工程技术,以及在镧掺杂氧化铪锆元件层各导入一层厚度约1奈米的二氧化钛(TiO2)种子层与一层2奈米的五氧化二铌(Nb2O5)覆盖层,我们成功开发了同时具备优良耐久性(1011次循环操作)与残留极化量的元件。在施加1.8MV/cm外部电场的情况下,残留极化量达到30µC/cm2,而且起始操作阶段的极化性也不错。

经过初步了解,该元件与Nb2O5覆盖层的接面,能促进HZO材料转换至所需的斜方晶相,也就是铁电相,做法是在HZO层注入氧离子,TiO2层则有利于製出(002)晶体,进一步提高残留极化的初始值。Jan Van Houdt透露,imec团队还尝试了另一种採用不同前驱物来沉积HZO层的做法,结果获得打破历史纪录的极化值,在电场为3MV/cm的情况下,达到66.5µC/cm2。但使用这种作法製作出来的元件,循环操作只有106次。

Jan Van Houdt总结说,有了这项高性能、与CMOS相容且可微缩化的铁电电容技术,业界将可进一步导入原子层沉积技术,将原先採用平面结构的铁电电容3D化,让储存密度大幅升级,更贴近各种应用的需求。这将是FeRAM技术发展史上一个重要的突破。

1259

1259