受到人工智能/机器学习(AI/ML)和数据中心、云、高性能计算等数据密集型应用的驱动,数据中心架构正在持续演进,这对PCIe接口提出了更高的要求。

面对未来市场需求,近日Rambus发布了由PHY和控制器IP组成的PCI Express®(PCIe®)6.0接口子系统,这是继今年年初Rambus推出PCIe 6.0控制器产品后的又一大动作。

图 | PCIe 性能加速随着时间的推移(图片来源:Rambus Inc.)

Rambus 战略营销副总裁Matt Jones表示:“芯片设计周期通常都非常长,而通过采用Rambus的PCIe 6.0接口子系统,可以降低芯片设计人员的设计复杂性。这是因为在过去,芯片设计人员需要把PHY和控制器单独拿来使用,同时还要重复一些冗杂的验证工作,而现在,Rambus PCIe 6.0接口子系统集成了控制器和PHY,并已经经过设计验证,可以直接在其芯片中实施。”

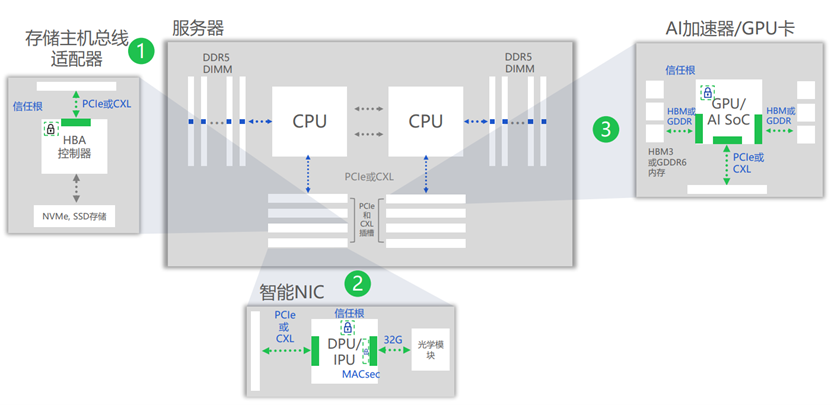

Matt Jones以数据中心举了三个例子,在这三个例子中,每个示例都有一个存储主机总线适配器、一个智能网卡和一个AI加速器或GPU卡。我们看到,PCIe PHY和控制器的组合提供了一个成熟的接口,可以从服务器主板上的PCIe插槽和物理接口连接到控制器芯片上。这三个例子都保证了PCIe或CXL接口是经过硅验证的,并且不会增加设计复杂性。

图 | 数据中心应用示例(图片来源:Rambus Inc.)

Rambus PCIe 6.0接口子系统有何特色?

Rambus PCIe 6.0接口子系统的数据传输速率高达64GT/s,并且经过全面优化,可满足先进异构计算架构的需求。该子系统中的PCIe控制器具备完整性和数据加密(IDE)引擎,专门用于保护PCIe链接和通过它们传输的重要数据。另外在PHY方面,它还提供对CXL 3.0的全面PHY支持,支持缓存一致性内存共享、扩展和池化的芯片级解决方案。

图 | PCIe 6.0接口子系统(图片来源:Rambus Inc.)

Rambus PCIe 6.0接口子系统有以下主要特性:

- 支持PCIe 6.0规范,包括64 GT/s数据传输速率和PAM4调制信号

- 实现低延迟前向纠错(FEC),保证链路稳健性

- 支持固定尺寸的FLIT,可实现高带宽效率

- 向后兼容PCIe 5.0、0和3.0/3.1

- 通过IDE引擎(控制器)实现最先进的安全性

- 支持CXL 3.0,用于优化内存资源的新使用模式(PHY)

总的来讲,PCIe 6.0能够提供高带宽,低功耗以及低延迟互联,所以是数据中心以及很多其他数据应用的非常理想的解决方案。

从NRZ切换到PAM4,PCIe 6.0的功耗是否会增加?

为了进一步满足PCIe 6.0达到64GT/s数据传输速率的需求,它的架构必须要重新优化和调整。同时,在整个电路和电路传输机制的配比上也存在着巨大的差异,其中最大的变化就是从不归零编码NRZ到四电平脉冲辅助调制PAM4的转变。通常,在PAM4的编码体系下,数据传输速率可以实现翻倍,但Rambus却采用了和之前一样的时钟速率,即两个比特。这是因为如果用传统的方法,通过增加时钟周期频率来提升数据传输速率,毫无疑问功耗会显著增加。

Matt Jones表示:“Rambus选择的是另外一种方法来增加数据传输速率,即采用全新的L0p模式,在该模式下可以对信道进行更加动态化的调整和控制,可以在减少信道总数的情况下保证现有的数据传输速率。同时,在管理功耗过程中,PPA是非常重要的,所以在设计PCIe 6.0相关子系统产品时,我们也进一步优化了相关的设计。”

不过,Matt Jones也坦言:“基于上述全新的创新技术,可以实现对PCIe 6.0功耗的可控,但在对性能需求比较高的时候,我们的确会牺牲掉一部分功耗,但是在对性能要求没有那么高的时候,我们在功耗上就可以实现更强的可控性。所以整体来讲,系统功耗在PCIe 6.0标准下是得到了优化的。”

为什么PCIe 6.0可以提供对CXL 3.0的全面PHY支持?

关于PCIe 6.0可以提供对CXL 3.0的全面PHY支持,Matt Jones认为这是CXL 3.0和CXL整个工作小组和委员会做出的一个非常聪明的决定,因为CXL 3.0重新使用PCIe 6.0作为物理层的接口,并且重新复用了PCIe 6.0的电气接口是一个非常重要的,可以保证兼容性的决定。从而可以确保在数据中心,各个服务器之间数据传输和数据移动的一致性,可以在现有的服务器架构下,在不改变现有PCIe插槽以及其他组件的前提下,进一步实现低延迟,以及CXL 3.0所支持的闪存一致性。

值得一提的是,不管是PCIe 6.0还是CXL 3.0,它们所具备的更高数据传输速率都更好地与异构计算所需要的分布式数据传输模式相吻合,两者相辅相成。

Rambus大中华区总经理苏雷表示:“Rambus也发布了CXL内存互联计划,CXL带来了池化、内存共享,还有内存扩展的概念,将从根本上改变整个数据中心的架构,特别是池化解决方案,未来将直接提高数据中心内存资源的利用率。”

PCIe 6.0可以给数据中心带来哪些改变?

Matt Jones认为PCIe 6.0的落地,将给数据中心带来四个重要的变化,具体如下:

- 第一点,PCIe 6.0和64GT/s数据传输速率的提升,会带来数据中心架构的变化,这意味着越来越多的数据中心会向异构计算进行迭代和变化。

- 第二点,随着PCIe 6.0的推出,数据中心本身的架构会变得更加先进,不管是分布式计算还是可组合的架构。

- 第三点,随着系统带宽大幅提高,在异构计算的模型之下,会催生出专门针对特别应用所开发的不同加速器,而且也可以进一步实现数据在不同组件之间传输效率的提升,然后针对不同的工作负载也会有一些具体的更好的应用,比如高性能计算、云服务商工作负载的进一步管理和优化等。

- 第四点,随着数据使用量的爆炸性增长,以及人工智能和机器学习的持续发展,PCIe 6.0将使更大的数据集能够在整个系统中移动,以进行处理,并提高数据中心的智能化。

PCIe的速率随着迭代不断提高,板级接口何时需要用到光纤连接?

PCIe的每一次迭代都会带来速率的提高,当PCIe发展到6代,甚至后面的7代以后,对板级接口方面的要求也会越来越高,或许会使用到光纤连接。当前,不管是从系统层面,还是从研发层面,包括一些PCIe 的工作小组,大家也都在探讨,并且已经把这个问题纳入日程。

对此,Matt Jones表示:“在不同的PCIe版本之间,到目前为止还是尽可能地做到对前代更好的兼容性,有关未来的发展我们很难推断,以及预测未来的走向,未来什么时候,到底是在PCIe 7.0,还是PCIe 8.0,我们需要用到光纤的连接,这些都还是未知的。但是不管怎么样,这个问题是必须要解决的。至于未来的发展方向,我们只能根据下一步的动向来作出具体的决定。”

数据中心刚开始向PCIe 5.0过渡,PCIe 6.0何时能商业落地?

当前,数据中心新的服务器平台基本才开始向PCIe 5.0过渡,而Rambus现在就开始推出PCIe 6.0接口子系统方案,是否为时过早?答案肯定是否定的,因为当年PCIe 5.0的相关技术,Rambus等比较领先的厂商也是在多年以前就开始开发,到现在才能得到普及。

Matt Jones表示:“根据对既往模式的预估,PCIe 6.0现在已经正式发布,预计需要两年时间才能够完成所有后续系统的筹备和开发,到2025年左右才会出现更大范围的系统性应用。不过两年后设计完成,社会面对其进一步的广泛采纳取决于很多其他因素,比如基础设施、CPU和其他组件的准备情况等。”

同时,关于PCIe 6.0首先会在哪些领域首先落地的问题,Matt Jones认为,每次进入新一代PCIe标准,最先推出相关产品并最先采纳类似技术的都是那些大规模的云服务商,或者是一些终端用户的应用场景。针对PCIe 6.0,我们认为那些针对专门应用或者专门工作负载的加速器应该最先会用到PCIe 6.0。”

芯耀

芯耀

3890

3890

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍

[课程]STM32电机控制软件开发软件X-CUBE-MCSDK 6x介绍