全阶段优化设计,英特尔Quartus Prime成就强大FPGA

一、前言

上一篇介绍了基于FPGA的除法器设计,想要设计一个优秀的FPGA除法器也是很有难度的,看看网上多少相关资料吧。

看样子,FPGA的除法器是个很有研究价值的东西。

看样子,FPGA的除法器是个很有研究价值的东西。

二、DDS由来 DDS技术是一种新的频率合成方法,是频率合成技术的一次革命,最早由Joseph Tierney等3人于1971年提出,但由于受当时微电子技术与数字信号处理技术的限制,DDS技术没有受到足够重视,随着数字集成电路和微电子技术的发展,DDS技术日益展露出它的优越性。

三、DDS算法原理 DDS的工作原理为:在参考时钟的驱动下,相位累加器对频率控制字进行线性累加,得到的相位码填入波形存储器中,使之能够输出波形幅度量化序列,经过模数转换器得到相应的阶梯波(D/A和滤波器不进行设计),最后再使用低通滤波器对其进行平滑,得到所需要频率的平滑连续的波形,其结构框图如图所示。

四、开发工具

1、Quartus II 15.0 (64-bit) 2、matlab R2012b 3、Modelsim SE 10.4c 五、地址查找表(ROM)制作 1、用Matlab生成查找表(ROM)的源数据。

2、ROM存储Matlab生成的数据

生成.mif文件加入Matlab生成的数据,做ROM查找表,

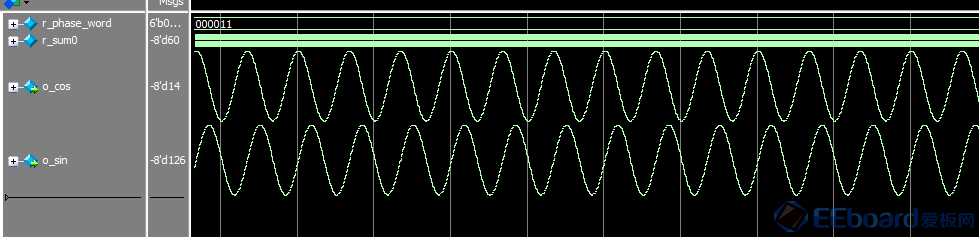

六、Modelsim仿真验证

不同的频率控制字可以实现不同的频率输出。

七、Quartus ii板上验证

生成RTL原理图(使用了2个ROM)。

quartus ii15.0和之前的版本有些出入,不能做成signed line chart这种类型了,只能做成signed bar chart,所以,在实现上和Modelsim有些出入。

注意点:在做成模拟波形时,一定要设置成signed型,如果是unsigned型,则波形异常,如下所示:

八、结束语

本篇完成了基于FPGA的DDS的制作,本次Arrow DECA开发套件的评测也即将结束,很感谢ALTERA和爱板网提供的开发套件,学到了很多东西。

|  /4

/4

/4

/4