|

本文主要基于紫光同创Pango Design Suite(PDS)开发软件,演示FPGA程序的加载、固化,以及程序编译等方法。适用的开发环境为Windows 7/10 64bit。

测试板卡为全志T3+Logos FPGA核心板,它是一款基于全志科技T3四核ARM Cortex-A7处理器 + 紫光同创Logos PGL25G/PGL50G FPGA设计的异构多核全国产工业核心板,ARM Cortex-A7处理单元主频高达1.2GHz。核心板CPU、FPGA、ROM、RAM、电源、晶振、连接器等所有器件均采用国产工业级方案,国产化率100%。

核心板内部T3与Logos通过SPI、CSI、I2C通信总线连接,并通过工业级B2B连接器引出LVDS DISPLAY、RGB DISPLAY、MIPI DSI、TVOUT、TVIN、CSI、GMAC、EMAC、USB、SATA、SDIO、UART、SPI、TWI等接口及FPGA IO引脚,支持双屏异显、Mali400 MP2 GPU、1080P@45fps H.264视频硬件编解码。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。 FPGA程序位于产品资料Demo目录,请将对应的FPGA程序拷贝至Windows非中文路径下。下表为Demo目录的FPGA程序目录结构及主要文件说明。 表 1 目录 | 文件/目录 | 说明 | bin | xxx.sbit | 可执行程序(BitStramFile文件),用于在线加载 | xxx.sfc | 可执行程序,用于固化至SPI FLASH | project | xxx_pgl25g/xxx_pgl50g | constraints | 约束文件目录 | hdl | Verilog源码文件目录 | xxx.pds | Pango Design Suite工程文件 |

按照本文档操作前,请先参考软件安装相关文档安装Pango Design Suite,并将评估板通过配套的FPGA下载器正常连接至PC机。 程序加载本小节以led_flash案例为例,演示程序加载方法。 - 打开Windows的设备管理器,查看并确认FPGA下载器已正常连接至PC机。

图 1

双击Pango Design Suite安装目录下"C:\pango\PDS_2021.1-SP7.1\bin\cdt_cfg.exe",打开Fabric Configuration界面。

图 2

图 3

将评估板上电,鼠标右键点击Fabric Configuration界面空白处,选择"Scan Device"选项,通过FPGA下载器扫描并连接FPGA设备。

图 4

连接成功后,将出现FPGA芯片图标,并自动弹出FPGA程序选择窗口,请选择对应的xxx.sbit文件进行加载。

图 5

图 6

鼠标右键点击FPGA芯片图标,选择"Program…",将目标程序加载至FPGA运行。

图 7

图 8

程序成功加载后,Console控制台将会打印显示"COMMAND[Program] execute successfully"信息。同时可观察到评估底板LED按照一定的时间间隔循环亮灭,说明程序在线加载与运行正常。

图 9

程序固化本小节以led_flash案例为例,演示程序固化方法。 双击Pango Design Suite安装目录下"C:\pango\PDS_2021.1-SP7.1\bin\cdt_cfg.exe",打开Fabric Configuration界面。

图 10

将评估板上电,鼠标右键点击Fabric Configuration界面空白处,选择"Scan Device"选项,通过FPGA下载器扫描并连接FPGA设备。

图 11

连接成功后,将出现FPGA芯片图标,并自动弹出FPGA程序选择窗口,点击Cancel,不加载xxx.sbit文件。

图 12

鼠标右键点击FPGA芯片图标,选择"Scan Outer Flash"扫描并识别SPI FLASH芯片。

图 13

扫描成功后,将自动弹出文件选择窗口,选择需固化的xxx.sfc文件。

图 14

鼠标右键点击"Outer Flash"芯片图标,选择"Program…"进行程序固化。

图 15

图 16

程序固化完成后,Console控制台将会打印显示如下信息。

图 17

将评估板断开FPGA下载器并重新上电,即可观察到评估底板LED按照一定的时间间隔循环亮灭,说明程序固化成功、运行正常。 工程导入与程序编译如需导入工程以及重新编译程序,请按如下步骤进行操作。如无需导入工程或重新编译程序,请忽略本章节内容。 本小节以led_flash案例为例,演示基于Pango Design Suite导入、编译FPGA工程的步骤。 工程导入- 请双击桌面Pango Design Suite图标,打开软件。

图 18

在弹出的界面中点击"Open Project"。

图 19

在弹出的界面中选择FPGA案例"project\led_flash_xxx\目录下的xxx.pds文件,并点击Open打开。

图 20

弹出如下界面,工程导入完成。

图 21

工程新建、移植本小节主要说明工程新建以及对现有工程进行移植的简要步骤。若无需新建工程或对现有工程进行移植,请跳过本小节内容。 - 双击打开Pango Design Suite,在弹出的界面中点击"New Project"。

图 22

图 23

- 输入工程名字,根据实际情况修改文件保存路径,并点击Next。

图 24

- 在弹出的界面中勾选"RTL project",并点击Next。

图 25

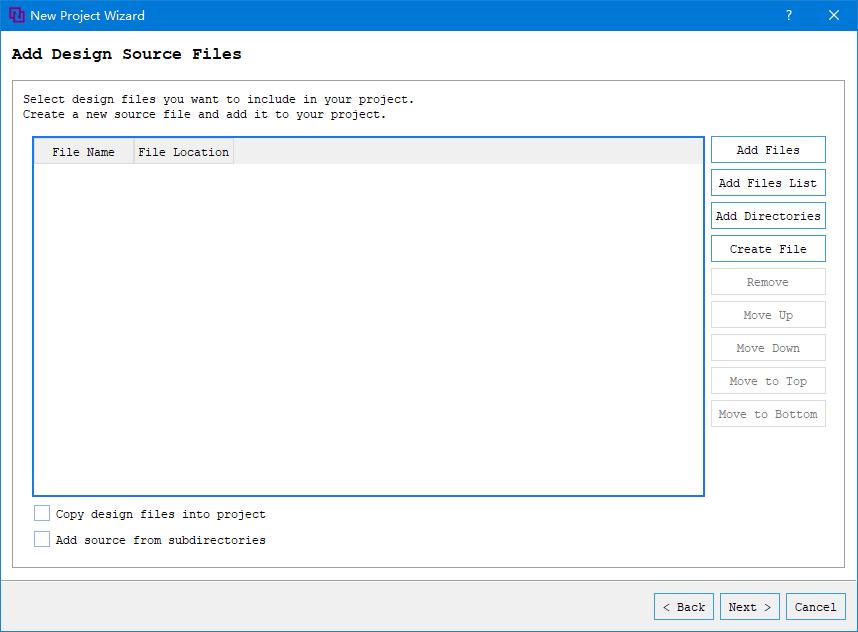

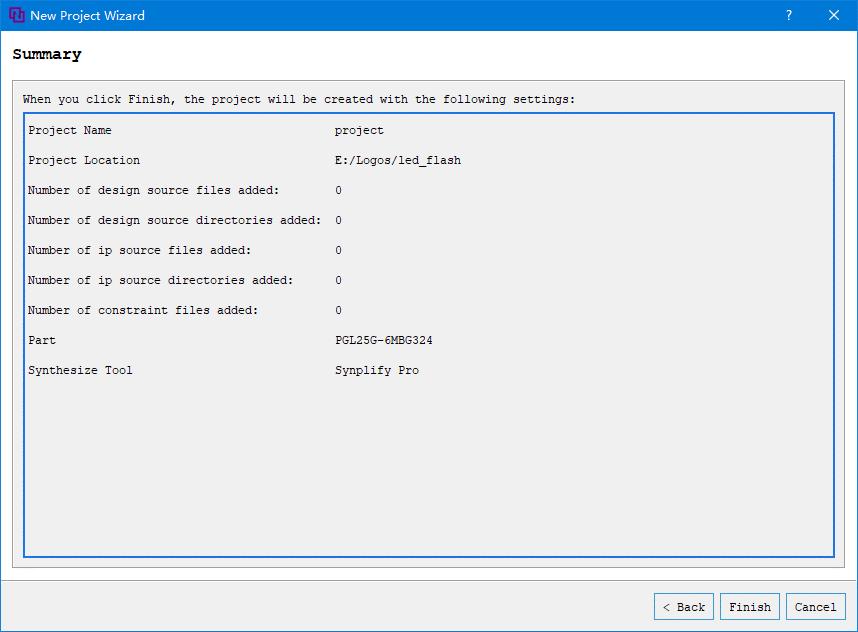

- 弹出如下Add Design Source Files界面,直接点击Next跳过。

图 26

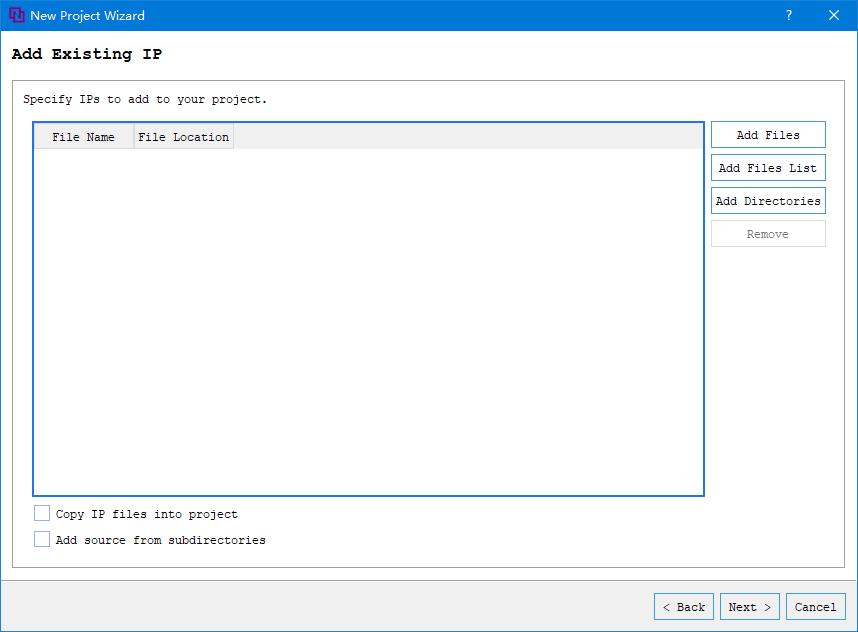

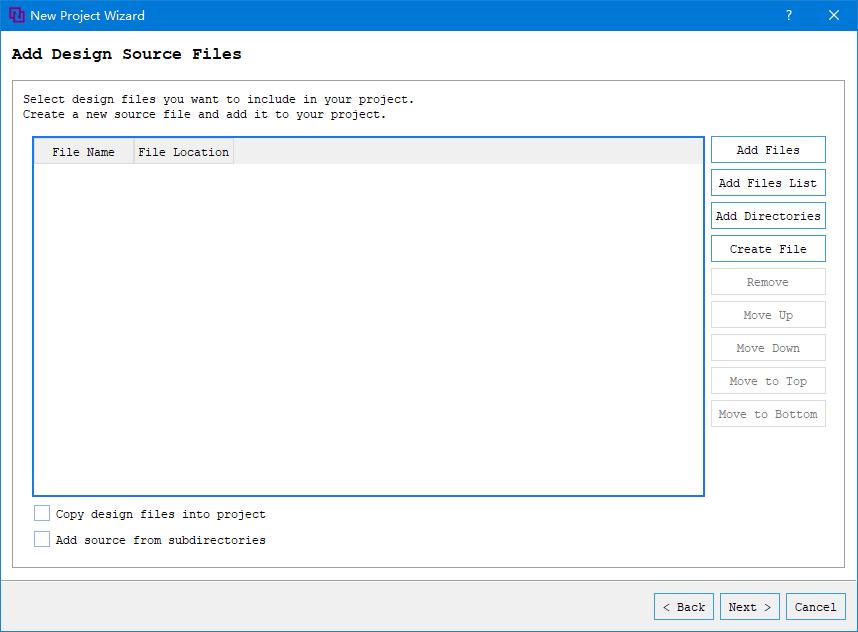

- 弹出如下Add Existing IP界面,直接点击Next跳过。

图 27

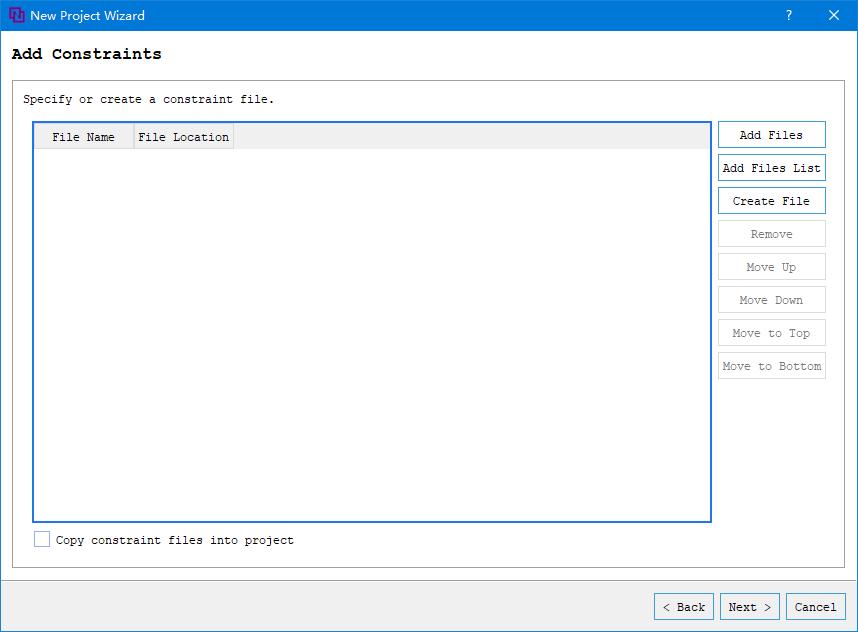

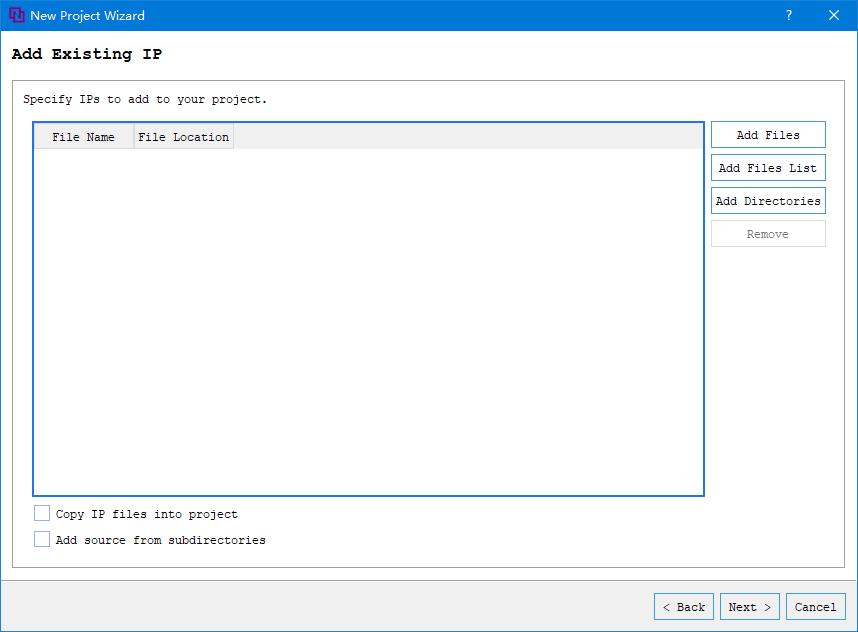

弹出如下Add Constraints界面,直接点击Next跳过。

图 28

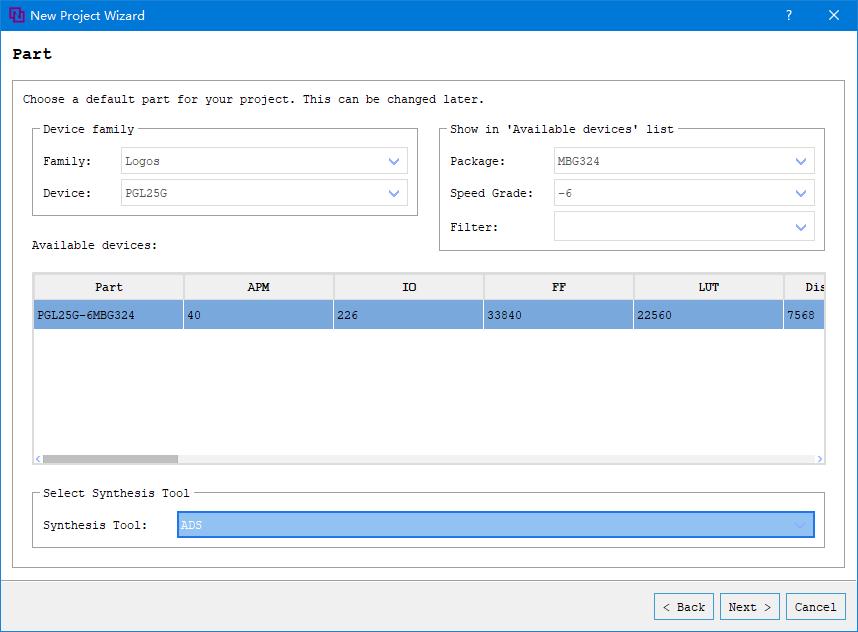

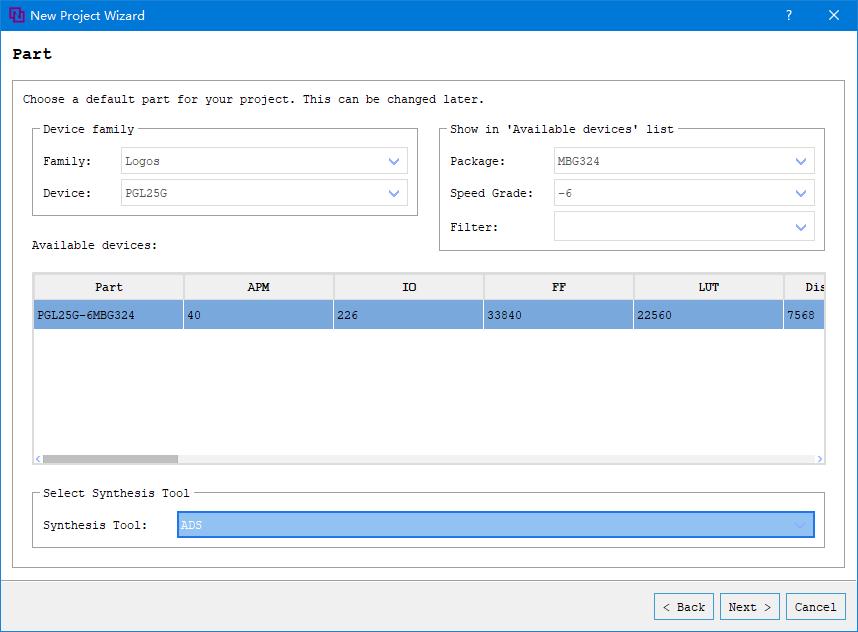

在弹出的工程配置界面中设置FPGA芯片参数。Family:Logos,Device:PGL25G,Package:MBG324,Speed:-6,Synthesis Tool:ADS,设置完成后,请点击Next。

图 29

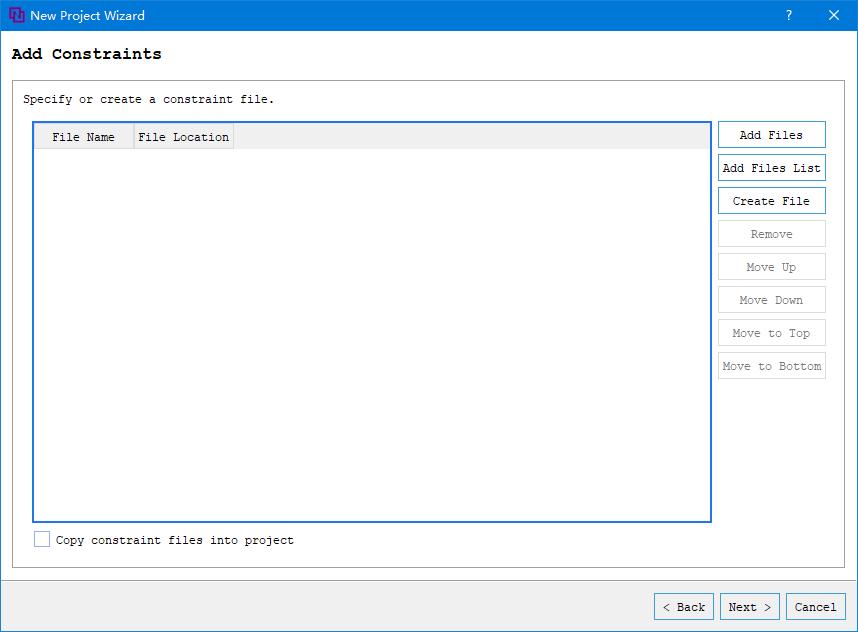

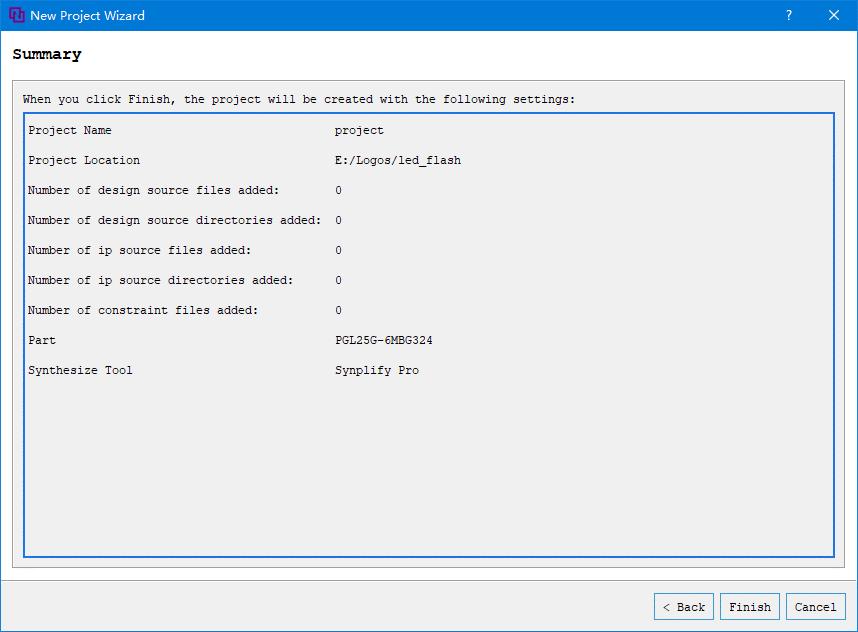

在弹出的界面,点击Finish,即可完成工程新建。

图 30

图 31

在工程界面,右击工程Designs,点击"Add Source"新建模块文件。

图 32

在弹出如下界面,选择"Add or create design sources",并点击Next。

图 33

在弹出的界面中,点击"Create File"选项,输入新建的模块文件名称,依次点击OK。

图 34

图 35

在弹出的界面,可直接通过图形界面配置引脚约束。由于本次演示通过新建约束文件进行引脚约束,请直接点击OK跳过。

图 36

完成模块文件新建后,此时将在工程界面右侧出现程序编辑窗口。

图 37

打开案例"project\led_flash_xxx\hdl\led_test.v"文件,将所有代码拷贝至程序编辑界面或自行编写,并点击保存编辑。完成保存后,Console窗口无Errors和Warning则说明程序语法无错误。

图 38

图 39

在工程界面,右击"Constraints -> Add Source"进行引脚约束。

图 40

在弹出界面,选择"Add or create constraint sources",并点击Next。

图 41

在弹出的界面中,点击"Create File"选项,输入新建引脚约束文件名称,依次点击OK。

图 42

图 43

引脚约束文件新建完成后,双击打开工程界面的xxx.fdc文件,如下图所示。

图 44

图 45

在如下界面选项栏中,依次点击"Device -> IO",根据工程xxx.v文件在"Tool Tabs"窗口生成引脚约束列表。请根据硬件连接进行引脚选择。

图 46

引脚选择完成后,呈现界面如下图所示。至此,FPGA工程新建完成。

图 47

程序编译- 双击"Generate Bitstream"进行FPGA程序编译。

图 48

编程完成后Console窗口将会打印信息:Process "Generate Bitstream" done,并在FPGA工程generate_bitstream目录下生成xxx.sbit文件。

图 49

图 50

如需生成用于固化至SPI FLASH的xxx.sfc文件,请按照如下步骤执行。 - 在菜单栏依次点击"Tools -> Configuration",进入Fabric Configuration界面,在菜单栏依次点击"Operations -> Convert File"。

图 51

图 52

在弹出界面,请按照下图方法配置SPI FLASH信息。Factory Name:WINBOND,Device Name:W25Q64Q(SPI FLASH芯片型号),BitStramFile:BitStramFile文件(xxx.sbit)路径,Output File Name:生成xxx.sfc文件保存路径(默认保存在BitStramFile文件同级目录下)。配置完成后,请点击OK保存配置。

图 53

弹出如下界面,请点击OK。即已成功生成用于固化至SPI FLASH的xxx.sfc文件。

图 54

图 55

|  1/2

1/2

发表于 2023-3-1 16:39:26

发表于 2023-3-1 16:39:26