|

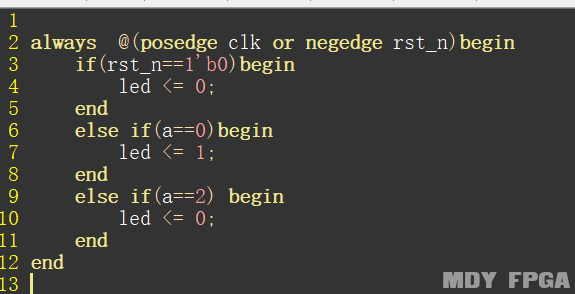

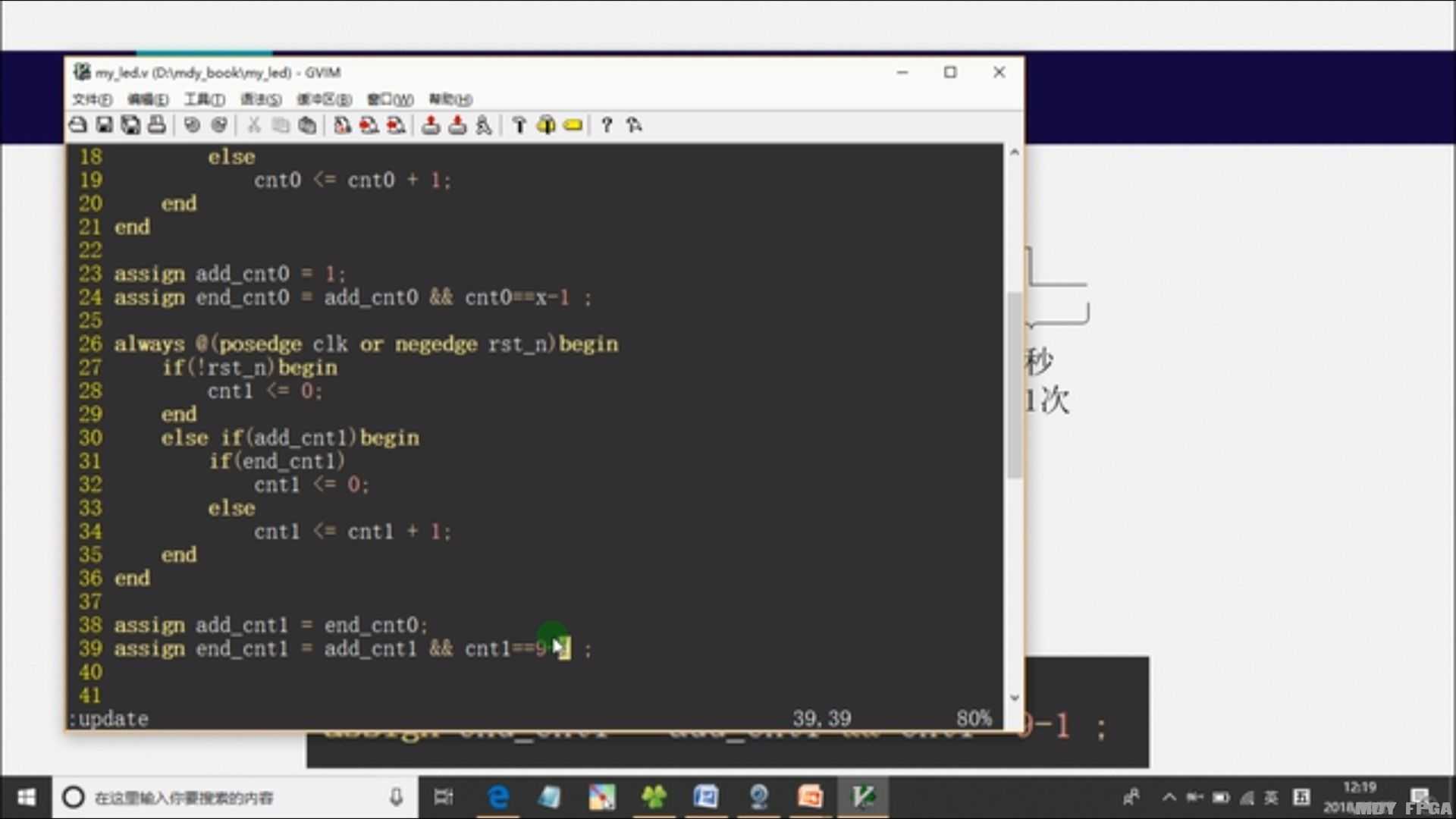

【问题1:ALWAYS不写ESLE表示保持原来的值】:下面是一个ALWAYS语句,当rst_n==1、a==1时,led的值是多少?

答:当rst_n==1,a==1时,上图中第3、第6和第9行都不满足条件,因此第4、7、10行的赋值语句都不会执行。也就是说led值没有改变。

所以,时钟上升沿之后,led还会保持原来的值。如果原来的led等于0,之后也是0;原来等于1,之后也是等于1.

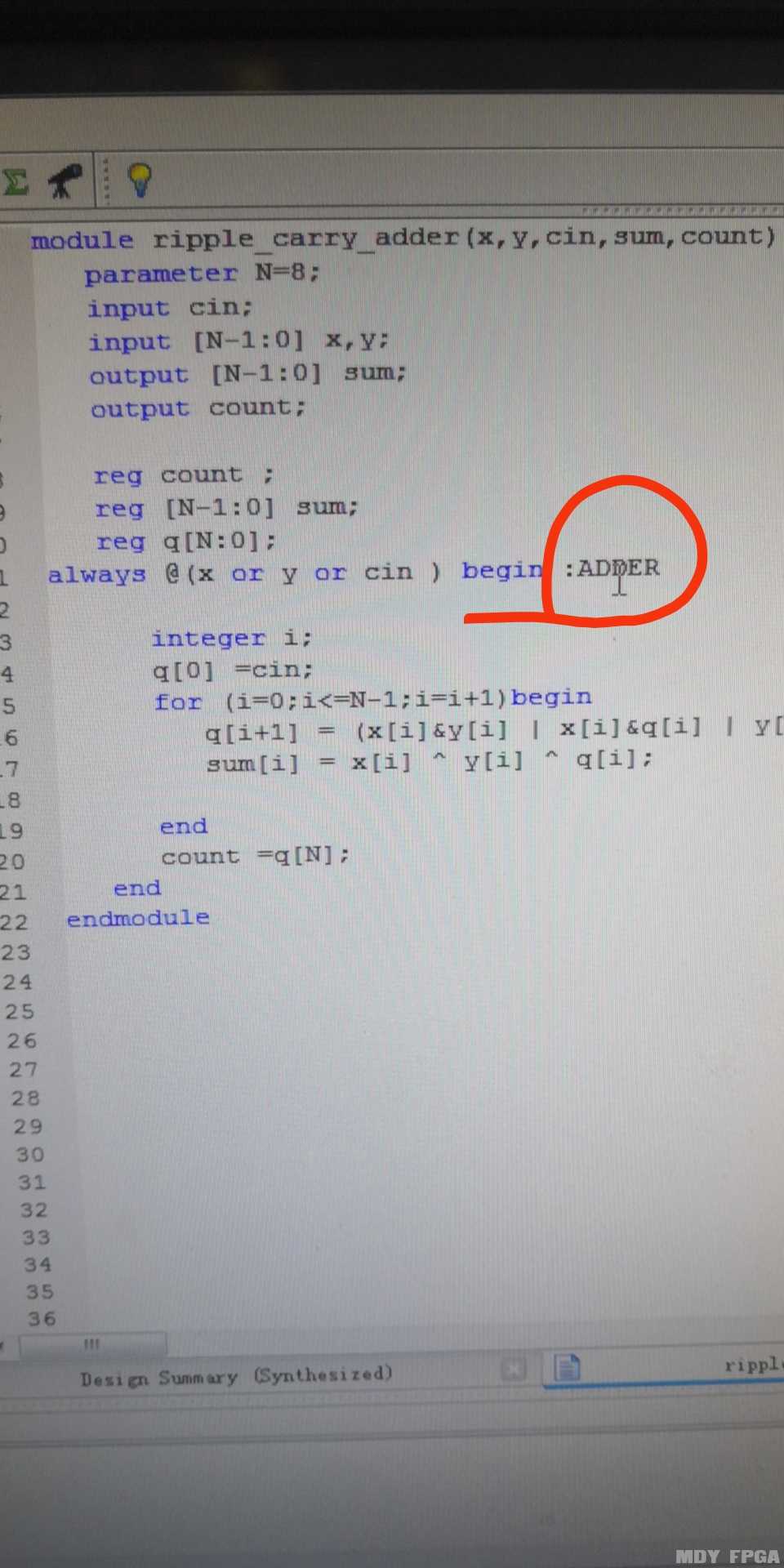

【问题2】为啥begin后面加这个冒号,以前没见到过。  答:begin后面加冒号,相当于这个begin end块起一个名字。起名字是做区分用,一般情况下,不对begin/end命名,所以这种写法很少见。

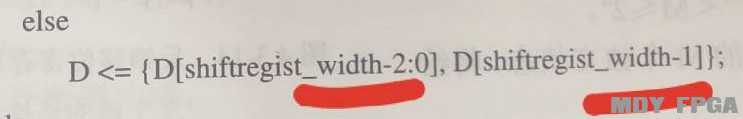

【问题3】请问以下变量后加个"-"意思是取这个变量的某几位吗?

答:上面的按减号带入结果就可以了,例如 data[7-1],就是data[6]。 data[7-1:0],就是data[6:0]。

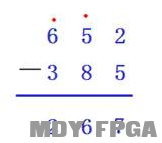

【问题4】二进制000-二进制001=111 这个最高位怎么算的?

答:参考十进制加减的运算方法,如下图所示得到的。

【问题5】rst_n==1'b0 和!rst_n不同的问题。   LED灯设计为什么LED和计数器复位条件不一样?

答:这两个结果是一样的,都是当rst_n为1时复位。只是写法不同。

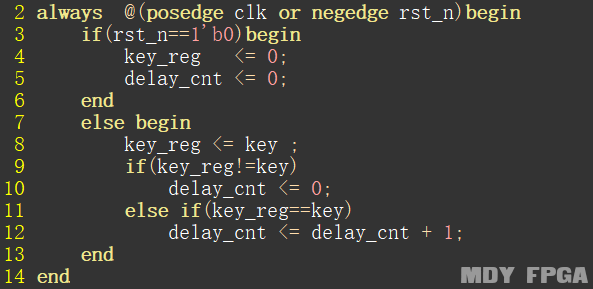

【问题6:一个always里有多少信号时的理解问题】如下图所示,第9行代码里的key_reg值,是等于第8行的key的值还是key_reg的值。是先执行第8行,再执行第9行代码吗?

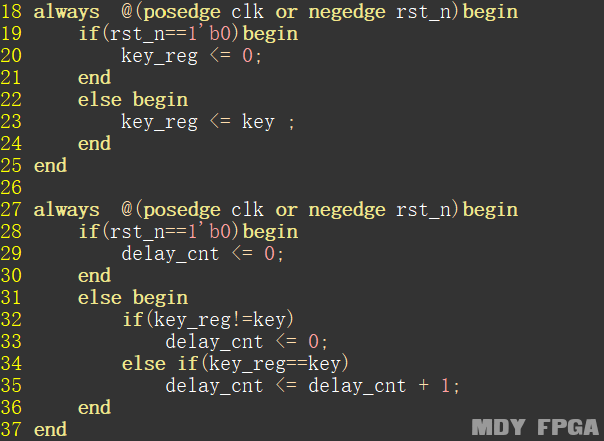

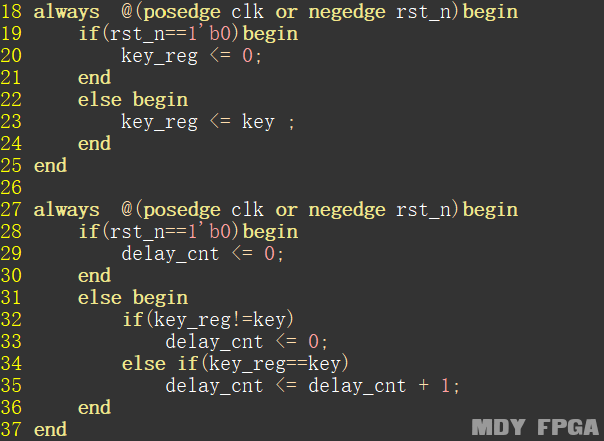

答:当一个always里设计了多个信号时,如上图中设计了key_reg和delay_cnt的值,其实质可拆分成如下代码。

答:当一个always里设计了多个信号时,如上图中设计了key_reg和delay_cnt的值,其实质可拆分成如下代码。

而众所周知,verilog代码中每个always都是独立并且同时执行的。因此上图中第23行的代码和第32行的判断是同时进行的。假设当前key_reg等于0。在时钟上升沿前key等于1。那么第23行执行后,key_reg值更新为1。同时第32行判断时key_reg值仍然为0,不是最新的值为1。

在此,MDY强烈建议,一个ALWAYS设计一个信号,有助于做逻辑设计,理清思路,避免很多理解上的问题。而且事实上,一个always设计多个信号更像写“软件”的代码,是用软件思维在设计FPGA,而在FPAG中是不规范的。

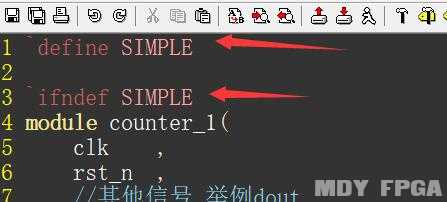

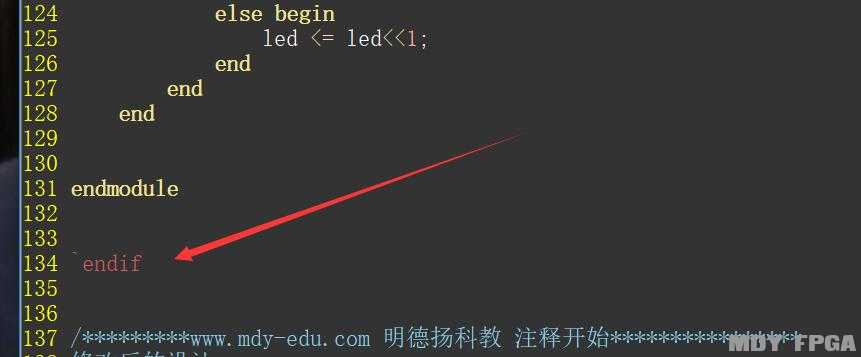

【问题7】红色箭头指的那些语句是什么意思?

答:这是宏定义的的一种用法。此时表示该.v文件使用的是从“ 'ifndef SIMPLE”到“ 'endif”的代码,如果把“' define SIMPLE”注释掉的话,使用的就是除“ 'ifndef SIMPLE”到“ 'endif”以外的代码。

|  /1

/1

/1

/1