|

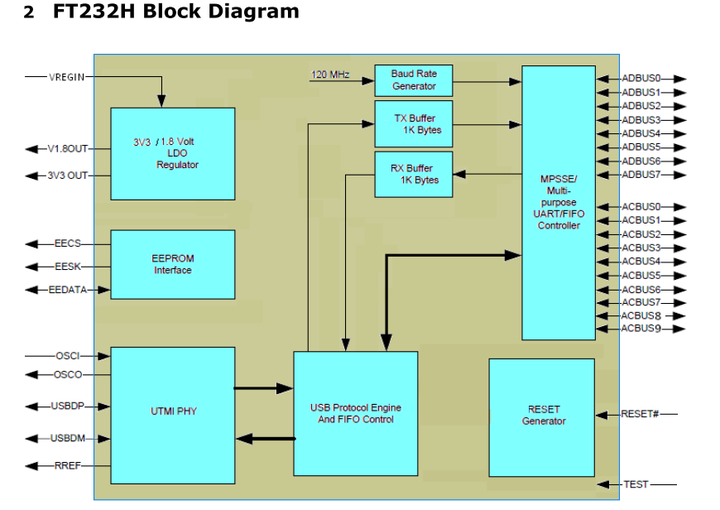

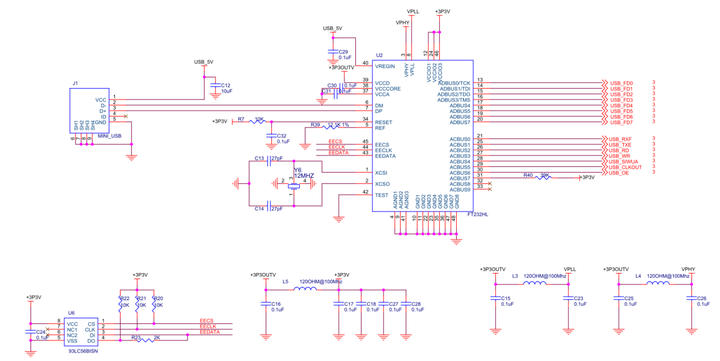

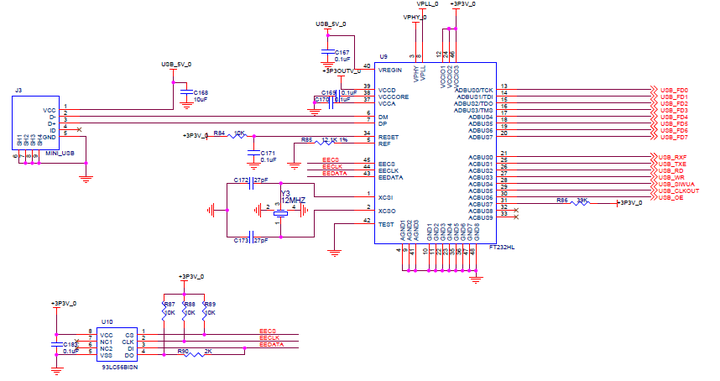

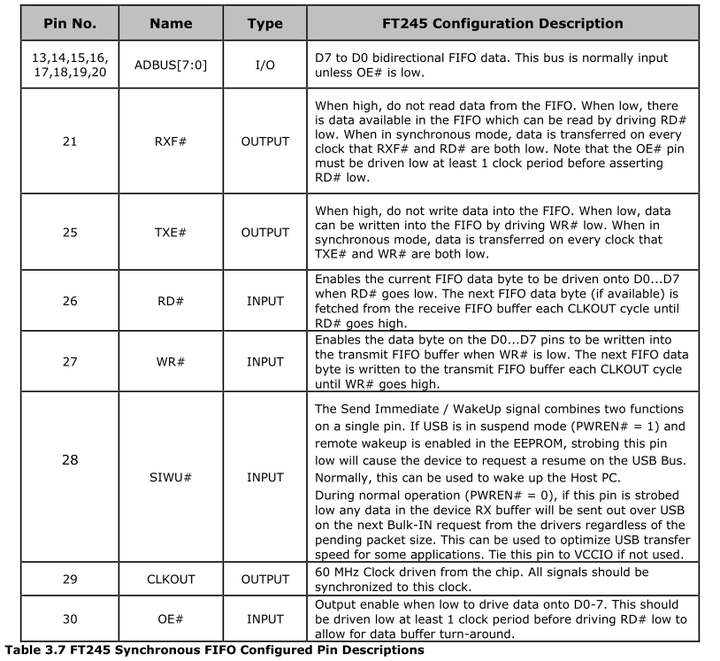

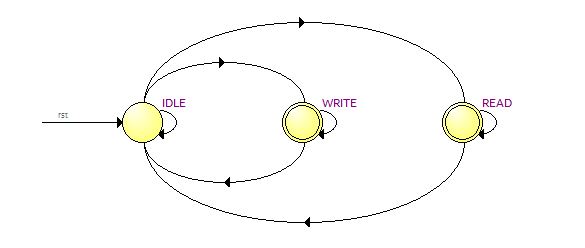

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处(http://www.alinx.com)。 适用于板卡型号: PGL22G 1. 简介本教程介绍如何使用FTDI公司的FT232H驱动芯片进行USB数据传输,文中从底层FPGA、驱动层固件(FT232H固件)及上位机测试软件设计方面阐述了USB开发的整个流程。 2. 实验原理2.1 FT232H原理介绍 FT232H是由FTDI公司生产的单路USB2.0驱动芯片,USB速度高达480Mb/s,支持转UART或FIFO模式,并可配置成多种工业串行或并行接口: (1)可配置成UART接口; (2)FT245同步FIFO接口; (3)FT245风格异步FIFO接口; (4)同步或异步Bit-Bang接口; (5)MPSSE接口; (6)Fast串口; (7)CPU风格FIFO接口; (8)FT1248接口。 在本实验中配置成FT245同步FIFO接口。下面是FT232H的内部结构图。  2.2 硬件原理图 如下为AX7035/AX7050开发板的USB部分原理图,USB驱动芯片采用FT232HL,配置为FT245 FIFO模式,通过与93LC56存储芯片相连,将FT232HL配置为FT245 FIFO模式的信息存储于芯片中。  AX7050 USB部分原理图 AX7050 USB部分原理图 AX7035 USB部分原理图 AX7035 USB部分原理图2.3 FT245 FIFO接口引脚 如下表所示为FT245 FIFO接口,ADBUS为并行接口,供FPGA使用,RXF#,TXE#为FT232H输出信号,用于通知FPGA是否可读可写,RD#,WR#为读写输入信号,由FPGA控制,CLKOUT为输出时钟60MHz,OE#为输出全能,需要在RD#有效之前至少提前一个时钟周期。  2.4 FT245 FIFO时序 下图为FT245 FIFO模式时序图,读时序中,首先FT232H将RXF#拉低,此时可以读取FIFO里的数据,FPGA可将OE#先拉低,过至少一个时钟周期,再将RD#拉低,在CLKOUT上升沿采集数据;写时序中,FT232H将TXE#拉低,表示现在可写,FPGA可将WR#拉低,在CLKOUT上升沿写入数据。  3. 程序设计 3. 程序设计程序设计比较简单,功能实现为将从FT232H的读FIFO中读取的数据存储到双口RAM中,再将数据从RAM读取出来发送到FT232H的写FIFO中,实现数据的环通。代码实现根据前面所讲的时序图,实现其功能即可。  代码中采用了简单的状态机,首先在IDLE状态下判断ft_rxf_n信号是否是0,如果是0,进入READ状态,开始读取FT232H的数据,并存入RAM中,如果ft_rxf_n拉高,进入IDLE状态;否则判断ft_txe_n是否为0并且RAM空间不为空,进入WRITE状态,将RAM数据写入FT232H,如果ft_txe_n拉高或者RAM空了,进入IDLE状态。 | 引脚名称 | 功能描述 | | ft_clk | FT232H时钟,CLKOUT频率60MHz | | rst | 复位信号,高电平有效 | | ft_rxf_n | RXF# FT232H FIFO可以读,低电平有效 | | ft_txe_n | TXE# FT232H FIFO可以写,低电平有效 | | ft_oe_n | OE# 输出使能,低电平有效 | | ft_rd_n | RD# 读信号,低电平有效 | | ft_wr_n | WR#写信号,低电平有效 | | ft_data | FT232H数据端口,8位位宽,双向IO |

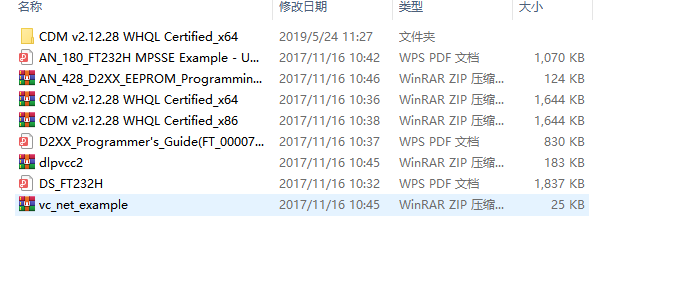

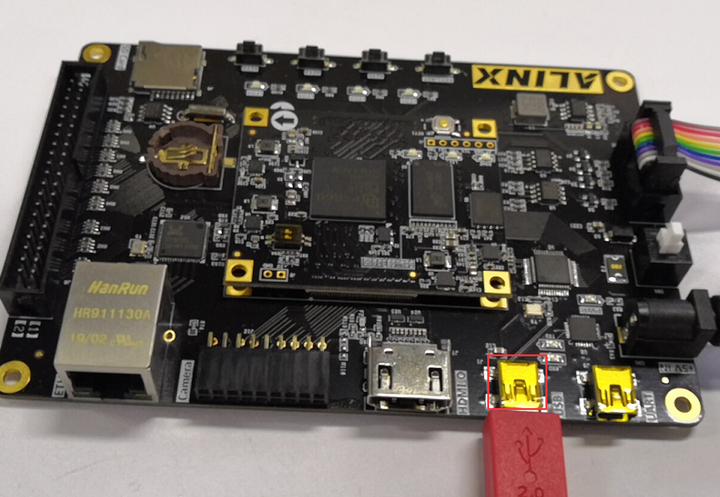

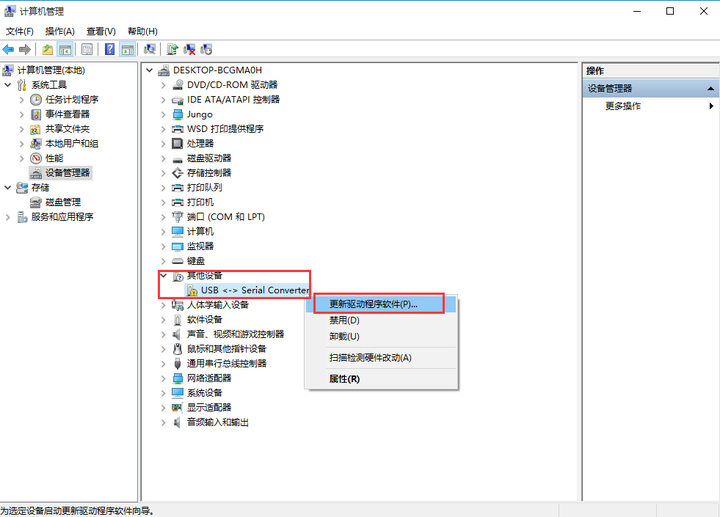

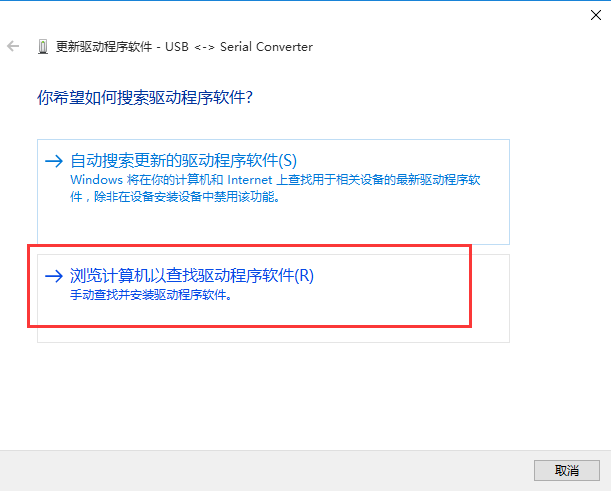

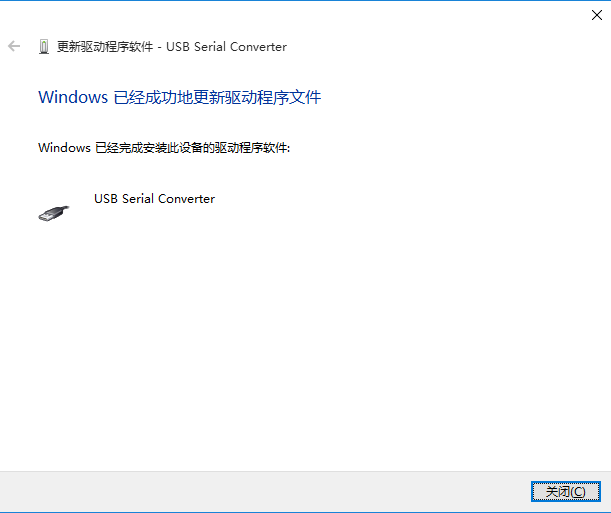

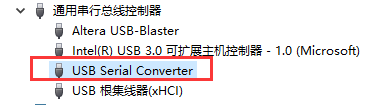

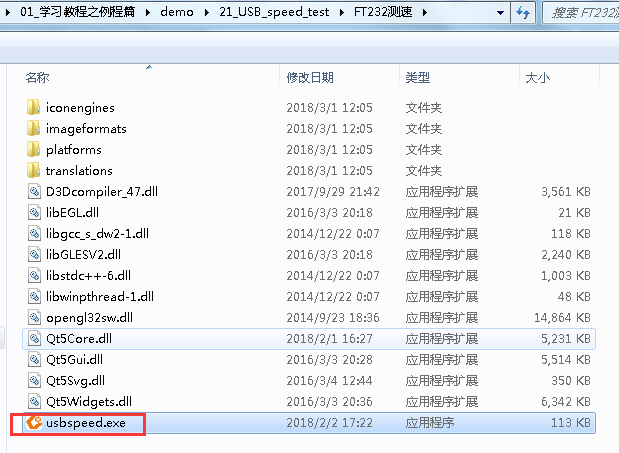

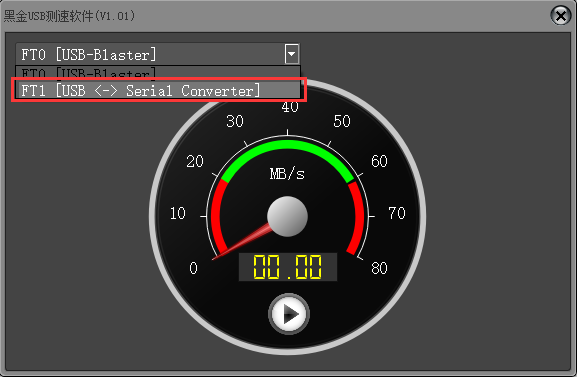

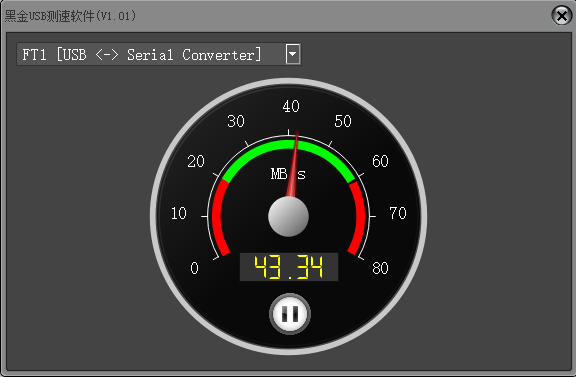

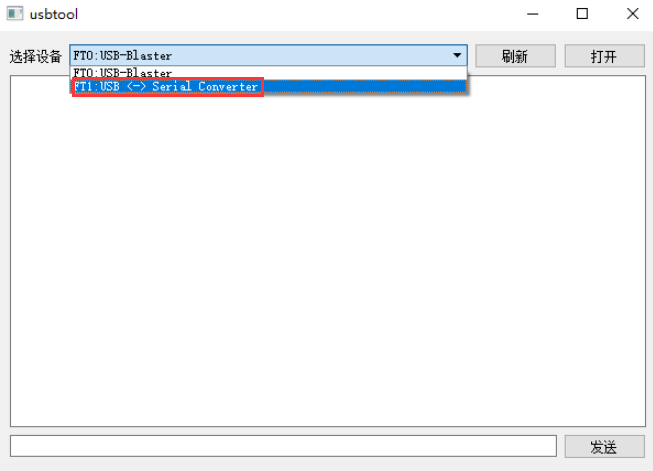

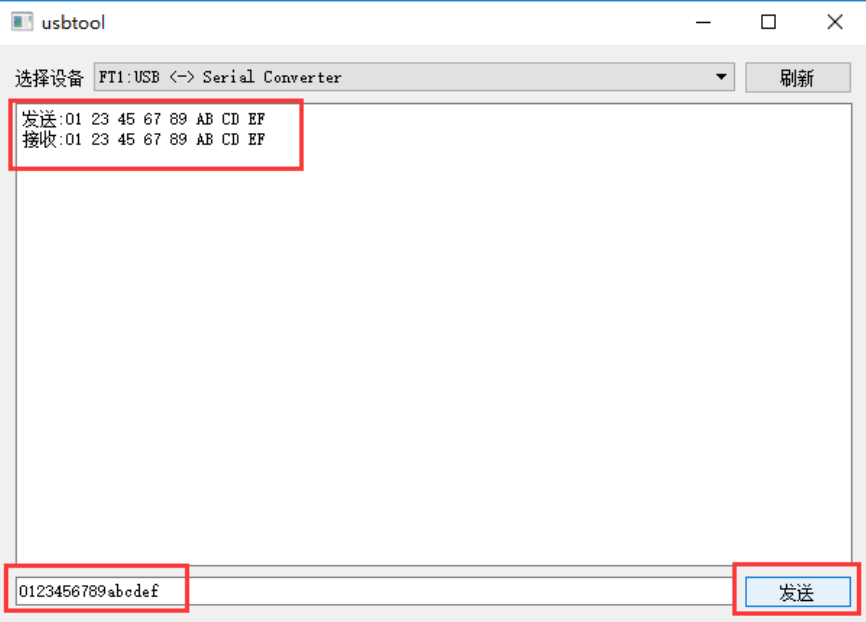

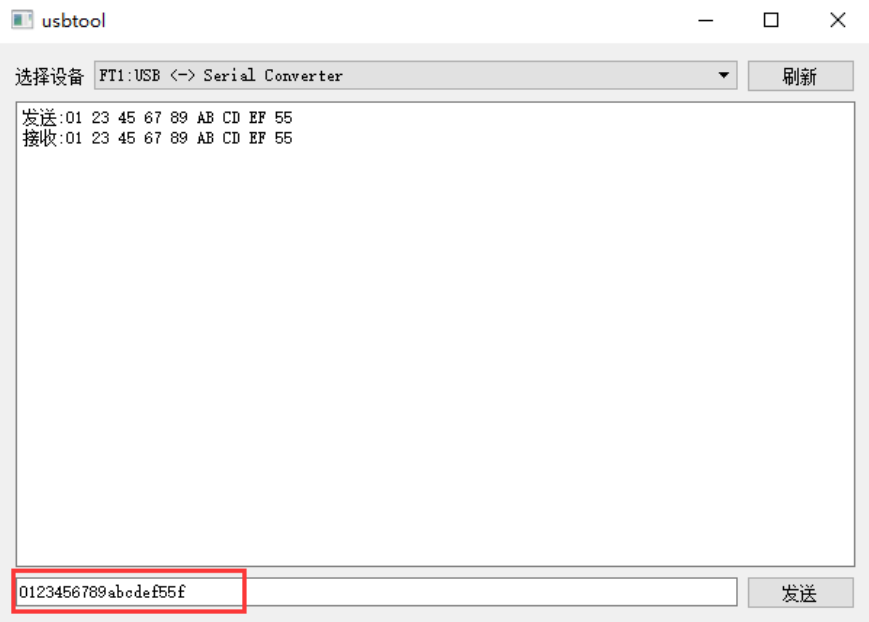

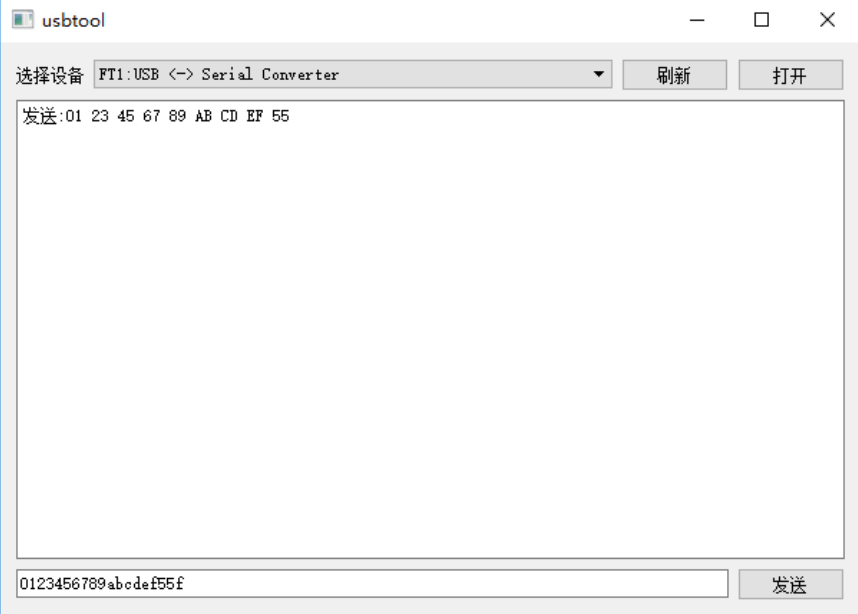

4. 实验流程4.1 安装FTDI D2xx driver 在05_芯片手册\ft232h文件夹中可以找到CDM v2.12.28 WHQL Certified_x64.zip,将其解压。  取出开发板,连接上开发板的USB接口,打开电源  打开设备管理器,出现新设备,右键点击更新驱动程序软件  点击浏览计算机以查找驱动程序软件  点击浏览找到解压的文件夹,点击确定,并点击下一步。 成功安装驱动后如下图:  可以看到出现 USB Serial Converter设备  4.2 实验现象 将程序下载到FPGA中,找到上位机测速软件,打开软件  选择USB设备,点击开始按钮  可以看到读写速度在40MB/s附近变动,点击暂停按钮可停止测速。  有些同学想要看看USB传输的数据,在这里我们提供 了“USB测试工具“,工具在下图中位置:  操作如下: 1)首先确保程序(与测速软件一致)已下载到FPGA中,连接好USB线,找到上位机测速软件并打开,在选择设备下拉框里找到USB 设备, 如果没有显示 USB 设备, 点击“刷新” 按钮 之后选择好设备, 点击“打开” 按钮。如下图:  2)在数据输入框输入十六进制数据, 再点击发送, 可以在显示窗口看到发送和接收的数据, 进行数据对比, 验证正确性。  在这里需要注意下:发送数据需要为偶数个,否则上位机会截取偶数个数据发送, 如下图, 最后一个数据 f 并没有发送出去。  3)“刷新” 按钮类似于关闭端口, 点击“刷新” 按钮后, 发送数据, 不会有反应, 需要点击

“打开” 按钮打开 USB 设备。  5. 总结 5. 总结本实验介绍了FT232H芯片FT245 FIFO模式的读写测速,大家可以结合各自的应用编写上位机程序实现所需功能。

|  /1

/1

/1

/1