|

原创声明: 本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处(http://www.alinx.com)。 适用于板卡型号: PGL22G/PGL12G 1. 实验简介本实验通过使用开源软件opencores上的I2C master控制器去控制I2C接口的EEPROM读写,练习如何有效的使用开源代码提升开发效率。 2. 实验原理2.1 硬件电路 在开发板上,FPGA芯片通过I2C总线连接EEPROM 24LC04, I2C的两根总线各上拉一个4.7K的电阻到3.3V,所以当总线上没有输出时会被拉高, 24LC04的写保护没有使能,不然FPGA会无法写入数据。因为在电路上A0~A2都为低,所以24LC04的设备地址为0xA0。

开发板部分电路 2.2 I2C的总线协议和时序 I2C标准速率为100kbit/s,快速模式400kbit/s,支持多机通讯, 支持多主控模块,但同一时刻只允许有一个主控。由数据线SDA和时钟SCL构成串行总线; 每个电路和模块都有唯一的地址。 在这里以AT24C04为例说明I2C读写的基本操作和时序,I2C设备的操作可分为写单个存储字节,写多个存储字节,读单个存储字节和读多个存储字节。各个操作如下图所示。

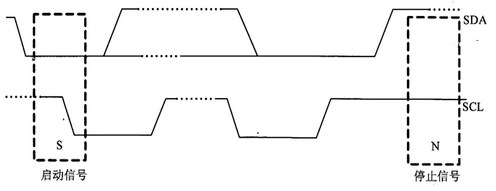

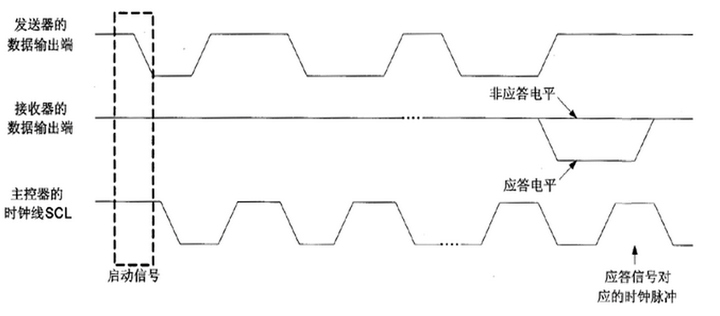

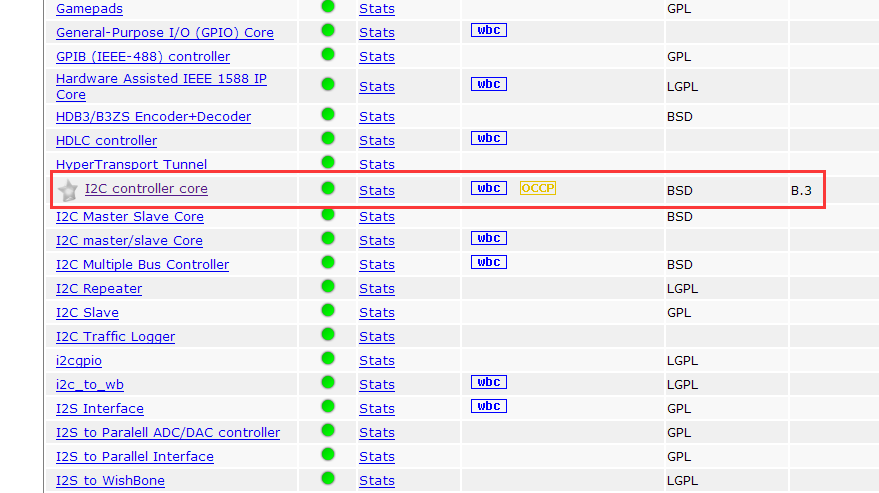

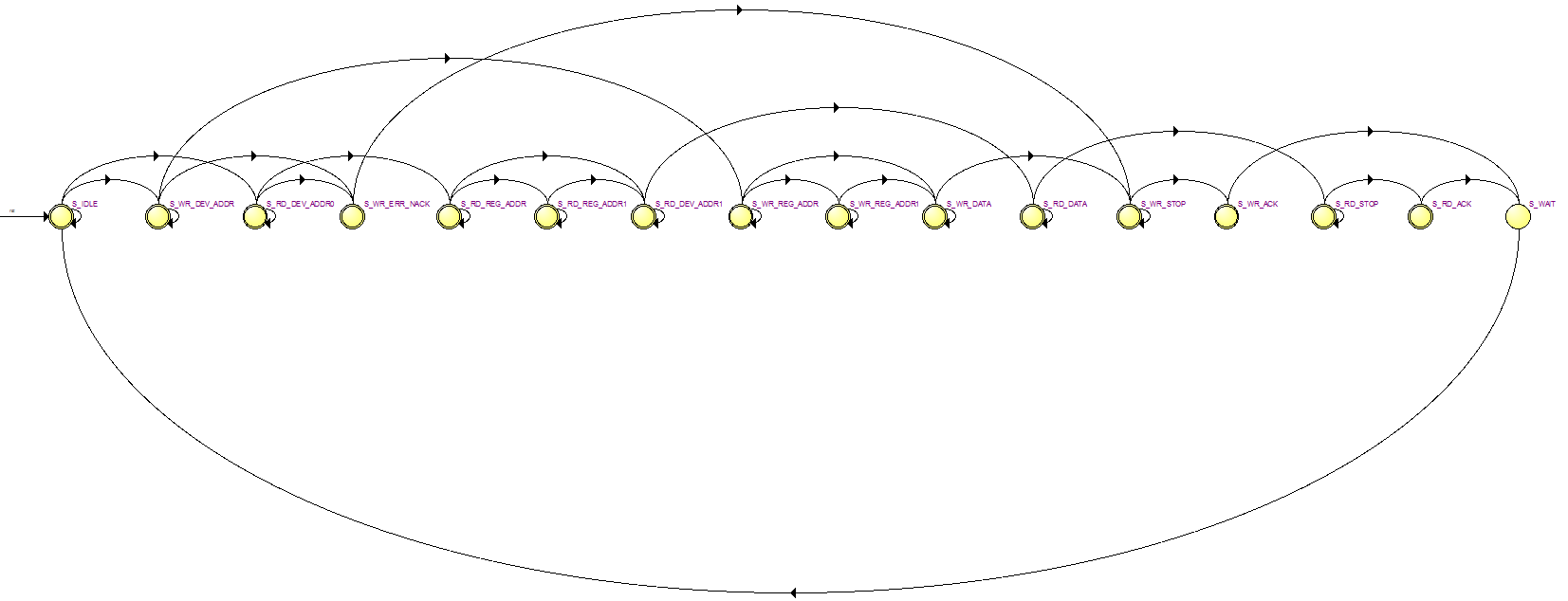

下面对I2C总线通信过程中出现的几种信号状态和时序进行分析。 ①总线空闲状态 I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。 ②启动信号(Start) 在时钟线SCL保持高电平期间,数据线SDA上的电平被拉低(即负跳变),定义为I2C总线总线的启动信号,它标志着一次数据传输的开始。启动信号是由主控器主动建立的,在建立该信号之前I2C总线必须处于空闲状态,如下图所示。  ③停止信号(Stop) 在时钟线SCL保持高电平期间,数据线SDA被释放,使得SDA返回高电平(即正跳变),称为I2C总线的停止信号,它标志着一次数据传输的终止。停止信号也是由主控器主动建立的,建立该信号之后,I2C总线将返回空闲状态。 ④数据位传送 在I2C总线上传送的每一位数据都有一个时钟脉冲相对应(或同步控制),即在SCL串行时钟的配合下,在SDA上逐位地串行传送每一位数据。进行数据传送时,在SCL呈现高电平期间,SDA上的电平必须保持稳定,低电平为数据0,高电平为数据1。只有在SCL为低电平期间,才允许SDA上的电平改变状态。 ⑤应答信号(ACK和NACK) I2C总线上的所有数据都是以8位字节传送的,发送器每发送一个字节,就在时钟脉冲9期间释放数据线,由接收器反馈一个应答信号。应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节; 应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将SDA线拉低,并且确保在该时钟的高电平期间为稳定的低电平。 如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送器结束数据发送,并释放SDA线,以便主控接收器发送一个停止信号。  3. 程序设计 3. 程序设计I2C时序虽然简单,但是写的不好也会出现很多问题,在开源网站http://opencores.org/上我们可以找到很多非常好的代码,这些代码大部分都提供详细的文档和仿真。俗话说,他山之石,可以攻玉,恰当的使用开源代码,不光能提升我们的开发效率,也能学习别人的开发思路。由于代码大部分都是经过很长时间反复修改,反复精炼后的,所以有些代码理解起来可能比较困难,在不能很好的理解别人代码的时候,最好的办法就是仿真。  从IP core文档得知,i2c_master_byte_ctrl模块主要完成一个字节的读写,我们只需要按照I2C读写的要求,完成设备地址、寄存器地址、数据等读写即可。 i2c_master_top模块是对i2c_master_byte_ctrl模块的再次封装,完成一个寄存器的读写,由于不同的设备寄存器可能是8bit,也可能是16bit,这里i2c_addr_2byte信号来控制寄存器地址是8位还是16位。 i2c_master_top模块状态机,如果是写寄存器操作,先写一个字节设备地址(写操作),再写1个字节或2个字节的寄存器地址,再写一个字节的数据;如果是读操作,先写一个字节的设备地址(写操作),再写1个字节或2字节的寄存器地址,完成地址的写入,再次写设备地址(读操作),然后读取一个字节的数据。不管怎么说,程序设计都是要满足芯片时序要求的,所以在阅读程序之前最好先把芯片的数据手册仔细阅读一遍。  i2c_master_top状态机 | 信号名称 | 方向 | 说明 | | clk | in | 时钟输入 | | rst | in | 异步复位输入,高复位 | | clk_div_cnt | in | I2C时钟分频因子,等于系统时钟频率/(5 * I2C时钟频率) - 1。例如50Mhz系统时钟,100Khz的I2C,配置为99,400Khz的I2C,配置为24。 | | scl_pad_i | in | I2C时钟数据输入,本实验可忽略 | | scl_pad_o | out | I2C时钟输出 | | scl_padoen_o | out | I2C时钟输出使能,低有效,I2C外部有上拉电阻,如果输出高阻态,则会被拉到高电平,在本实验中,高电平输出时输出高阻 | | sda_pad_i | in | I2C数据输入 | | sda_pad_o | out | I2C数据输出 | | sda_padoen_o | out | I2C数据输出使能,低有效。在本实验中,高电平输出时输出高阻。 | | i2c_addr_2byte | in | 寄存器地址是8位还是16位,1:16位,0:8位 | | i2c_read_req | in | I2C寄存器读请求 | | i2c_read_req_ack | out | I2C寄存器读请求应答 | | i2c_write_req | in | I2C寄存器写请求 | | i2c_write_req_ack | out | I2C寄存器写请求应答 | | i2c_slave_dev_addr | in | I2C设备地址,8bit,最低位忽略,有效数据位是高7位。 | | i2c_slave_reg_addr | in | 寄存器地址,8位地址时,低8位有效 | | i2c_write_data | in | 写寄存器数据 | | i2c_read_data | out | 读寄存器数据 | | error | out | 设备无应答错误 |

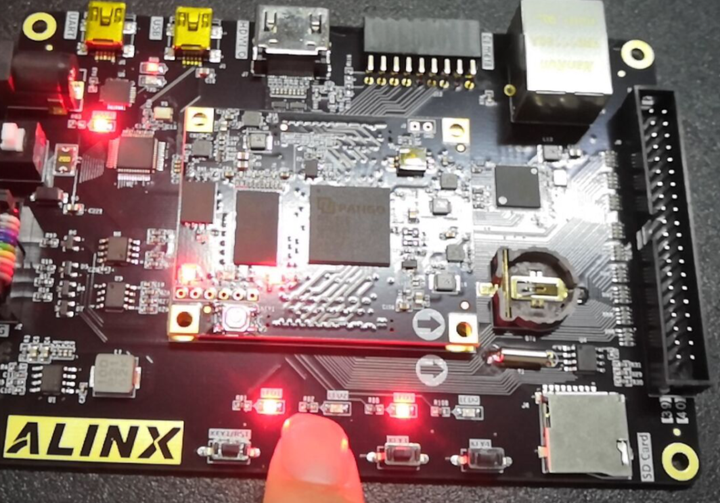

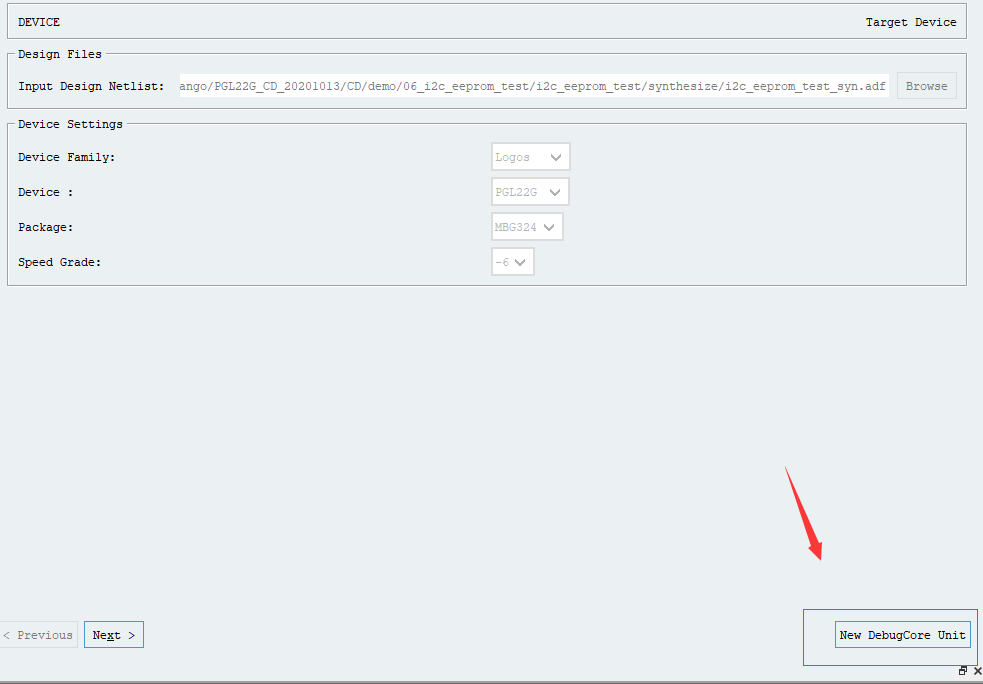

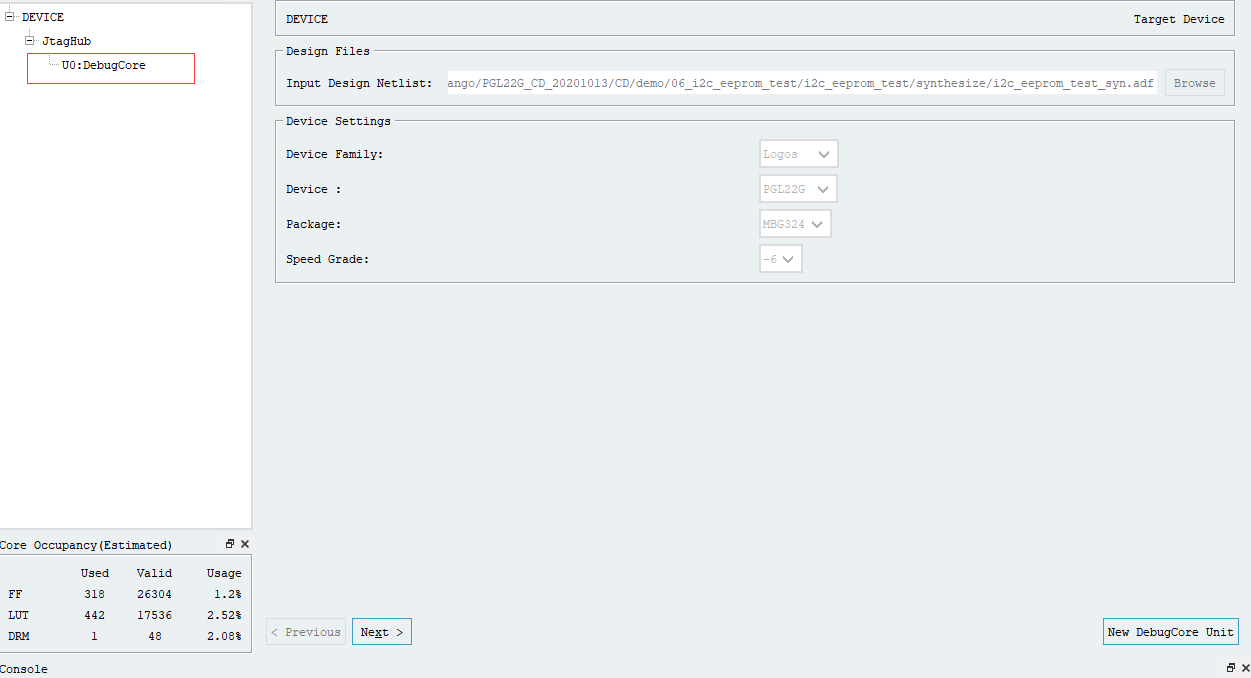

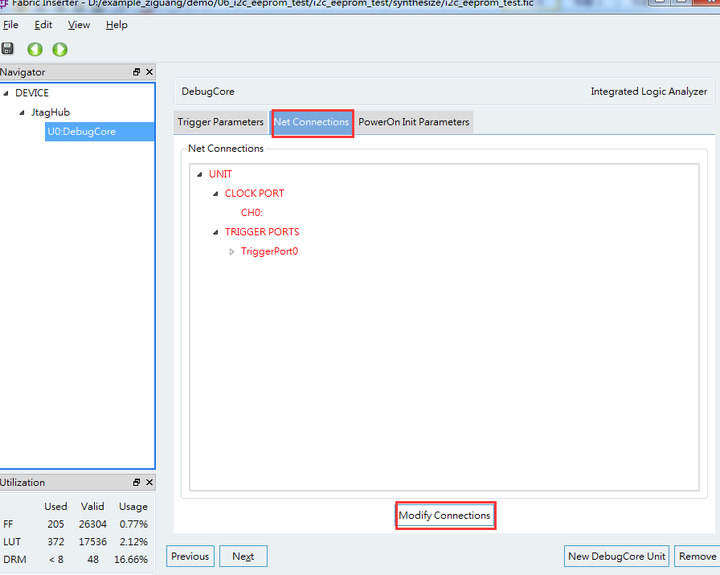

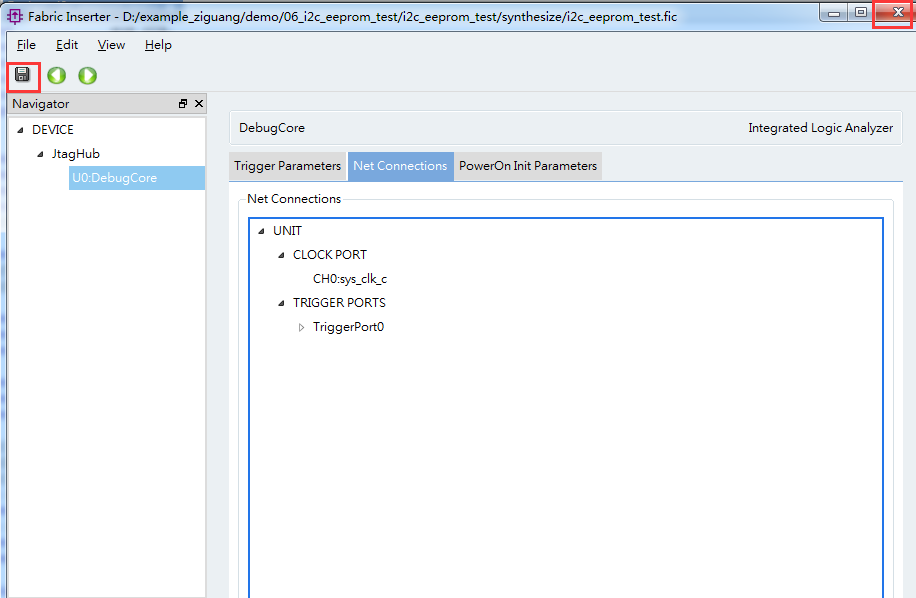

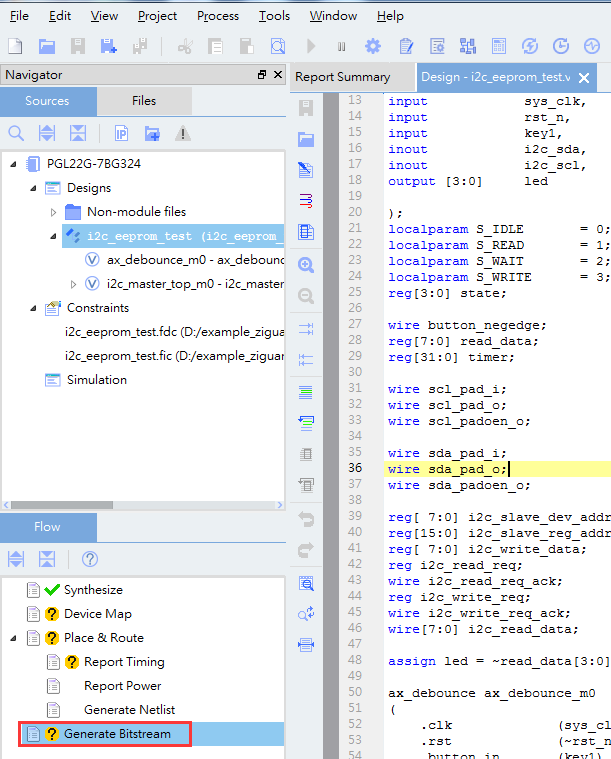

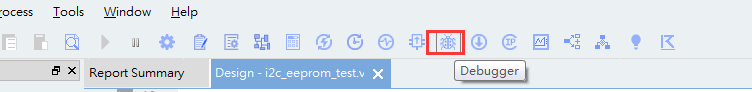

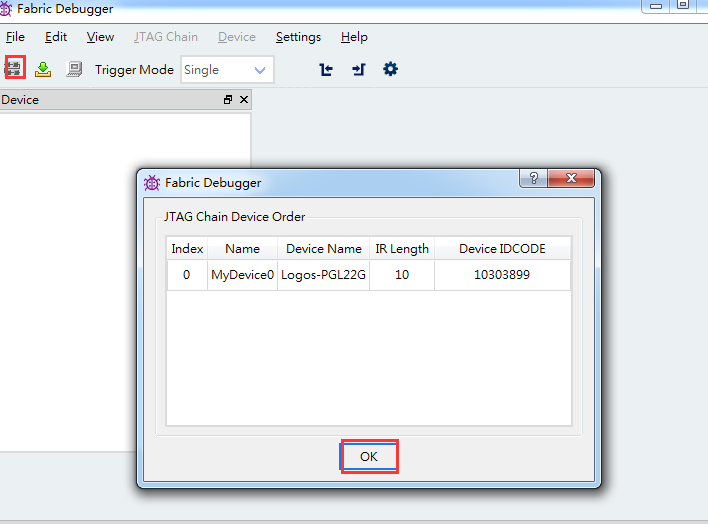

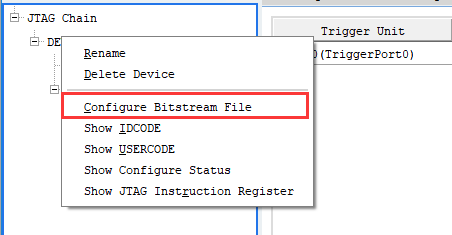

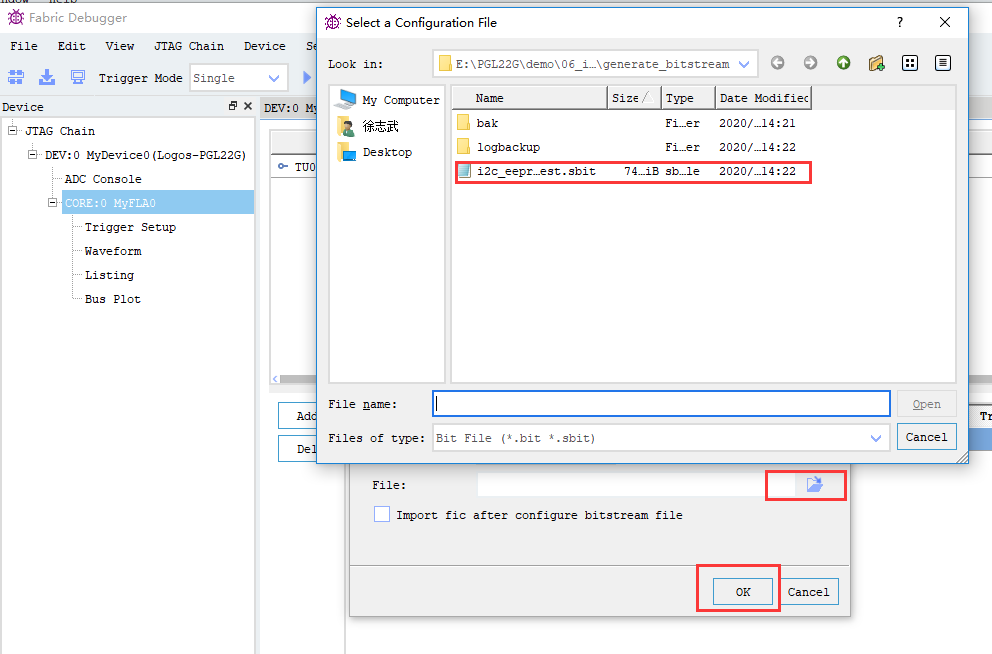

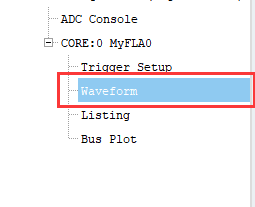

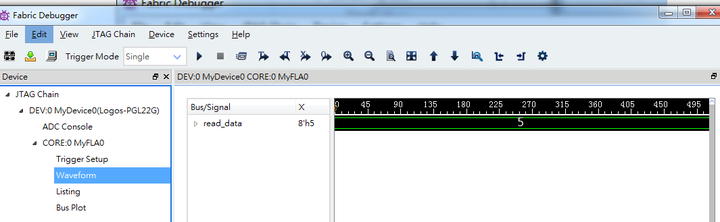

i2c_master_top模块端口 i2c_eeprom_test模块完成EEPROM的读写,EEPROM设备地址是A0,程序中将地址00的数据读出,然后通过LED显示,在KEY2 按下时,数字加一并再次写入EEPROM并显示出来。在I2C控制器中,代码的大部分功能在备注中也有很多批注。 4. 实验现象下载实验程序后,可以看到LED显示一个二进制数字,这个数字是存储在EEPROM中00地址的数据,数据是随机的,这个时候按键KEY2按下,数字加一,并写入了EEPROM,再次下载程序,可以看到直接显示更新后的数据。  5. 使用在线调试Fabric Debugger观察信号 5. 使用在线调试Fabric Debugger观察信号使用Fabric Debugger可以非常直观的看到程序在开发板上运行时各个信号的变化,在本例程中添加一个Debug Core来观察程序运行时各数据线的变化情况。 按红色标记,在单击“Inserter":  在弹出如下界面下选择New DebugCore Unit来新建一个Debug Core:  单击U0:DebugCore:  会跳到参数设置界面,在"Trigger Parameters"栏中Sample Depth采样深度自己根据需求选择,这里选择默认,其它的设置保持不变。  在"Net Connections"栏中选择Modify Connections,进行Net修改;  弹出的界面中首先对TriggerPort栏中观测信号关联,在这里,选择左侧read_data,然后单击Make Connections,可以在TriggerPort栏中看到关联的观测信号read_data;  以同样的方式对Clock栏中时钟信号关联,选择左侧sys_clk_c,然后单击Make Connections,可以在Clock栏中看到关联的观测信号sys_clk_c,然后单击OK;  再在如下界面中单击保存按钮进行保存并关闭即可。  接下来重新生成.sbit文件,双击Generate Bitstream,会生成带有在线调试的DebugCore。  上面的工作准备好后,接下来才是正式开始调试, 单击Debugger(确保开发板上电并连接了下载器),  单击JTAG 扫描按钮,在找到后单击OK;  右击DEV:0MyDevice0,在下拉菜单中单击Configure Bitstream File  再按如下图中进行设置,设置完成后按OK键;  到此,程序已下载到FPGA 中,可以在线观察所需要的信号,选择 Waveform,选择触发模式为连续,并单击run;   可以看到read_data数据,每按一次KEY2键运行一次可以看到数据增加1。

|  /3

/3

/3

/3