模数转换器 (ADC) 是在高速、高分辨率应用中通过数字形式处理、存储、传输模拟或射频信号的关键元器件。ADC 性能要求随应用而异,包括分辨率、动态范围、线性度、功耗、速度、带宽、SNDR(信号与噪声加失真比)和 ENOB(有效位数)。 遵照性能规范验证 ADC 功能时,设计人员面临着诸多挑战。将连续的模拟信号转换成离散的数字编码时,由于量化噪声,不可避免地会产生逼近误差,设计人员可以通过选择最适合其应用的架构来使误差最小化。在纳米技术节点中,器件噪声、布线后寄生效应、工艺变化和器件失配也会严重影响 ADC 性能。

Analog FastSPICE Platform 全电路 ADC 验证模数转换器 (ADC) 是在高速、高分辨率应用中通过数字形式处理、存储、传输模拟或射频信号的关键元器件。ADC 性能要求随应用而异,包括分辨率、动态范围、线性度、功耗、速度、带宽、SNDR(信号与噪声加失真比)和 ENOB(有效位数)。遵照性能规范验证 ADC 功能时,设计人员面临着诸多挑战。将连续的模拟信号转换成离散的数字编码时,由于量化噪声,不可避免地会产生逼近误差,设计人员可以通过选择最适合其应用的架构来使误差最小化。在纳米技术节点中,器件噪声、布线后寄生效应、工艺变化和器件失配也会严重影响 ADC 性能。

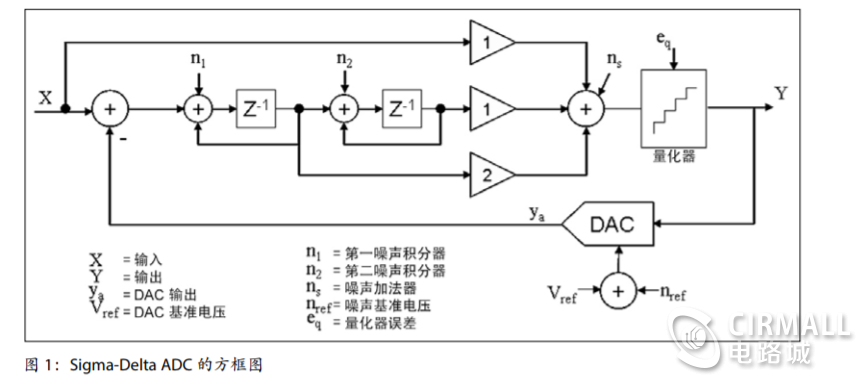

务必要在进行芯片加工之前,以纳米 SPICE 精度验证 ADC 的主要性能指标。也就是说,要在晶体管级别执行全电路验证,以弄清架构限制、器件噪声、布线后寄生效应、工艺变化和器件失配引起的性能降低情况。由于传统 SPICE 和 RF 仿真器的性能和容量限制,在晶体管级别执行全电路 ADC 验证非常具有挑战性,甚至无法实现,设计人员不得不求助于模块级验证方法。这种方法是将 ADC 拆分为多个周期模块,对各个模块(积分器、量化器等)进行周期噪声分析 (PSS-Pnoise),然后手动合并结果以估计整体噪声。模块级验证需要设计人员拥有大量的设计专业知识、采用多个步骤和高风险的近似计算,而且无法保障所得结果的精度。利用 AFS Platform,设计人员无需再依赖模块级方法,而是可以在晶体管级别以纳米 SPICE 精度验证全电路 ADC。AFS 全电路 ADC 验证包括随机器件噪声的影响以及量化噪声等架构特征。此外,设计人员可以纳入布线后寄生效应,并表征电路的工艺变化和器件失配。使用 AFS WaveCrave Calculator Pad 进行的自动后处理,会利用快速傅里叶变换法 (FFT) 将时域结果转换为频域中的功率谱密度 (PSD),并计算 SNDR 和其他指标。下页的 sigma-delta ADC 的 PSD 图说明了在 ADC 验证期间考虑器件噪声的重要性。传统瞬态仿真(无器件噪声)在噪声基底估算方面的误差高达 25dB,而 AFS 瞬态噪声的结果与硅片测量具有极佳的相关性。[1]

/4

/4

/4

/4